- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

简化消费类应用DDR存储器电源设计,降低嵌入式设备开发成本

不论是采用分立元件系统还是高度集成的系统级芯片(SoC),许多嵌入式消费电子系统都利用了现有系统(如PC或其它成熟的通用系统)的架构。这些嵌入式系统(或子系统)通常不存在对奢侈的灵活性扩展的需求,甚至也不需要PC类系统设计所要求的全部资源。

在将某个系统参考设计修改成适用于特定的嵌入式系统或消费电子应用时,去除参考设计中不需要的模块或功能可以大量节省成本。但通过有创造性地对被推荐供电元件进行优化来减少过多的能力可以节省大量成本,而且不会降低任何性能或功能指标。

双数据速率(DDR)存储器目前成为所有新型PC和笔记本电脑的标准配置,由此带来的结果是,其价格现在已经下降到同档次SDRAM之下。这使得机顶盒、个人录像机和显示器/电视等消费类产品的设计者已在使用DDR存储器设计新型系统。

通常,消费产品所要求的存储器数量比计算机少得多,所以,2.5V的Vddq和1.25V的Vtt所需的电流要低得多。这使得单个DDR功率IC不仅可以为DDR存储器提供电流,而且也可以为内核SoC电压提供电流。California Micro Devices(CMD)公司就可提供此类IC,其中包括CM3121(实现完整单芯片DDR供电)、CM3132(为Vddq提供1A、为Vtt提供0.5A、为Vcore提供1.5A)等。所需要的唯一外部元件是输出电容。

折衷考虑开关和线性架构

一个参考设计最初可能是持采用昂贵的开关调节器供电的1,024MB、256位DDR存储器。但是,目标应用可能只需要焊接到PCB上的6 MB、128位存储器。这或许会将对持双列直插式存储器模块组(DIMM)插槽中多达16个DDR模块的需求降低到2或4个模块,系统设计者可以更严格地控制相应的供应商和指标规格。另外,在这种情况下,设计者可以通过优化供电电源架构显著降低成本。

不论采用哪种拓扑结构,同线性调节器相比,开关调节器通常需要更多的功率器件(是线性调节器的两倍)并需要电感等更昂贵、体积很大的元件和更大的旁路电容。这种复杂性和成本上的增加是为在负载较高时耗散更低所付出的代价。但在负载较低的情况下,将成本或空间降低50%或更多要比将耗散减少10%更为重要,此时,线性调节器是一种简单而精确的选择。

在下面例子中,一种成本得到优化的参考设计可以大幅降低成本、缩小电路板空间并可带来其它好处。由于元件数量较少并可以把通过型(pass)场效应晶体管(FET)直接放在负载附近,布线进一步得到简化。(对于开关调节器来说,等同的“通过元件”需要两个FET和一个大电感。)

当然,线性设计首要折衷因素是功率耗散。通过元件必须“烧掉”没有被负载耗散的所有能量。然而,在许多应用中,“高效率”开关调节器对给定负载来可能说尺寸过大,低耗散的优点可能很容易就被其它缺点抵消了。

为了在线性调节器中将功率耗散减至最低并使效率达到最高,可通过为调节器输入端选择尽可能低的供电电压来尽量减小输出通过型晶体管的电压降。例如,在PC环境中,传统标准限制了可使用的主要电源轨(12V、5V和3.3V)。在其它应用中,主要电源轨可以按照需要进行更准确地定制,但成本保持不变。

例如,如果一个嵌入式系统的系统逻辑部分只要求2.8V主电源轨,那么在这块板上任何地方都没有理由使用3.3V的电源轨。这增强了使用线性DDR-I调节器的应用前景,因为300mV压降((VIN=2.8V)-(VOUT=2.5V))功率耗散比800mV压降((VIN=3.3V)-(VOUT=2.5V))的耗散小得多。如果可能,人们希望选择较低的中间电压,但必须把调节器的“压差”检测出来。“压差”指VIN和VOUT之间的最小电压差,在这个电压下,调节器依然可以有效地把输出控制在指标要求之内。)。

低压差(LDO)调节器可以把压差降低到几百毫伏以下。依靠LDO的低压差特性,线性调节器的效率常常可以逼近甚至超过开关调节器的效率。

将开关系统重新设计成线性LDO拓扑可以将元件数减少到只包含一个简单调节器、一个通过FET元件、一个输出负载电容,从而获得前述的各种好处。

高集成度电源架构优化方案

为了实现更高度的集成,设计者可以像CMD公司所做的那样将整个线性DDR电源(包括通过FET和控制器逻辑)集成到单个Power-SOIC封装中。

CMD公司的CM3121集成了两个低电压LDO调节器和一个源-汇(source-sink)线性调节器,以便为 DRAM 或存储器内核逻辑提供2,000mA VDDQ和为DDR或其它SSTL端接电压提供500mA VTT。

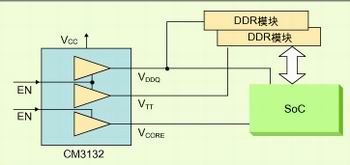

CM3132集成了两个低电压LDO调节器和一个source-sink线性调节器,以便为 DRAM 或存储器内核逻辑提供1,500mA VDDQ及为DDR或其它SSTL端接电压提供500mA VTT,还可为SoC或诸如千兆位以太网等外围内核提供1,500mA VCORE。图1是一个典型应用框图。

PSOP-8封装的占位与开关调节器的一个功率电感几乎相同,但却可以替代整个SoC电源。由于尺寸小,设计工程师可以把该芯片与参考设计并行排列,并可以在成本更低的生产配置中(可能并不需要原有电源的全部容量)对它的性能进行测试。

如前描述,要把电压较低的VIN分配给在电流汇总点的各个LDO,主要的设计工作是把用于互不关联系统的多个竞争开关调节器整合到PCB上单个“中间VDD”扩散平面。这种开关/线性组合能折衷两种拓扑的效率,并可以同时节省成本和电路板空间。

复杂参考设计包含一些关键电路,对这些电路进行改动或重新设计可能存在风险。但在电源部分存在很多机会,可以在不牺牲功能或破坏规范的情况下进行创造性优化和实现具有竞争力的个性化设计。

走向成功的步骤

首先,降低成本过程应从各个相关的参考设计或某个早期的原型的完全设备化开始。保守的纸面设计方法几乎必然导致系统电源容量过剩进而对DDR供电电源带来额外的成本。接口速度、宽度、模块密度和软件要求可以极大地影响最大功率需求。在必须适应各种DIMM配置的全功能PC设计中,无数的不确定性可能要求系统具有很高的安全裕度。但在存储器模块被焊接到电路板上的嵌入式简化系统(如视频卡)中,或在选择范围受限的封闭盒系统(如机顶盒)中,设计者可以牺牲一些灵活性以节省成本。

针对你的实际(或近似)系统的不同配置来测量在VDDQ和VTT上的实际动态负载并观察这些系统的实际要求,而不是做出各种假设或给出极为保守的性能裕度。以改动一个设计或降低成本为目的工程师可能倾向于依据原有系统来决定自己的要求。然而,不改变可能还是会给你的设计引入不必要的成本或使它的成本效益低于要求。

基于许多相同的理由,向系统中引入安培表是不能接受的,这使得无法从评估板连线到现有的系统。简单地把直流安培表接入系统中会产生误导和各种问题。首先,它引入了寄生电容,这可能会干扰关键的VDDQ和VTT节点的调节;其次,大多数高电流测试设备会引入可察觉的IR压降。感应环测量是直流安培表的一种替代方案,可以显示精确的瞬时峰值,但不能显示出直流负载。

有几种基于霍尔效应的感应测量设备可以读出直流和交流电流,并可以产生能在示波器上观察的精确缓冲输出。LEM元件LTS串联电流探针被校准以输出给定的每安培几个毫伏,并可以通过感应环准确地测出数十安培的电流。考虑了要易于中断VDDQ和VTT电源平面的PCB布局可以对在实验室中分析该系统实际电流要求带来方便。

另一个保持线性调节器节省成本潜力且还可以降低相关成本的方案是布局双占位的“备份方案”。在这种方案中,设计者按照现有的设计或参考设计(开关型或其它)进行布局,但需包含前述集成器件的占位,从而使得可以把它与原始方案并行地进行评估。通过组装两个等价的电路板,一个采用老方案,一个采用高度集成方案,由于所有变量相等,可以同时对两者的性能进行评估。这能可靠而快速地确定设计的可信度。

由于这些集成器件体积很小(通常比单个FET封装小),这种方法牺牲的PCB面积可以忽略不计。

一旦你最终确定了目标,你就很容易确定适合于该设计的折衷水平。在一些情况下,双占位策略可以用于在相同PCB上构建成本更低、功能更少的设备。不论何种情况,线性调节器和开关调节器之间的折衷都可以通过这里描述的新型集成器件得到增强。鉴于这些新方案在减小尺寸和降低成本方面的巨大优势,我们有必要重新认识在存储器子系统应用中线性电源和开关电源之间的折衷问题。

作者:Jeffrey Dunnihoo

高级应用工程师

California Micro Devices

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...