- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

采用6 Sigma方法降低便携式产品的功耗

本文将把6 Sigma方法用于手机功耗控制,并探讨如何采用这种最佳功率实现方法使便携式产品达到更小的尺寸和最佳的功率指标。

无线设计工程师目前所面对的最关键需求之一是降低新型便携式产品的功耗。无论是具有GPS(全球定位系统)功能的手机还是可上网的手表,便携式产品市场对增强产品的功能、减小产品尺寸的要求从未间断过。我们面临着延长电池寿命、降低系统电压、减低微处理器的速度和更合理有效地分配功率等方面的挑战。

6 Sigma方法将商业、统计和工程学的理论融于一体,强调通过基本的工艺技术剔除产品缺陷。通过严格采用6 Sigma方法,业界在新型无线技术方面将取得长足的进步。本文将把6 Sigma方法用于手机功耗控制,并探讨如何采用这种最佳功率实现方法使便携式产品达到更小的尺寸和功率指标。通过对商业和市场趋势以及统计和工程学的综合分析,我们将形成一种清晰的可降低便携式产品功耗的方法。

便携无线业务和市场趋势

无线产品的功能要求越来越多,并且还增加了对于产品便携性、功率,亦即电池寿命的要求。而推动市场销售的各种应用都要求增加带宽,但它们势必也会增加电池的耗电量。在2001年九月《战略分析在线》上,题为《美国蜂窝设备市场动态》的文章指出:购买新型移动电话的消费者中有24%是为了获得更好的功能。数码相机、蓝牙功能和多媒体终端都对开发商利润增长起到正面影响。根据这份报告,推动人们换购新型手机的决定性因素是电池性能和产品价格。

人们对于高带宽传输的需求是不言而喻的。很多公司都在积极地为各种无线应用开发能提供高带宽、优良信号质量的解决方案,无论它们是蓝牙、802.11b,或者是GSM、CDMA、W-CDMA和TDMA。但是,无线技术在2001年发展迟缓表明,无线技术缺乏吸引人的应用和服务内容。目前很多公司都加入了在便携产品中集成一系列功能的竞争,无论胜出的应用将是彩色显示屏、移动互联网、蓝牙功能、MP3、数码相机(DSC)、PIM功能、GPS、单板游戏,还是多媒体功能,产品开发商必须注意以下两点:第一,人们要求带宽更高、可靠性更强、避免诸如噪声和通话延迟等RF问题;第二,手持设备自身的特点决定了它必须自带电源,并能支持即将出现的各种新功能。改进电源管理和分配功能,并重新关注功耗最小化将成为促进市场拓展的关键因素。

关键功能的功耗和用户使用模式的统计模型

要提高产品的便携性和电池寿命就需要综合了解无线设备每项功能的功耗,并对消费者使用便携产品的模式进行统计。过去,手机大都处于发射模式、待机模式或关机模式。但是,即将到来的2.5G和3G产品带宽的提高和持续小型化的趋势将使其集成更多的数字功能,从而产生计算模式。为了能更好地理解不同功能所需的功率,我们测量了MP3、数字蜂窝电话、数码相机、PDA和手持GPS在休眠模式或待机模式下的瞬时待机功率以及正常工作时的功率。结果如表1所示。

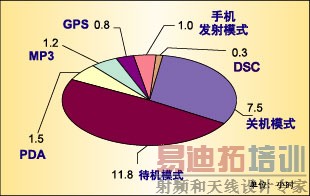

为了使表1中所列无线设备的电池寿命最大化,我们需要了解每项功能使用的频繁程度。考察24小时周期范围内每分钟采样测得的瞬时功率的分布,可以得到对于某一给定统计对象的功耗模式的统计模型。例如,假定某个用户在睡觉时会关机7.5小时,一天实际通话1.0小时,使用DSC、MP3、PDA和GPS的计算模式分别为0.3小时、 1.2小时、1.5小时和0.8小时,手机在余下的11.8小时处于待机或休眠模式。每项功能使用时间的饼图如图1所示。

1.2小时、1.5小时和0.8小时,手机在余下的11.8小时处于待机或休眠模式。每项功能使用时间的饼图如图1所示。

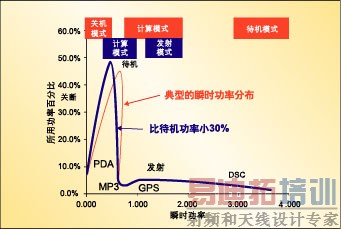

瞬时功率的分布如图2所示,对曲线下的面积求积分可得到总功耗。由于无线设备大部分时间处于待机模式,降低30%待机功耗会使24小时时间范围内该设备的总功耗大幅降低。

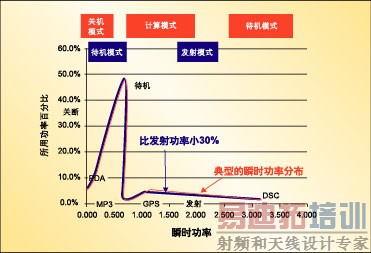

图3所示为发射功率降低30%时功耗的降低量。由于手机并非经常处于发射模式,因而节省的瓦特 小时数并不明显。

降低功耗的方法

对功率进行分类有助于集中注意力去找到降低功率所应采用的方法。共有三种功率分类,这三种类别分别是电源管理、电源分配和功率最小化。电源管理技术关注的是如何通过软件和硬件,例如看门狗定时器等使各个功能模块处于休眠模式或完全关机模式,促使图2中的瞬时功率分布压缩至最左边。电源分配技术关注的是如何分配和调节每个模块的功率,例如可根据DSC是否具有支持闪光灯所需的大电容,以及是否具有可浏览图像的改进型LCD,决定是否为其分配高达3.5W的功率。在给定的使用模式下,这项功能在一天24小时内的功耗可达0.92瓦特

小时。如果统计结果表明DSC使用的时间百分比数更高,那么这项功能就应该分配更多的电源,甚至为这项功能添加一块电池组的附件。

功率最小化技术关注的是如何降低待机、计算和发射等模式下的功率。该技术利用排列图分析方法来了解最主要的功耗的来源,然后通过采用标准工程技术来找到降低这项功耗的方法。这项技术的使用范例之一是标准逻辑门器件的采用,即在今天的手机中所采用的分立的“与”、“或”门。在设计中手机可能会用到5个以上独立的门电路,如果查看一下这些门在发射模式下的功耗,我们就会发现这些门所消耗的功率仅占总功耗的一小部分。利用图2和图3所示的统计建模方法,可以更清楚地看到需要大幅降低这些逻辑门的发射功率才能降低24小时内总的功耗。不过,在待机模式时,降低这5个独立逻辑门的功率就变得更为有效。

在上文所举的手机例子中,手机的待机功率为4,400微瓦,工作电压为4.0V。如果这5个分立逻辑器件也工作在此电压下,其ICC 将为20微安,那么这些器件将消耗400微瓦的功率,这意味着这些分立逻辑器件实际消耗功率为待机功率的9.0%。通过选用最新工艺、最低电压的分立逻辑产品对设计进行优化,可以使分立逻辑器件的待机功耗降低一半,或者是获得超过5%的待机功率的减小量。由于待机模式是最常使用的模式,降低5%的待机功率所带来的功耗节省是很可观的。

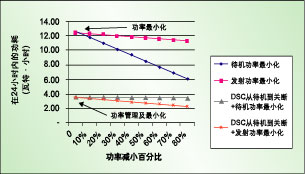

很明显,6 Sigma方法适合于手机功率最小化分析。在过去几年里,业界分析家都只关注于手机的电源管理技术,现在人们更关注图1中分布曲线的尾部,希望对功耗最小化作彻底的分析。功耗最小化关注如何降低待机模式、计算模式和发射模式的功耗,图2和3展示了最小化功率的优势所在。图4则显示了电源管理与功率最小化所能带来益处的一个比较。假定DSC 比其它功能消耗更多的功率,那么应该利用电源管理技术在使用DSC时开启此功能,而在不使用时完全关闭它。这项技术对于降低24小时内的瓦特 小时数可产生直接的影响,使其由14.6瓦特 小时降至6.7瓦特 小时。在电源管理发挥调节功能之后,发射功率的功率最小化将成为延长电池寿命最优先的考虑内容。

电源管理和分配已得到业界人士的广泛讨论和关注。但是,由于功率最小化是与加工工艺的变迁密切相关的,因此,在对上述论题进行讨论时,以功率最小化作为问题的焦点是必要的。

了解功率的分量

对于CMOS器件功耗的研究可发现如何进行电路板的布线、选择技术和设计电路才能延长电池的寿命。CMOS器件的总功耗是三个基本量的函数,这三个量是:静态或待机功耗、内部动态功耗和输出动态功耗。这些最重要的功率分量之和即为总功率,计算公式如下。其中,I CC 或I DD 为静态电源电流,V CC 或VDD 为电源电压,C PD 称为器件输出电容,CL 为器件驱动的负载电容,f 为工作频率。

PD总功耗 = PD待机功耗 + PD内部动态 + PD输出动态功耗

PD总功耗 = (I CC × VCC) + (Cpd ×f× VCC2) + (Cl×f× V CC 2)

在很多情况下,输出V CC 和频率与内部电压和频率相同,因而动态功耗可简化为下面的功耗方程:

PD总= (I CC × V CC ) + ((C PD +CL)×f× V CC 2)

优化功率分量

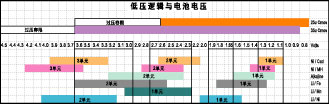

由以上方程可发现V CC 对于功率的影响很大。动态功率正比于V CC 的平方,而待机功率直接正比于V CC 。如今的CMOS技术可轻易地在V CC 为1V以下的条件工作。而现在的问题是无线设计仍然采用混合电压,并且要求4.6V的过压容限(OVT)。4.6V OVT的要求促使设计工程师选择0.35微米CMOS技术,这是由于0.25微米技术的栅极氧化物只能允许达到3.6V OVT。在便携式系统中,V CC 的选择还受到所选用电池的影响。如表2所示,0.35微米CMOS 技术是可适用于混合电压系统的最广泛的电池技术。

决定待机功率的另一因素是ICC。降低I CC 的关键在于工艺技术、尽量减少集成电路设计中所采用的逻辑门数量,并正确地匹配电路所需的内部驱动以缩短内部传播延迟。将手机的天线由高带宽的砷化镓(GaAs)天线改变为为基于微型机电装置(MEM)的开关,这样可以将手机的待机功率降到零。基于GaAs的天线开关存在静态I CC ,而基于MEM的开关静态功率则为零。但是,人们担心MEM技术不能通过蜂窝手机的跌落试验。

当无线设备处于计算或发射模式时,方程的动态功率部分变得至关重要,关键的因素是V CC 、频率、器件的输出电容C PD 以及布线和负载电容CL。前面已讨论过V CC 参数,可根据电池技术和系统所需的混合电压进行选择。器件的工作频率可根据预估的时序,在系统级或电路板级作出决策。显然,降低工作频率,如降低休眠模式的时钟将使功率降至最低。

下一个分量CPD是工艺技术和输出驱动的函数,工艺技术和输出驱动都正比于CMOS输出缓存的大小。如上文所述,通常由混合电压和电池技术决定V CC 的范围,然后根据栅极氧化物的限制确定工艺技术。在确定了正确的工艺技术后,下一步选择如何使输出驱动最小化,从而降低C PD 。所需的输出端口数(扇出系数)、每个单元负载的电容,以及所需的开关时间决定了需要的输出驱动。输出驱动最小化的关键,即降低C PD 的关键在于选择合适的产品,它要具备足够的驱动,能在预估的时序内切换负载。可使用方程I=C × dv/dt来进行计算,其中I 等于输出驱动电流,C 为电容负载,而dv/dt等于对应于给定负载的输出驱动电压的变换率。对于门电路或缓存等简单器件,内部传播延迟通常小于纳秒级。在这些器件中,大部分传播延迟由输出电压转换率决定。因此,如果需要在10纳秒的时间内使0V电压变换至3V,且该部件需驱动两个5 pF负载(总共10pF),则所需的驱动电流为2.4mA=10pF×(3V×0.8/10nS) (假定Trise由10%变化至90%)。

由于输出驱动直接正比于输出电容C PD ,因而使输出驱动最小化的关键仍然在于使驱动和负载以及预计的传播延迟相匹配,因此可以选择接近2.4mA 的I OL 或称输出低驱动电流的驱动器。如果选用的驱动器的驱动电流小于所需电流,就要根据经验规律,即每个时间常数下只能完成66%的跃迁来进行RC时间常数计算。匹配驱动的另一个益处在于更低的驱动电流可降低噪声和EMI。

在使动态功率最小化时要考虑的最后一项是CL,即器件驱动的负载电容。要使动态功率最小化,布线至关重要。要正确计算总电容值,必须知道迹线和所需驱动的器件是集总负载还是具有分布负载的传输线。一般的经验是如果器件间连接线路的电气长度小于输出边缘速率的1/6 就可以作为集总负载处理。有效电气长度可由传播速度确定。例如,FR4电路板外部迹线的传播速度为160pSec/In。如果迹线长度为2英寸,则电力长度将为320pSec。对于上升时间超过1.9纳秒的输出,这就可以作为集总负载处理。对于上升时间小于1.9纳秒的负载,这就需要作为传输线进行处理。

阻抗计算公式为:

ZO = (L/C)^0.5

C = T prop /ZO

L = T prop × ZO

如果线路的阻抗是50欧,总电容值为320pSec/50或6.4pF。通常这将使所需驱动的输入负载电容的增加量小于2pF,总电容将达到8.4pF。如果开关由低到高的时间为10ns,那么所需的驱动电流为I = (8.4pF)(3V×0.8/10nS)= 2mA。

本文小结:

本文提出了一种利用统计规律研究特定用户功率使用模式的方法,为了探讨延长电池寿命的工程方法,本文还对功率的概念进行分类,并着重阐述了功率最小化的概念。由于笔记本、手机和数字消费电子市场的复苏,对于功率最小化的关注是十分必要的。本文所列举的分立逻辑手机的例子表明了了解和降低待机模式功耗的意义。通过使用最优化的分立逻辑方案,我们就可以使微型逻辑器件的待机功率降低一半,并能在实际应用中使待机功率降低5%以上。

作者:

Brent Rowe

接口和逻辑产品行销总监

Jeff Corbin

销售工程师

王蔼伦

亚太区逻辑业务部高级市场经理

飞兆半导体公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:通过以太网数据传输线传送电源

下一篇:PCB表面贴装电源器件的散热设计