- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

新型智能驱动器可简化开关电源隔离拓扑结构中同步整流器

本文描述的技术适用于数字控制,尤其适用于正确关断一个或两个在开关模式电源(SMPS)隔离拓扑中作为整流器使用的MOSFET。该技术有助于实现PWM控制器位于初级端的隔离SMPS拓扑智能驱动IC系列(STSRx) 。这些IC从隔离变压器的次级输出获得时钟信号,能为一个或两个同步整流器MOSFET门电路提供正确的门驱动信号,解决隔离拓扑同步整流器控制中所存在的问题。

隔离拓扑结构中的同步整流

在隔离拓扑结构中,如果主PWM控制器位于次级端,同步整流器的驱动问题很容易解决。实际上,由于次级端上可获取PWM信号,它能用来产生同步整流器的驱动信号,由于在驱动信号通过某种耦合器件传输到初级端时会产生传输延时,因此驱动信号还必须增加一定的延时补偿。

然而,次级端的控制配置还存在一些系统上的缺点,例如需要辅助电源启动转换器;需要将PWM控制驱动信号传送至初级开关的跨隔离电路;在电流模式控制环中,将初级开关电流信息传送至PWM控制器中存在一些困难。因此必须在初级端使用PWM控制,以实现高性能、高效率、小尺寸和低成本的SMPS。

如果主PWM控制电路在初级端,其输出信号在次级端不能以简单而低成本的方式获得,但仍然可以在次级端根据隔离变压器的输出获得这些信息。由于电路中的寄生效应,因此由隔离变压器输出得到的同步信号相对于初级端PWM信号将存在延时,并可能呈现某种程度的振荡,尤其是在非连续传导模式下。因此,提供同步整流器驱动的控制技术必须避免产生错误运行条件,这些运行条件产生自对应于初级端PWM信号的任何次级端信号同步时序作用(PWM同步信号)。

一种称为“自驱动同步整流”的技术可以在正向拓扑的基础上,通过将隔离变压器的输出作为PWM同步信号,使MOSFET作为整流器工作于隔离拓扑结构。

遗憾的是,该技术应用很不方便。例如,在前向变换器中,驱动信号决定于主变压器的消磁方式。这样,由于门电路缺少必要的驱动信号,驱动信息在快速恢复式整流MOSFET的体二极管中传送的时间将会很长。这样不仅损害了同步整流,还限定驱动同步整流器只能与某些专用的特殊消磁技术协同使用。

此外,当初级输入电压的可变范围很大(公因子为2:1)时,由于难以提供总是能与门电路范围相匹配的驱动信号电压值,该技术很难实现。

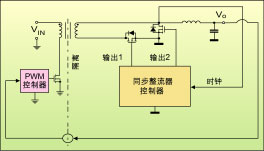

因此,在带有初级端控制的隔离拓扑中,驱动同步整流器最适用的方法是使同步整流器配备处理来自隔离变压器次级端同步信号(时钟)的控制电路,并解决任何与两个对应于时钟输入的MOSFET驱动信号时序有关的问题。图1显示了前向转换器中控制驱动实现的简化图。

跨导和击穿问题

控制电路中必须用简单的方法使同步整流器工作在隔离拓扑结构,处理来自时钟信号输入的同步整流器驱动信号的正常时序生成。时钟信号和同步整流器(SR)驱动信号之间必须提供适当的空载时间以避免开关之间的跨导。

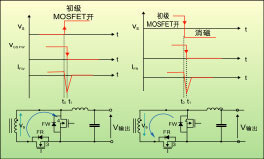

控制器还需要处理击穿问题。击穿可能发生在隔离拓扑的次级端,出现这种问题的条件决定于电路拓扑结构。通常,同步整流器打开的变换过程很容易处理,而关断的变换则需要特殊处理。实际上,由时钟产生驱动信号的电路会产生传输延时,该延时加到隔离变压器的信号中。这些固有的延时将延缓双向同步整流器开关的关断,产生错误的电路条件,使得不可能使用单向二极管器件。这种情况下会产生短路环,将产生非常高的电流峰值,该峰值电流大小仅受电路中的寄生参数限制。图2显示了前向拓扑的短路条件。

因此,有必要引入可以避免产生错误运行条件的特定空载时间。特定空载时间可产生正确预测的关断转换时序,并保证SR在时钟信号转换之前关断。但开关的预测值必须降至最低,以减少体二极管的导通时间,从而避免降低效率。特别地,预测值可用作优化参数,并按照设计的物理实现对电路操作进行调整。实际上,SR下降电流的关断时间斜率取决于多个参数,如转换器的输入和输出电压、先前的驱动电流大小及电路中的寄生参数(如漏电感)。预测时间可由特定的电路操作条件加以调节,以实现最佳的性能,即较高的效率、体二极管的通电时间最短、相应的反向恢复电流最小。

新方法介绍

这里引入的方法是为了从输入时钟信号产生适当的同步整流器驱动信号,该驱动信号与开关模式电路的主PWM信号相关。

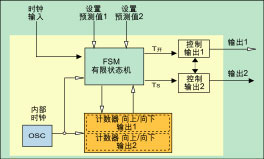

这些功能是通过使控制电路与时钟信号(尤其是开关信号)在转换器开关频率上保持同步而实现。利用频率远高于转换器开关频率的振荡器和两个数字计数器模块来实现同步功能,两个计数器模块具有不同的功能:一个负责对整个开、关时间进行测量,并将该信息存储以用于下一周期;另一个则根据电路拓扑的特定需要,对时钟信号的开或关断时间进行相同的测量。系统的精确度和分辨率与内部数字工作频率相关,并用来实现这种方法。由于可获取前一周期的周期大小和开、关时间间隔参数,因此能够很容易地在下一周期中生成正确的输出时序,尤其是能够得到关断转换的正确预测。预测值可根据系统的分辨率,以最小数字脉冲周期离散量的形式进行设定。该系统的整体结构参见图3。

在次级端带有两个互补信号(前向拓扑)的常见应用中,系统整体结构由一个内部振荡器、一个有限状态机和两对加法/减法计数器以及两个控制输出逻辑块组成(参见图3)。该系统结构具有3个输入和两个输出:输出是转换器次级端上两个MOSFET的驱动信号,而输入则为时钟、OUT1的预测时间设定和OUT2的预测时间设定。

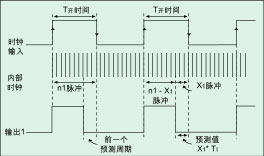

在频率fI>fS(周期TI)处,与内部振荡器时钟信号(CKI)上升沿同步的有限状态机是系统的中枢,它产生两个信号:OUT1和OUT2,两个信号在开和关断条件下均不重叠。时钟输入为频率为fS(周期为TS)的方波信号,fS 称为开关频率;而预测时间在外部通过相关的输入进行设定。两个计数器的工作方式也不相同,DOWN计数器负责预测输出的关断,而UP计数器负责连续得到OUT2开关周期的持续时间信息或OUT1的Ton持续时间信息。这样,开关周期中,输出关断的预测值将取决于前一开关周期存储的信息。此外,还将连续检测开关周期,并得到Ton时间。与OUT2相关的计数器位数由转换器最小和最大开关频率确定,而与OUT1相关的计数器位数则由转换器的最小和最大Ton值确定。

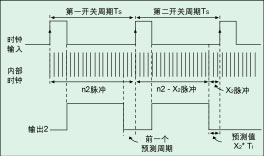

在稳态条件(固定开关频率和固定占空比)下,紧邻的两个开关周期,与OUT2相关联的系统部分的按图4所示的时序工作。

第一个开关周期

在时钟输入的上升沿,第一个加法/减法计数器开始作为加法计数器,计算内部时钟(CKI)的脉冲数目。在时钟输入的下一上升沿(第一个周期TS的末端),计数器停止计数,计下的脉冲数(n2)反映了开关周期的持续时间。系统将保存这些信息,以便于下一开关周期使用。

第二个开关周期

在CK输入的上升沿,第一个计数器作为减法计数器计算内部时钟的脉冲数目,并在n2-X2时刻停止计数,在该时刻输出2关断。第二个计数器则计算内部时钟的新脉冲数目,并在开关周期TS中更新持续时间信息。

输出2关断的预测值由X2×TI 给出,并由“预测值2输入”进行设定。在每个周期,根据前一周期情况转换计数器的功能,即的作为加法或减法计数器。

在对与输出1相关的系统部分,其它两个加法/减法计数器为了能预测输出1的关断,还将考虑TON的持续时间信息(参见图5)。

第一个开关周期

第一个计数器在时钟上升沿开始计数,并在下降沿停止计数。计算得到的脉冲数目为n1,该信息给出了TON时间。

第二个开关周期

第一个计数器作为减法计数器,假定OUT1关断预测值等于X1×TI,在n1-X1时刻停止计数,预测值在“OUT1 预测值输入端口”中设定。第二个计数器在这段时间内计算时钟输入上升沿和下降沿之间的内部时钟脉冲数目。

当时钟输入随TON时间和开关周期变化时,第一个开关周期和第二个开关周期之间的条件会有所不同,所有这些条件可能导致计算错误。

无论任何情形,这些可变条件的根源在于转换器的PWM控制器。例如,在开关转换器中,如果负载发生变化,PWM控制器将增加或减少TON时间来调节输出电压。TON时间的变化速率取决于转换器的控制循环带宽,开关转换器的最大可变控制循环带宽为开关频率的1/10。这意味着用该方法在产生这些变化后,其速度足够快来处理这些变化而不会产生任何问题。

这种控制同步整流器关断时间的方法目前正在硅器件系列(STSRx)的设计中应用。这些专为特定拓扑应用(如前向、后向和双端拓扑)设计的器件,以及其它本文未涉及的功能,将有利于经济而简单地实现隔离拓扑下的同步整流技术。

作者: Fabrizio Librizzi

技术营销及应用工程师

意法微电子公司

www.st.com/vregs

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...