- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用数字控制优化单相同步降压转换器的效率

随着在线语音、视频、游戏和商务等数据密集型活动的普及,对带宽的要求正以前所未有的速度增加。数据中心的容量也在相应增加,但它们却面临有关电力成本和可用性,以及因计算要求提高而导致热效应不断增加的挑战。因此,有一点越来越重要,那就是最新型的功率设计必须能高效工作以确保满足带宽要求,并同时减少功耗及发热。

数字功率控制提供了一种增加服务器功率转换效率并简化设计的方法。采用数字环路控制可设计出更具效率的降压转换器,也能提高各相位的电流容许量。通过使用一种独特的栅极驱动控制算法的数字控制IC,单相同步降压转换器在低电压下能提供40A的电流。与现有解决方案相比,此设计方案的效率提高了2%。

改进的降压转换器

人们通常认为功率转换器数字方案的效率低于模拟方案的效率,但是新型数字PWM控制器能获得同于或高于传统模拟控制器设计的效率。与此同时,新型数字PWM控制器还可以扩展其性能界限。

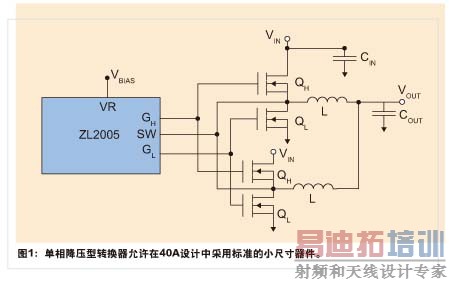

与标准降压转换器不同是,这种设计增加了与第一个功率链并联的第二个功率链(图1)。这种设计以Zilker Labs的ZL2005数字功率控制器为基础,仍然是单相IC,但包含第二组MOSFET和第二个电感。由于采用能调节死区时间控制的栅极驱动控制数学算法,这种设计独特的控制器不但可以优化效率,还可在单相工作状态下输出高电流。该设计可输出40A电流,高于单相控制通常输出的20A~30A。

这个转换器被设计成将12V输入转换为1.8V或1V输出,输出电流高达40A。它的主要设计目的是尽可能提高效率,同时保持理想的瞬态特性。最大输出纹波的目标值为10mV,目标的瞬态响应是在25%电流负

载下保持在输出电压的3%以内。

这种双功率链设计允许使用标准的元件,因为多数可用的电感的额定值都是30A。它也可以使用普通电感。由于设计针对效率而进行了优化,因此有必要对降压转换器内消耗功率的所有设计点进行审查。

与标准降压转换器设计一样,降压转换器改进后的功率级中的每个元件都会消耗功率。输入和输出电容以其等效串联电阻(ESR)消耗功率,大小与所流过的纹波电流成比例。

电感线圈和磁芯材料的损耗会消耗功率。磁芯损耗与流过电感的纹波电流和纹波频率成比例。同步MOSFET (QL)以两种方式消耗功率:一是大小等于电流的函数的通道电阻

(RDSON),二是MOSFET导通/关闭所需的栅极驱动电流。

栅极驱动电流损耗与频率成比例。同样,控制MOSFET (QH)也因其RDSON和栅极驱动电流而消耗功率,在其导通和关闭的瞬间也会消耗功率。在导通和关闭转换过程中消耗的功率称作开关损耗,它与频率成比例。许多功率级元件的损耗都与频率成比例,增加频率就会增加功耗,从而降低效率。控制MOSFET(OH)的导通时间可决定输入电压和输出电压的转换比。当QH关断时,电感电流继续流过同步MOSFET OL。为避免输入电压电源短路,ZL2005必须确保QH和QL不同时导通(即交叉导通)。QH和

QL都关断的时间称作死区时间。

图1

在死区时间期间,电感电流必须流过QL中的寄生漏极二极管。该二极管的电压降和产生的功耗大于电流流过QL漏极所产生的电压降和损耗。因此,应使死区时间降低到最小值,但不能降低到使MOSFET交叉导通的程度。这种情况能使高压侧栅极驱动(GH)的上升沿转换和下降沿转换时都有最佳的死区时间。如果MOSFET的时序在任一方向偏离此最佳值,效率都将会降低

。

死区时间控制

Zilker Labs的数字直流(Digital-DC)技术整合了可在功率级效率基础上连续优化MOSFET死区时间的算法。具有这种功能的典型模拟PWM试图使死区时间最短,但这样做可能使死区时间变得太短,从而出现交叉导通,这是由于MOSFET电容特性的差异(可能很大)而引起的。

相反,数字直流架构则在给定输入/输出电压比的基础上,通过寻找最低占空比,不断试图优化效率。这种最小占空比下的效率最高。需要注意的是,最佳效率点并非总出现在死区时间最短的情况下。

此外,该算法能捕捉FET电容或其它参数的变化,并在计算中给予补偿。另外值得一提的是,ZL2005的控制环全部以混合信号硬件实现。在实时处理环路控制信号时,不存在微控制器块或DSP功能干扰,

这样便可以获得模拟控制器的性能,却没有通常与纯数字电路实现相关的额外功率损耗和高的时钟频率。

在ZL2005中,输出电压误差信号通过一个A/D转换器进行转换,并通过器件控制算法进行处理。本设计采用的控制器混合PWM方法来处理得到的数字信息,并将时序信息(占空系数D和其补码D’) 转译成PWM驱动器的输入。一种专利架构和算法使这种占空比信息特别准确,精度达0.3μs(200kHz)~30ps(2MHz)。

尽管超出了本文讨论的范围,但这种数字直流架构也能在不增加额外元件的情况下实现功率管理功能,如跟踪、预留余量、监测以及排序。为控制这些功能,ZL2005支持PMBus标准指令集。控制器运行也可以通过引脚跨接来配置,在本降压转换器设计中就是采用了这种方法。

效率优化

降压功率级的设计要求在尺寸、效率、电气性能和成本间进行权衡考虑。可以在牺牲效率的情况下增加开关频率来缩小尺寸,也可以通过采用过孔电感和电容来最大限度降低成本。不过,这些元件物理的尺寸大,电气性能可能没有表面贴元件好。

1、频率选择

必须在设计开始时就选择工作频率。这个频率是起始频率,可随设计的进展而调节。表1汇总了普通应用中的一些频率范围。为使效率最高,在本例中选择300kHz的开关频率。

数字直流技术可使设计工程师不用改变电路板上的任何元件即可调节频率。这样,设计工程师就能在达到了所有其它设计目标之后,再选择效率最高的最佳频率。可以通过将专用引脚跨接到3个状态中的一个(高电平、悬空或地)来将频率调整到预定义值上。这也可以通过SMBus接口来实现,可以将频率设置在200kHz~2MHz之间。

2.电感选择

选择输出电感时必须考虑多个折衷。电感量的大小必须足够大以实现低纹波电流(IOPP)。纹波电流低则可以使用更小的输出电容,而同时仍能达到理想的输出纹波电压。高电感值将牺牲输出瞬态负载性能,因为纹波电流低则输出纹波低,纹波电流高则瞬态负载改变幅度时输出偏移小,所以必须在低纹波电流和高纹波电流之间作出选择。选择输出电感电流纹波等于期望的负载瞬态阶跃幅度

(IOSTEP)是一个好的开始:

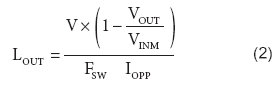

这样输出电感就可以采用下式计算,其中VINM是最大输入电压:

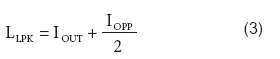

在40A设计(每个电感器为20A)的情况下,采用VINM=14V、IOPP=10A、FSW=300kHz和VOUT=2.5V(VOUT的取值范围为1V至2.5V)。利用等式2,计算得到电感值为685nH。这里选择PG0077.801 750nH、1.3mΩ、31A的脉冲电感器。这个电感器可提供串联电阻相对较低(1.3mΩ)的理想电感,同时还可提供足够的峰值和平均电流额定值。此外,还有现成的小型表面贴装封装可用使用这一设计原则,纹波电流IOPP将可与最大输出电流步长要求相比。峰值电感电流(ILPK)采用下列等式计算,其中IOUT为最大输出电流(在整个开关周期内的平均值):

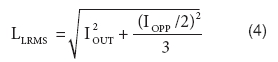

一旦选好了电感,就可以计算出电感器内的ESR和磁芯损耗。使用电感制造商数据手册中给出的ESR值,功率=ESR×ILRMS。ILRMS由下列等式计算所得:

其中,IOUT是最大输出电流。

在大多数情况下,电感值将随着平均负载电流的变化而发生明显变化,电感ESR也将根据运行状态下元件温度的变化而变化。为达到效率目标,应考虑这两种效应的影响。对于高电流应用,如果效率很关键,则选择ESR较低的电感器尤为重要。

3.其它元件的选择

数字技术使得设计工程师可以校准传感元件,以适应工艺和温度变化。当整合了内部或外部温度传感器(内部或外部)时,这一校准时可以得到更为准确的电流读数。

校准可以在开发测试期间或者在电路板级终测试期间进行。可以根据传感元件的实际测量数据调节多个参数,并将它们存储在器件的非易失性存储器内。这些参数包括传感元件的增益(在如下所述的MOSFET RDSON)、偏移量(布局及传感元件的变化)以及温度系数(对MOSFET RDSON而言,此系数通常约为50%)。有了校准功能,选定的元件就不必因温度变化而不得不采用超安全标准设计,从而避免不必要的功耗和额外费用。

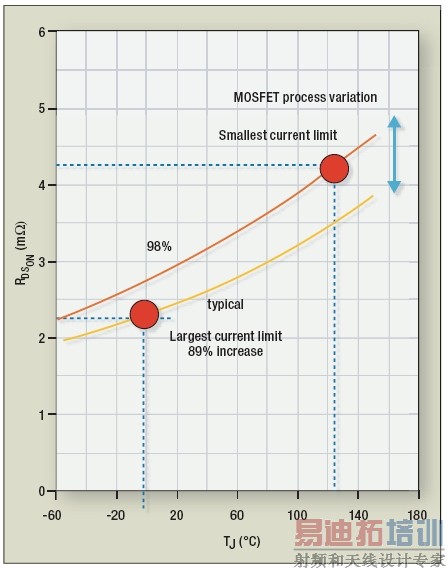

把对输出电流的约束条件应用到整个转换器设计中,可以降低MOSFET、输入和输出电容器及电感器等其它元件的要求。在传统模拟实现中,当将RDSON用作感应元件来设定电流限值时,该参数随温度发生变化可能意味着元件要按超过设计要求50%的标准来设计。当温度从25℃上升到125℃时,RDSON将增加50%。

除此之外,设计工程师还需要考虑传感元件的工艺偏差,此偏差可能高达30%(图2)。这意味着对于应用在0℃~125℃整个范围的20A系统,电流限值必须设置成平均值38A,这要求使用额定电流为45A的电感和MOSFET。通过采用温度补偿和板上校准,电流限值可能更苛刻,设置点精度优于5%。这样,电流限值将降低到平均22A,可以选择25A电感和MOSFET。所选的元件将更小、成本更低,而且能提供更精确的保护功能。

在考虑到这些要求后,选择IRF6635作为低压侧MOSFET。IRF6636的额定漏电流在70°C温度下为25A,RDSON非常低(在4.5V下为1.8 mΩ),可以最大程度地降低传导损耗。将两个MOSFET并联可以提高电流,并保持器件的电流额定值(在高压侧也如此)。对高压侧MOSFET选择IRF6636是因为它的栅极电荷(QG)低,开关损耗最小。对于输入至输出的降压比很高的特定场合,高压侧MOSFET保持导通的

时间不长,大部分损耗是开关损耗。

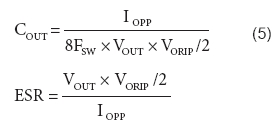

输入和输出电容的选择要满足总体瞬态目标,并使输入和输出纹波电流最小。对于高纹波电流,电感值小可能导致非常大的输出电压纹波。同样,如果瞬态负载阶跃很大,当电感电流斜坡上升或下降到新的稳态输出电流值时,需要相对大的电容值来使输出电压偏移最小。

作为起点,把输出电压纹波的一半分配给电容器ESR,另一半分配给电容,如下式所示:

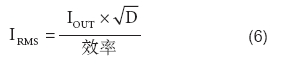

假设1V输出电压的目标纹波为3mV,根据式5计算出COUT为3000μF。为提供一些设计余量,选择输出电容为4400μF。输入电容主要由降压转换器输入端的纹波电流决定,该纹波用下式确定:

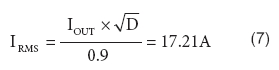

RMS纹波电流的计算如下:

输入电容额定值应该为以上计算出的纹波电流的1.4倍,以确保有50%的降额。建议使用额定电压等于最高预期输入电压的1.1倍、ESR低的X7R或X5R电介质陶器。可以采用陶瓷和低ESR有机或聚合物电解电容的组合来降低成本和体积。通过把以上计算出的总纹波电流应用于所有的输入电容上,可以确定每个元件的纹波电流。采用电流分流公式计算每个电容的纹波电流时,应该考虑每个电容在开关频率下的阻抗。

通过采用上述方法,所选择的元件都针对给定工作条件进行了优化,同时也针对成本进行了优化。设计工程师总是倾向花更多的钱购买更好的低损耗元件来进一步提高效率,然而,实用的商用方案可以在增加的成本仅占总电路成本一小部分的情况下提高效率。

效率结果

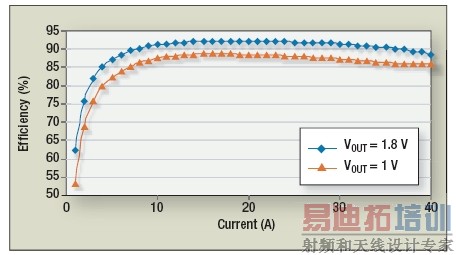

图3给出了该降压转换器的测量效率。对于20A额定电流时的1.8V输出,转换效率高达92%以上,即使在最大电流(40A)时的曲线也非常平坦。这种高效率特性是通过多种方法来实现的。首先是采用了Zilker Labs公司的栅极驱动控制算法,并针对高压侧和低压侧MOSFET分别将死区时间动态调节到4ns和8ns。当固定死区时间时,设计工程师不得不增大这些值,以将任何工艺偏差都考虑进去并避免出现交叉导通。额外的死区时间将导致低压侧MOSFET中体二极管的传导损耗更大。

另一个原因是采用MOSFET并联来减少寄生电感、降低总电阻并提供更好的散热。本例采用了两个高压侧和两个低压侧MOSFET。减少MOSFET数量将增加传导损耗,而增加MOSFET数量则会增加开关损耗。

由于采用了专利引脚跨接技术,ZL2005的大多数配置和设置都无需使用任何外部元件,这就降低了功率损耗,并为改进热性能提供更大的铜面积。驱动器强度和速度允许采用低电阻MOSFET,且不会影响效率。

电流大于20A~30A的应用一般地采用两相方案设计。单相方案的缺点是增加了电流纹波,本例的额定输入纹波比典型的两相方案大50%。

在两相方案中,虽然给定瞬态性能对输出电容的要求较低,但输出纹波也将降低。但是,在此电流下,选择输出电容器主要由电容器的总体电阻(ESR)来决定,需要的元件数量相差不多。两相方案也需要复杂的电流平衡算法,以确保两相电流相同。布局将变得更加重要,这也意味着要使用额外引脚来获取电流共享信息。

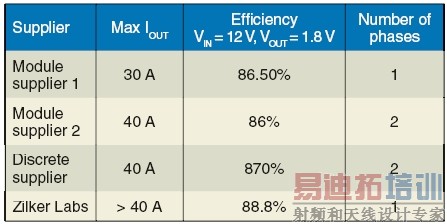

采用这个单相设计所达到的动态性能完全满足设计目标。从30A到40A的10A负载阶跃(2.5A/μs)会产生±30mV (为VOUT的3%)的输出电压偏移。表2对最近推出的多个20A到30A方案作了比较。

本设计在降低系统复杂性的同时,还将效率提高了2%至4%。

作者:Benoit Herve

产品经理

Zilker Labs公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:使用PoE为IP相机提供安全电源

下一篇:面向汽车苛刻应用的模拟IC介绍