- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

针对便携设备的高端负载开关及其关键应用参数

对于各具特色的移动电话、移动GPS设备和消费电子小玩意等电池供电的便携式设备应用来说,高端负载开关一直受到众多工程师和设计人员的青睐。本文将以易于理解的非数学方式全方位介绍基于MOSFET的高端负载开关,并讨论在设计和选择过程中必须考虑的各种参数。

高端负载开关的定义是:它通过外部使能信号的控制来连接或断开至特定负载的电源(电池或适配器)。相比低端负载开关,高端负载开关“流出”电流至负载,而低端负载开关则将负载接地或者与地断开,因此它从负载“汲入”电流。

高端负载开关不同于高端电源开关。高端电源开关管理输出电源,因此通常会限制其输出电流。相反地,高端负载开关将输入电压和电流传递给“负载”,并且它不具备电流限制功能。

高端负载开关包含三个部分:

1. 传输元件:本质上是一个晶体管,通常为一个增强型MOSFET。传输元件在线性区工作,将电流从电源传输至负载,就像一个“开关”(与放大器相对应)。

2. 栅极控制电路:向传输元件的栅极提供电压来控制导通或关断。它还被称为电平转换电路,外部使能信号通过电平转换来产生足够高或者足够低的栅极电压(偏置电压)来全面控制传输元件的导通和关断。

3. 输入逻辑电路:主要功能是解释使能信号,并触发栅极控制电路来控制传输元件的导通和关断。

传输元件

传输元件是高端开关最基本的组成部分。最经常考虑的参数,特别是开关导通时的阻抗(RDSON),与传输元件的结构和特性有直接关系。

由于增强型MOSFET一般在工作期间消耗的电流较少,在关断期间泄漏的电流也较少,并且具有比双极晶体管更高的热稳定性,所以被广泛用作高端负载开关中的传输元件。本文将专门介绍基于增强型MOSFET的传输元件。增强型MOSFET传输元件可以是N沟道FET,也可以是P沟道FET。

当N沟道FET的栅极电压(VG)比其源极电压(VS)和漏极电压(VD)高出一个阈值(VT)时,N沟道FET就会被完全转换至导通状态或者工作于其线性区。以下式子给出了导通条件的数学表达式:

VG-VS=VGS>VT

VG-VT>VD

或者是,

VGS-VT>VDS

其中,VG为栅极电压、VS为源极电压、VD为漏极电压、VT为FET的阈值电压、VGS为栅-源极压降、VDS为漏-源极压降,所有参数均为正。

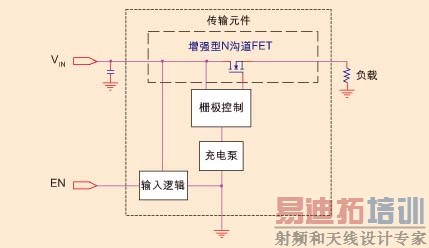

图1:具有内置电荷泵的N沟道FET高端负载开关。

当N沟道FET导通时,漏极电流ID为正,从漏极流向源极(如图1和图2所示)。当P沟道FET的栅极电压(VG)比其源极电压(VS)和漏极电压(VD)低出一个阈值(VT)时,P沟道FET就会被完全转换至导通状态或者工作于其线性区:

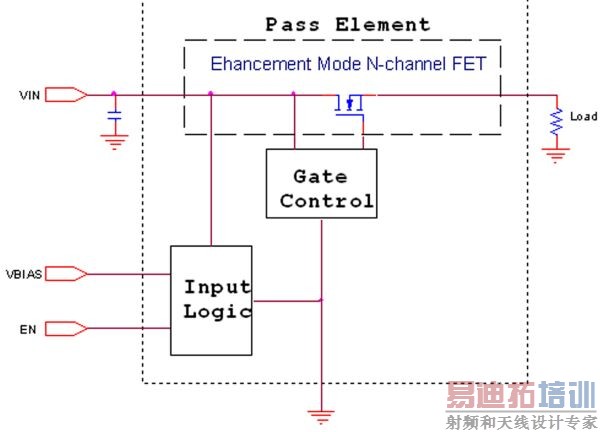

图2:具有额外VBIAS输入的N沟道FET高端负载开关。

VS-VG=VSG>VT

VD-VT>VG

或者是,

VSG-VT>VSD

其中,VG为栅极电压、VS为源极电压、VD为漏极电压、VT为FET的阈值电压、VSG为源栅极压降、VSD为源漏极压降,这里的所有参数也均为正的。

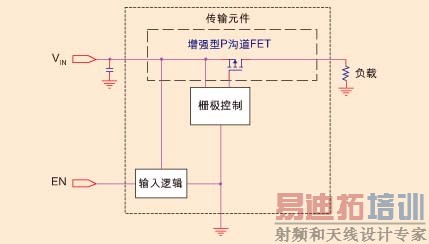

当P沟道FET处于导通状态时,漏极电流ID为负,从源极流向漏极(图3)。N沟道FET将电子用作“多数载流子”,与P沟道FET的“多数载流子”空穴相比,电子具有更高的移动率。这意味着,在相同的物理密度下,N沟道FET比P沟道FET具有更高的跨导,从而使得在导通状态期间产生较低的漏-源极阻抗(即RDSON)。N沟道FET的RDSON一般为相同尺寸的P沟道FET的RDSON的1/3~1/2,漏极电流ID也会高出相应的倍数(未考虑连接线厚度和封装等其它限制参数)。这还表示,对于相同的RDSON和ID,N沟道FET一般需要较少的硅片,因此它的栅极电容和阈值电压比P沟道FET要低。

图3:P沟道FET高端负载开关。

此外,由于当开关导通时N沟道FET的VD比VG低VT,并且VD一般与VIN相连,因此有可能传递给负载的VIN非常低。理论上讲,N沟道FET开关的VIN可以低至接近GND,并且不高于VG-VT。另一方面,P沟道FET开关传递给负载的VIN(与VS相连)总是高于VG+VT。但这并不表示在任何情况下选择传输元件时N沟道FET都比P沟道FET好。

如上所述,N沟道FET的一个基本属性是开关导通时工作在线性区,VG要比VD高VT。但是,由于VD几乎总是与VIN(通常是开关的最高电压)相连,因此VG必须从现有电压(如外部使能信号EN)进行由低向高的电平转换,或者通过直流偏移进行从低向高的偏置,直流偏移是单个新的高压轨,通常被称为“VBIAS”。

如果栅极电压从使能信号进行从低向高的电平转换,通常需要一个电荷泵作为附加的内部电路。电荷泵需要一个内置的振荡器,芯片上至少需要一个“快速”(flying)电容器,从而产生栅极电压(通常是在导通过程中的多个使能信号)。这当然增加了设计复杂性和硅片大小,从而抵消了N沟道FET因RDSON较低所带来的硅片缩小的优势。当负载电流相对较低(几安培)时,电荷泵确实会增加硅片面积,并且增加的面积比RDSON所能缩小的面积要大,这使得N沟道开关解决方案的成本和设计复杂性要高于P沟道开关方案。更多细节如图1所示。

如果栅极电压通过直流偏移VBIAS进行从低向高的偏置,就不再需要电荷泵,从而硅片面积的增加也不再是主要问题。但是由于可能不具备额外的高压轨(这是大多数电池供电的设置和器件都需要的),因此这可能不是系统级的最佳解决方案(图2)。

而在P沟道FET中,VG通常低于VS(与VIN相连)。只要开关导通时VS保持在VG±VT的范围,那么它将始终工作在线性区,并且不需要特定的内部电路或外部电压轨。这是通过采用栅极控制电路将使能信号的电平从高向低转换至适当的VG电平来实现的。此方案不需要太多的电路或者额外的硅片面积(见图3)。

N沟道高端负载开关通常是要求极低RDSON的高功率系统或者要求将接近GND的低VIN传递给负载的低输入电压系统的理想选择。另一方面,P沟道高端负载开关在要求设计复杂度不高的低功率系统或者要求将高VIN传递给负载的高输入电压系统中具有一定优势。

栅极控制

栅极控制电路或者电平转换电路通过控制MOSFET的VG来实现其导通或关断。栅极控制电路的输出由从输入逻辑电路收到的输入直接决定。

在导通期间,栅极控制电路的主要任务是对使能信号进行电平转换,以产生高(N沟道)或低(P沟道)VG来完全导通开关。同样,在关断期间,栅极控制电路产生低(N沟道)或高(P沟道)VG来完全关断开关。

许多高端负载开关都在栅极控制电路中采用“斜率控制”或“软启动”功能。斜率控制功能可以在开关导通时限制VG的上升速度,从而逐步产生ID。其目的是为了保护负载不受过多“电涌”的影响,电涌有可能导致栓锁等故障。

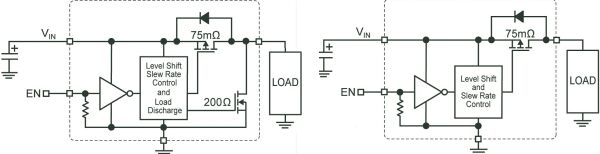

负载有时不仅仅具有阻抗性,也会具有高容性。因此,当开关关断时,聚集在容性负载上的电荷不会迅速放电,这会导致负载没有完全关断。为了避免这种情况,一些高端负载开关加入了“活动负载放电”功能,其目的是提供一个电流通路,在开关关断时使容性负载迅速放电。通常采用一个小型低端FET来实现该功能。图4是该方法的示意图,其中,底部N沟道FET的栅极与栅极控制内核相连,漏极与负载相连,当顶部的主开关P沟道FET关断时,底部的N沟道FET导通,以使容性负载放电。

图4:MIC94060/1/2/3P沟道高端负载开关产品结构图。

输入逻辑

输入逻辑电路的唯一功能是解释使能信号,并将正确的逻辑电平传递给栅极控制电路,以便栅极控制电路能够以输入逻辑电平控制传输元件的导通和关断。输入逻辑电路只采用下拉电阻就可以实现。

在某些情况下,使能信号和栅极控制电路之间需要缓冲器。这是因为使能信号无法为栅极控制电路提供足够的驱动电流来驱动VG,而缓冲器却可以充当额外驱动电流的来源。

关键应用参数

工程师在设计中采用高端负载开关时需要考虑一些关键应用参数。

第一个关键参数是ID。这是在设计周期早期选择的系统级参数。高端负载开关的ID由MOSFET物理特性(N沟道或P沟道)、MOSFET的尺寸、连接线的物理特性(长度和厚度)以及封装的热性能等参数决定。通常,高ID开关为N沟道,采用热增强型封装,而低ID开关为P沟道,采用小型封装。

第二个关键参数为RDSON。当选定ID时,RDSON越低就越好。这是因为较低的RDSON可以提高总效率、降低VIN和负载之间的压降并减轻开关的散热压力。

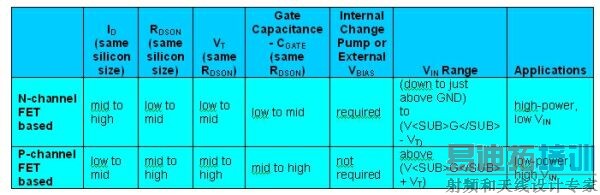

表1:N沟道FET开关和P沟道FET开关的比较。

如果ID和RDSON都已确定,设计人员通常会考虑开关的以下四个关键参数:动态响应、关断电源电流、关断泄漏电流和封装尺寸。

对于高端负载开关,动态响应是指负载电压随着使能信号逻辑电平的变化从GND升至VOUT(=VIN-RDSON×ID)或者从VOUT降至GND所用的时间。

当使能信号在传播延迟或导通延迟时间(tON_DLY)之后使能时(由栅极控制电路和输入逻辑电路引起),VG将转换至导通开关所需的足够高(或足够低)的电平。此时,负载上的输出电压(N沟道FET开关的输出电压为VS,P沟道FET开关的输出电压为VD)开始上升,电压达到满VOUT所用的时间称为导通上升时间(tON_RISE)。要求快速响应的应用需要tON_DLY和tON_RISE足够短,而需要软件启动来限制电涌的应用则要求tON_DLY和tON_RISE相对较长,这取决于系统要求。

同样,当使能信号在传播延迟或关断延迟时间(tON_DLY)之后使能无效时,VG将转换至关断开关所需的足够低(或足够高)的电平。此时,负载上的输出电压从满VOUT开始下降,电压下降到GND所用的时间称为关断下降时间(tOFF_FAIL)。通常要求tOFF_DLY和tOFF_FAIL足够短,以便负载能够迅速被关断。如果负载具有较大的容性元件,活动负载放电功能将有助于减小tOFF_FAIL。

关断电源电流和关断泄漏电流也是需要考虑的重要参数,特别是在设计需要较长的电池工作时间的电池供电设备时。关断电源电流是内部电路在开关关断时消耗的电流。关断泄漏电流是开关关断时MOSFET传递给输出的电流。关断电源电流和关断泄漏电流越低,系统总效率就越高。对于电池供电的应用,这可以获得更长的电池工作时间。

对于封装尺寸(管脚面积和外形轮廓)而言,很明显是越小越好。特别是对于空间有限的低电流系统(电池供电的手持设备)中使用的P沟道开关,情况更是如此。

Micrel半导体公司提供一套完整的P沟道FET高端负载开关,目标市场为电池供电的便携式设备。最新成员MIC94060/1/2/3产品系列拥有业内领先的关键参数,而这些参数都是设计师们最关心的。

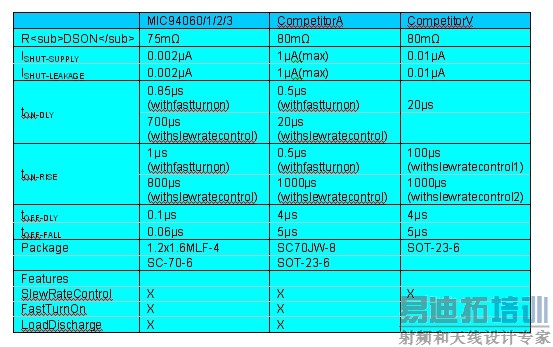

表2:MIC94060/1/2/3与其它产品的比较。

从表2可看出,MIC94060/1/2/3可在2A电流等级提供75m最佳RDSON。此外,它还具有市场上最低的关断电源电流和关断泄漏电流,具有导通和关断状态下出色的动态响应以及1.2×1.6mm的最小MLF封装。因此,在文章开头提到的那些电池供电的便携式设备中,MIC94060/1/2/3已经确立了其性能领先的地位。

作者:Qi Deng

混合信号产品高级产品营销经理

Micrel半导体公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...