- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

嵌入式闪存使“智能”汽车接口应用得以实现

现代汽车中日益增加的汽车电子元件已对汽车的空间和重量提出了挑战。并且,在汽车电子集成的过程中,当重量的问题通过使线束合理化得以改进后,空间的限制仍然为主要的关注点。

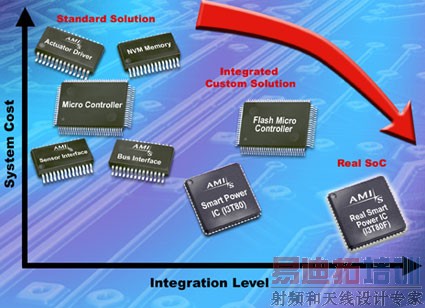

因此,对于关注节省空间的工程师们来说,所采用的潜在的半导体技术集成水平就显得从未有过的重要。无论怎样,通过集成电路对元件进行替换,最新技术有助于使元件数量趋于合理,而增加IC的“智能”性也能进一步改进集成的功效。

实现这一高水平集成的关键在于混合信号半导体技术。利用该技术可进行这样一种开发应用:将模拟和数字元件及一些高压三极管结合到一个单芯片当中。显而易见,这一使得应用面板上的元件数量降低到一个单一封装器件的能力,为节约大量空间提供了可能。

当今的半导体技术如果也能为嵌入一颗微控制器及非易失存储器提供可能,集成元件就能为工程师们提供一种快捷并可进行本地控制和应用管理的方法,该应用管理的范围囊括传感器接口方案及电机驱动器所需的机电执行装置方案,这在现代汽车中正日益普及。这一工艺对系统级芯片元件和诸如智能传感器接口之类器件的应用提供了可能。

更优成本

你可以想象,对各种不同的共存元件进行安排,特别是还要产生必要的NVM可不是一件容易的事。因为有复杂度要求,就会有潜在成本的上升。因此其决窍就是在确保最终IC仍能提供有成效的取代方案的同时对各种元件加以集成。

要做到这一点,最重要的是查看应用结构并对每个功能块的规格进行预估。例如在大多数应用中,NVM的复杂技术可能有助于使整个芯片的面积减少三分之一。对诸如16或32闪存与8kB的电可擦除只读存储器(EEPROM)之类的应用更可见其优势。

尤其需要强调的一点是:设计中NVM元件不可与其它如引擎控制单元(ECU)或BCU车身控制单元(BCU)混合使用。通过这种方式,工艺成本可降低,元件面积的三分之二都不需要采用复杂的NVM工艺,并且半导体制作过程中所需的价格不菲的光刻掩膜的成本也会降至最低点。

[p]

另一种将两种工艺集成在同一块芯片的取代方法是以两种不同的半导体工艺将两种独立的芯片集成在一起。例如将从不同的生产线获得的两种裸片结合到同一塑料封装中,就使现有制造工艺的能力得以利用。这里的问题是:在所采用的装配流程中,是选择堆叠式或是选择并列工艺?因为两种工艺各有其利弊。

堆栈裸片工艺固然稳定,但也会出现因消费者现场失误造成的不利:由于一个裸片会掩盖问题并对问题的分析造成阻碍,因而很难对出现故障的器件进行分析。另一方面,采用并列技术需要对定制压焊垫进行定位,以有效地在两个芯片之间进行绑定。绝大部分应用所采用的首选方案均需要一个具有嵌入式闪存的标准微控制器,这种内部绑定的应用具有重大实际限制。

这就是此前所提到过的,AMI半导体已开发了用于嵌入式闪存的自有方案,即大家所知的HiMOS。这种技术基于一种简化的方法,仅仅在基础半导体工艺的制作过程中增加了几个步骤而已。由于额外制作步骤的数量减少了,HiMOS工艺是嵌入式非易失存储器的成本降低到可以集成到一个单芯片之中。

通过HiMO NVM技术与公司建立的I3T80智能电源技术的集成,已能在单个芯片中提供0.35 μm CMOS混合信号及80V高压的能力,使得完全集成的SoC方案得以发展,实现了成本和空间的显著降低及性能的提升。特别是包含闪存工艺只需要对I3T80基础工艺掩膜组增加三个光罩层。对于一个嵌入式闪存的单个芯片,它只占该芯片总体积三分之一;掩膜层数量越少,HiMOS方案的单元密度就越低,从而使整个替代技术的净成本降低15%。

未来之路

最后,除了节省空间之外,具有高压能力的嵌入式闪存技术的一个更大的优势在于元件的长期供应。例如,在汽车与工业应用中,产品的寿命周期能达10年或更多。将闪存嵌入IC可以防止出现技术生命终结的风险,并且由于逐步淘汰当前工艺而采用新的工艺,需要对设计进行定期检验,这是采用分立式NVM或闪存微控制器时经常会出现的问题。

Herve Branquart

AMI半导体

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...