- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

采用箝位电路抑制车载电压瞬变

由车载电气系统供电的电路必须能耐受严酷的环境。电压瞬变有可能是随机的,或重复性的。重复性的瞬变(例如引擎的转动)可能产生数百伏特的电压,但对于车载电子组件来说,最为剧烈的瞬变来源于负载倾卸(load dump)。

负载倾卸是急促的能量卸放,由于交流电机在为负载提供充电电流期间电池突然性的断开所导致。并且,车辆“借电”(jump starting,又称跳线跨接启动)也有可能因使用串联堆积式电池而导致一种过压状态。其它的瞬变可能源于点火系统的噪声、继电器开启及关闭以及诸如保险丝熔断等单稳态事件。

值得庆幸的是,最为剧烈的大能量瞬变可通过核心的抑制器进行处理;典型的抑制器被置于重要的(以及昂贵的)组件附近,具有高阻抗的通路连接到卸放源。车载的抑制器必须能够耐受峰值功率耗散超过1,500W的重复性负载卸放,并限制电池电源轨偏移小于±40V。

附加的保护电路常常是必需的,可更为有效的限制电压导轨。二极管反极性串行连接到附加的负载电路,可以分离电源导轨并有效地隔断反相的电压尖峰。设计人员将瞬变箝位至低于+40V的结论取决于电路所接受的电压。该电压接受功率的DC/DC稳压器必须能够耐受至少+40V的电压,以防止功率元件及控制电路产生过压(overstressing)。绝大多数的现代脉宽调制控制器(PWM)均能耐受超过+40V的电压,而无需损失任何有益的特性(例如同步运作,可能是满足设计某些特定目标的条件)。

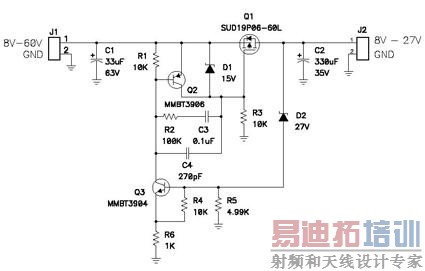

限流电阻及箝位齐纳二极管典型地应用于小负载电流电路,一般来说低于0.1A,以确保串联电阻不产生过多的能量损耗。下图所描绘的电路提供了一个箝位输入电压至所期望的最大电压值的方法,同时仍可保持较大的电流输出能力并使得“典型的”非瞬变运转时的电路损耗最小化。

此电压箝位电路限制输出电压至27V

上图所示的电路设计限制输出电压至27V,由齐纳二极管D2限定。该输出电压旨在为绝对额定最大值为30V的DC/DC转换器提供电源。对于12V静态电压的输入,晶体管Q2处于“关闭”状态,电阻R3将P道沟FET管Q1的门极下拉至地,开启Q1。

输入电压高于3V时,Q1开始引导电流,并至少增强至4.5V。穿过Q1所引起的电压降非常低,其值取决于额定的Rds-on及输出负载电流。例如,3A的负载所引起的Q1两端的电压降仅为0.16V,而此时的输入为14V。二极管D1用于保护FET Q1,避免在高输入电压状态下Q1的门极—源极电压超过最大限额20V。对于输入电压不超过20V的设计,D1可以免去。

由于输入电压的升高,输出也将随之升高直至某数值,齐纳二极管D2击穿并开始引导电流。此时,输出电压被钳位为齐纳二极管D2、电阻R4、R6的电压之和。而R4及R6两端的总电压仅为0.6V左右。

晶体管Q3采用了射极跟随(emitter follower)的配置,因而电流增益近乎为1。由于集极电流流经Q3,使Q2产生偏置,并开始降低FET Q1的门极—源极电压。由于FET Q1对流经其本身的、过高的输入到输出电压的抑制(起了线性稳压器的作用),使得输出电压被保持在了27.6V。随着输入电压的增加,输出电压不再增加,因为额外的电流将流经齐纳二极管D2并迫使Q2降低Q1的门极—源极驱动电压。该闭环反馈防止了输出电压继续变化。

[p]

系统稳定性

当涉及到负反馈闭环控制系统之时,稳定性对于可预测的、可靠的运行是至关重要的。闭环增益及相位裕度(phase margin)决定了系统对外部干扰响应的优良程度,例如输入电压的改变。

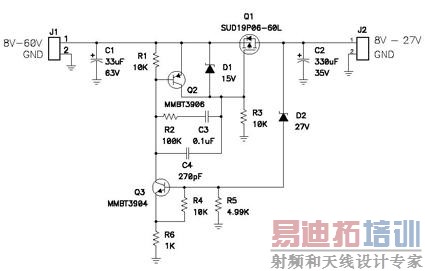

晶体管Q3旨在配置作为单位增益以防止反馈通路引入过量的增益。晶体管Q2提供了等于其β值的电流增益,其典型值的范围处于50至200之间。FET Q1同样提供了等于其跨导乘上输出负载阻抗的增益。该增益也处于200的量级。总的闭环直流增益由上述两增益项决定,数值巨大,超过80dB。负载阻抗及输出电容所引起的传递函数极点使得FET Q1的增益在大于50Hz时以-1的斜率(或-20dB/十倍程[decade])滚降。输出电容的等效串联电阻(ESR)同样增加了一个零点,其位置由ESR及其自身电容值确定。从而使得输出的频率响应平坦带超过了6kHz。精细的修整Q2增益的频率响应可给出一个可接受的总体闭环频率响应。

由R2、C3以及C4所组成的补偿网络提供了所需的频率修整。当未达到串联的R2及C3所引入的零点之前,Q2的增益以-1的斜率从直流(零频)点开始下降。该零点的位置被调整至50Hz附近。并联的R2及C4所引入的极点被调整至6kHz的零点位置。此时,总体的有效环路增益保持了-1的斜率,直至越过单位增益,如下图所示。示例的电路展示了最少70kHz的带宽,可支持大于0.5A的负载电流,在几乎所有的负载状态下都拥有90度的相位裕度。由于负载阻抗及输出电容设定了一个低频的极点,因此带宽将随负载阻抗的升高而降低。

环路增益在宽范围负载内保持稳定(负相)

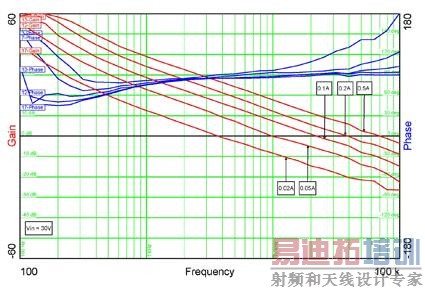

下图显示了在较大的不规则输入电压瞬变状态下输出电压的响应。一旦输入电压超过齐纳二极管D2额定的27V,输出电压将箝位并很好的抑制输入电压的改变。

输出电压箝位于所期望的电平(如红线所示)

[p]

为防止FET Q1过载,需考虑多个重要的因素。加载在Q1上的电压、电流及功率都必须保持在器件的安全运转区域(SOA)曲线之内。大负载及横跨Q1的大电压降(在持续的保持过压状态下)将使器件达到其极限。FET可能消耗非常大的功率,且器件有可能无法在如此短的时间内将热量有效的驱散,从而导致FET因超出SOA曲线区而失效。

并且,如果输入电压瞬变具有很高的转换速率,而输入电压源所串联的阻抗又很小或近乎为零,则有可能产生非常高的峰值输入电流,从而也有可能使Q1超出SOA曲线区。因此需要在输入端串联适当量的阻抗以限制流经Q1的峰值输入浪涌电流。降低输入电压上升的速率同样有助于限制输入电流的峰值。

结论

上面所述的输入箝位电路提供了一个低成本的方法以箝位输出电压至一个安全的电平,防止可能的过压状态在低电压电路出现。该电路可通过设定输出箝位电压及电容(以适用于任意负载)并随后调节控制环路,轻松的实现调整。在典型的输入状态下,传输单元的前向压降非常低,可实现比使用线性稳压器所能达到的更低的功率损耗及更高的效率。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...