- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

保证65nm节点低功耗设计的成功

电源管理的终极目标是在将价值十亿美元的产品投放市场的同时,实现最低功耗、最佳时序和最小面积。对用采用90和65nm节点制造的无线、移动和消费类IC来说,情况尤其如此。这些设计的最大挑战是在不牺牲性能的前提下,提供具有最佳能效比的器件。所以,应该结合采用哪些低功耗技术呢?另外,工程师在设计中如何在高性能和低功耗间取得最佳平衡呢?

右文列举的是源自90和65nm节点低功耗设计的一些经验与诀窍。遵循这些经验与诀窍,有助于取得低功耗设计的成功。

应该

1. 根据逻辑层和逻辑域的不同,在寄存器传输级划分多电压设计。将时钟作为独立同步域。编写模块级隔离单元(isolation cell)和电平转换器,以确保对电源控制对列成功进行形式验证和仿真。若需对物理模块进行硬化,就要提供设计约束,同时也要具备连接至一些必要的模块端口的能力。

2. 在寄存器传输级(RTL)综合时,不仅在逻辑链路而且还在时钟树实现时钟门控,以降低动态功耗,并减小面积。

3. 将电平转换器安放在靠近各电压域边界的地方,以简化第二级电源回路的走线,并保证当有电压交叉时,所有电平转换器同时动作。

4. 在布局时,灵活地布置簇及寄存器。簇寄存器省电;将这些寄存器分散开来,可提升性能。

5. 采用多阈值库,尽早对泄漏进行优化。在寄存器传输级综合时,要考虑泄漏功耗。

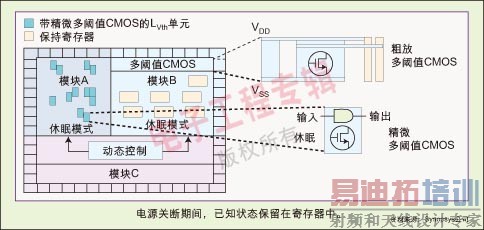

6. 尽量采用各种技术来关断激活模块,如隔离单元、状态保持寄存器、电源门控单元、多阈值(MT)CMOS单元和“常开”缓冲器。

7. 分阶段唤醒休眠模块。突然启动会产生浪涌电流,从而降低可靠性。

8. 在精微与粗放的多阈值CMOS之间进行权衡取舍。精微工艺开关速度快,粗放工艺能更好地减小漏电流。

9. 突出最关键的时序拐点。

不应该

1. 对时钟门控投入过多。优化的低功耗时钟树实现必须考虑时序、斜率、插入延时、区域及阻塞、以及动态和泄漏功耗。某些设计师仅注重其中一两个要求,所以其最终得到设计会显得稍为逊色。

2. 忘记电压感知扫描插入的可测试性设计。在可测试性设计过程中,不允许扫描链穿越不同电压岛。自适应电压扫描技术也能将阻塞和电平转换器的数量减至最小。

3. 对签核(signoff)时序、串扰和功率分析估计不足。功率的最坏拐点通常与时序的最坏(或最好)拐点不同,不同操作模式下的功耗会有很大差异。这就是为什么需采用利用许多独立拐点同时分析全部模式的多模式/多拐点技术从而扩展签核流程的原因。

4. 在泄漏优化过程中利用高阈值单元时走极端。若在物理综合时,将时序关键范围设定得过于紧凑,由于工艺变异的原因,许多非关键时序路径反倒变成关键时序路径。另外,从自动测试程序生成的角度讲,关键时序路径越多,按速(at-speed)测试模式就越多,从而抬高了测试成本。

5. 迷醉于“保持-翻转触发器”。保持寄存器(也称作球触发器)在单一库单元中,包括一个触发器和一个保持锁存器,这意味着保持寄存器一般比标准寄存器体积大。综合工具必须选定哪个寄存器将被选择性地替换为离保持寄存器最近的寄存器,以将泄漏损失降至最低,且不加大休眠通路及信号的面积,及降低其可布线性(routability)。

图:电源关断期间,已知状态保留在寄存器中

作者:Tom Chau

RTL至GDS流及方法学应用工程部门总监

Cheng Shi

低功耗与可靠性产品应用工程总监

Synopsys公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电源新品撷英

下一篇:五类主要线性稳压器的优缺点及其应用领域分析