- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

在RTL设计阶段之前尽早规划,实现IC功耗的降低

过去,面积与性能是IC设计的主要驱动因素,但如今,将功耗降到最低已经日益成为IC设计的首要目标,而因功耗问题造成的设计失败或设计返工也越来越多。因此,在设计之初就需要一种面向低功耗设计的一致性方法学,以此将计算、通信与存储功耗都考虑在内。

CMOS逻辑电路的动态功耗通常是由电容性负载的开关来决定的。这可以通过公式P=A×f×C×V2来估算,其中C代表电容,V是电压,f是频率,A是每个时钟周期开关的次数。传统上,许多降低功耗的技巧集中在将其中一个或多个因子的值降到最小。而随着IC特征尺寸的减小,漏电流的重要性变得更高,需要给与更多考虑。

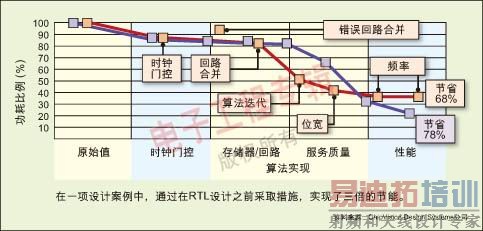

然而,能够做的最大改进是在RTL设计之前。所以,最重要的建议就是要明智地选择你的努力方向。门级优化固然需要,但要保证你在设计周期之初,就已在全局和系统级解决了有关功耗的所有重要问题。

应该

在设计流程的早期就处理漏电流问题。漏电流似乎是一个低级别问题,但最有效的漏电流降低技巧都涉及到利用空闲状态,即在不工作期间切断电源或增加阈值电压。这些空闲周期在更高的提取层次能被最佳识别。

|

图2: |

尽早地考虑系统的动态行为。动态行为决定了系统的功耗特征。数据通路的功耗极大地取决于正在发生的数据流的相互关系。在实际设计过程中,这意味着尽早实现有仿真能力的描述。

有意识地将功耗与性能、面积、服务质量(QoS)进行折衷考虑。由于动态功耗与频率呈现线性关系,并且与电压呈平方关系,所以要首先考虑就地尽可能地减小这些参数,只要处理要求允许即可。这可能要求引入新的电压和时钟域。你也可以考虑像流水线和并行这类技术来补偿损失的性能。

采用变化工作负荷的方法。关闭设计中所有不工作的部分,或者使其进入低性能、低功耗状态,这是一个好的想法。时钟门控技术已经成为通用的低功耗技术,但是你也应该考虑更进一步,采用动态降低时钟频率和/或电源电压的技术。

在提取的所有级别都要考虑功耗问题。尽量在RTL设计之前就稳固地掌握你的功耗问题,因为此时功耗节省潜力大出许多,并且与后续更低的级别上相比,能更容易实现设计变更。在整个设计周期中都需要注意所涉及的功耗问题。

不应该

使速度尽可能的慢。这一贯是一条没什么价值的建议,但如今,降低速度不再是一件不必耗费脑筋的事,因为通过漏电流消耗的能量取决于这个过程的时间长度。随着漏电流变得更加重要,“运行速度更快以及睡眠时间更长”可能是更好的策略。

忽略系统极其重要的部分。数据通路、控制逻辑、处理器软件、模拟模块、存储器和总线——所有这些都对整体功率预算有重要影响。

盲目行事。每项设计都有其自身的关键功耗问题。如对某一项设计而言,时钟可能对功耗问题很关键;对下一项设计而言,则可能是存储器;而对另一项,可能是乘法器。不要仅仅作假设,你可能假设错了。

动作迟缓。由于设计越来越具体,节省功耗的潜力逐渐缩小。你能在RTL设计之前轻易地成倍降低功耗因子,但是降低同样程度的功耗在门级将是非常困难的。

指望存在一种“万金油”。和我们EDA供应商一样,不存在单一的技术能够解决设计中的所有功耗问题。这些问题极大地依赖于设计本身、设计的实现方式以及环境。

作者:Eike Schmidt

首席架构师

德国ChipVision Design Systems公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:网站论坛有关微控制器的问答精粹

下一篇:具有热意识的设计可产生高质量的芯片