- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用Alchemy Au1200处理器设计便携式媒体播放器

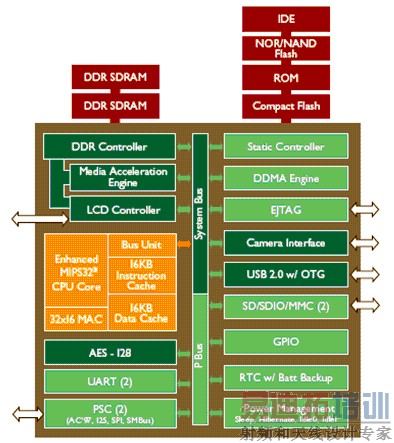

Originally developed by AMD, and now available from RMI (a company founded by AMD's former COO), the Alchemy Au1200 processor is a highly integrated system-on-a-chip (SoC) product built expressly for PMPs equipped with high-performance video capabilities, including long run time and support for multiple codecs without transcoding.

The growing wave of premium digital video content has challenged PMP designers and manufacturers to create devices with more versatile, higher power video capabilities while maintaining form factor and other capabilities pushing the explosion of PMP's into the market. Consumer electronics market research firm In-Stat forecasts that worldwide PMP shipments will reach 5 million units by the end of 2006 , while senior analyst Chris Crotty of iSuppli recently stated that the market for PMP semiconductors is expected to double to $6.4 billion in the next three years.

These trends strongly influenced the design goals behind the RMI Alchemy Au1200 processor, a highly integrated system-on-a-chip (SoC) product built expressly to meet the requirements of a PMP equipped with high-performance video capabilities. For developers and original equipment manufacturers (OEMs) looking to build a PMP around the RMI Alchemy Au1200 processor, a closer look at this processor's characteristics alongside one of the PMP reference designs available from RMI may be helpful in mapping out an overall device approach.

Design considerations and video performance

One of the biggest challenges facing PMP designers today is delivering high-quality video playback while minimizing power consumption to enable long playback times. The Alchemy Au1200 has addressed this problem with the integrated Media Acceleration Engine (MAE) architecture. The MAE not only enables devices to play native content from all popular formats, but is also able to deliver that content at rates that are competitive with mainstream entertainment systems. The Au1200 can play native video content that is based on MPEG (1, 2 and 4), DivX, Windows Media (WMV9/VC-1) and XviD. While other devices in this market may compromise on screen sizes and frame rates, the MAE enables the Au1200 to deliver full D1 resolution video (720X480) at 30 frames-per-second, and data rates up to 10Mbps for substantially lower power than would be required to drive a QVGA (320x480) mobile panel.

![]()

Table 1: Video format and resolution

Video decompression and decoding

In designing a PMP that can play back premium video content at DVD-quality resolution, one of the major challenges is meeting the computational demands of decoding high-quality MPEG/WMV video content. With most current devices, native D1 (720x480 resolution) video content must be transcoded to a lower bit-rate and resolution because the PMP either lacks sufficient processing resources or is too power-hungry to play the files at full size and rate. Downloading video content onto a PC for transcoding can take as long as the playback time of the file itself, which diminishes the user experience.

The RMI Alchemy Au1200 processor addresses this need by providing support of common digital media codecs -- including MPEG (1,2 and 4) DivX and WMV9 -- and delivering full D1 resolution without the need to transcode content. Mated on a single chip with the MIPS32 processor core, the MAE performs power-intensive tasks such as video decoding, scaling, color space conversion and filtering in hardware, thus freeing the processor core to handle user interface functions, audio processing and other demands. The integrated MAE is a low-power alternative to using a DSP to decode the video content. The MAE spares developers from having to either invest significant time in DSP programming or added expense in hiring a 3rd party for this task.

Memory architecture

Employing a single-chip solution also sidesteps a number of cost and engineering problems inherent in the multiple-memory controller designs that use a DSP/CPU combination, such as the need for separate memory banks to handle DSP decoding and application processing functions. With the RMI Alchemy Au1200 processor's unified memory architecture, PMP developers can use up to 512MB 2.5V DDR1, 1.8V DDR2, or Mobile DDR memory at speeds up to 500MHz (DDR2) in 16-bit or 32-bit implementations. Those seeking to achieve lower power consumption in their devices might choose 1.8V DDR2 or Mobile DDR, while the 32-bit implementation option can satisfy a higher-end PMP model's appetite for video and graphics data.

Where cost considerations outweigh the need for large memory bandwidth, the 16-bit DDR avenue is open as well. The availability of processor speeds up to 500MHz gives a developer the flexibility to build additional capabilities -- such as Wi-Fi, GPS and digital media broadcast -- into the PMP design.

Direct Memory Access (DMA) control

To support the large volume of memory transfers typically required in multi-function PMP designs, while keeping the physical area of the processor small, the RMI Alchemy Au1200 processor's descriptor-based direct memory access (DBDMA) controller autonomously manages multiple sequential data transfers via a linked list of descriptors. This design provides a developer with 16 DMA channels, arbitrated as high- and low-priority pools, that can be addressed using round-robin or weighted priority techniques. The DBDMA controller also augments DMA transfers with operating modes and data management strategies that are tailored to tasks as well as to a PMP's consumer-centric use model.

This includes an increment mode that supports the transfer of any byte count from any byte alignment, and a decrement mode that supports the requirement of Secure Digital (SD) devices for backwards data feed without using buffer memory to perform the data reversal. The DBDMA also supports conditional data transfers using compare-and-branch and subroutine descriptors, which enable branching to commonly used descriptors with automatic return and the ability to poll an on-chip or off-chip register.

Figure 1: RMI Alchemy Au1200 block diagram

Camera interface

To meet consumers' demand for imaging capabilities in a PMP, developers can employ the RMI Alchemy Au1200 processor's Camera Interface Module (CIM), which supports data input modes for CCD/CMOS sensors and CCIR656. Both of these formats are served by the MAE, which provides Bayer pattern demosaic for CCD/CMOS along with scaling, color space conversion and filtering for all CIM parallel operating modes. CIM input data is moved into memory, unchanged, via a Raw Data mode.

LCD control

Developers have full 32-bit aRGB capabilities in each of four prioritized overlay windows using the LCD controller in the RMI Alchemy Au1200 processor. This enables overlay window repositioning with no frame buffer modification as well as gamma correction for each window to match the video display with graphics. A global background color helps the developer aesthetically unify display panel contents with minimal demands on processing power. The controller's 8Kb palette RAM frame buffer complements a PMP's idle mode in supporting a low-power system information display, such as alarm times.

Scalability and versatility factors

The RMI Alchemy Au1200 processor's static bus facilitates added versatility and scalability in PMP designs by accommodating a range of devices with interface similarities -- such as RAM, ROM, NOR flash, PCMCIA/CF, IDE and NAND flash -- as well as supporting 10/100 Ethernet connectivity. Developers can further scale their designs with the processor's on-chip interface to the IDE drive, which supports simple DMA mode, PIO mode and multi-mode DMA for delivering video and audio data to the PMP.

AES encryption/decryption

Given the necessity for owners of copyrighted digital content such as movies, music videos and televised programming to protect their intellectual property from pirating, PMPs must also be able to recognize and enforce the digital rights management (DRM) security measures built into this content en route to enabling its playback. These capabilities are handled by the RMI Alchemy Au1200 processor's AES Cryptography Engine. It supports the U.S. government's 128-bit Advanced Encryption Standard (AES) in ECB, CBC, CFB and OFB modes, and uses the data transfer capabilities of the DBDMA Controller to augment encryption/decryption functions. Since decryption is handled in on-chip hardware, rather than in software, PMP developers can avoid slowing down the application processor with this function thus applying processing power to other device requirements. In PMP designs where power vs. throughput is a key consideration, the AES Cryptography Engine offers four bandwidth choices: 44, 22, 11 and 5.5 Mbps operation.

Power management

In addition to the other low-power attributes described previously, the RMI Alchemy Au1200 processor supports power conservation in the PMP use model with the following modes:

·Sleep Mode is a low-power state in which memory contents can be maintained by invoking DDR self-refresh. Developers can optimize this state for lowest power consumption by disabling the internal power supply (VDDI) during sleep. They also can program the time out of sleep in VDDI rise-time increments of 5, 20 and 100 milliseconds, or keep the VDDI active for faster wake-up.

·Hibernate Mode allows the system to be powered off while a separate battery back-up on XPWR32 keeps the time-of-year clock alive to allow for a periodic wakeup mechanism in the PMP device.

The RMI Alchemy Au1200 processor also supports DDR memory power management for DDR1 and DDR2 in three configurable power-down modes that occur automatically, so there is no software interaction required from the PMP.

The DDR controller includes the following options during idle periods: Automatically drive the clock-enable signal (DCKE) low Automatically pre-charge on idle and drive DCKE low, putting the DDR into "power-down" mode with all DDR banks closed Drive DCKE low and wait for a specified idle time to precharge and drive DCKE low.

The LCD controller's 8Kb palette RAM frame buffer, mentioned earlier, can be loaded with low-resolution images to support PMP operation in power-saving modes. This will enable refreshes to occur out of palette RAM while DDR is put in self-refresh, thereby reducing power consumption while still allowing frame buffer access.

Anatomy of a PMP design

RMI supports device manufacturers' need for differentiation in their PMP designs by providing numerous development tools to streamline the process and reduce the design cycle. Development platforms, SDKs and reference designs from RMI, combined with third-party products ranging from companion devices to turn-key designs provided by RMI partners, deliver the basic functionality of the PMP as well as additional features to jump-start a specific product definition.

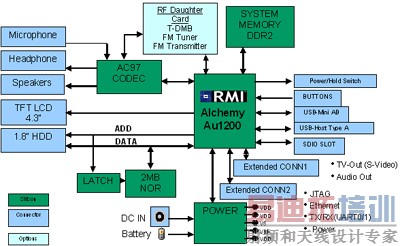

Designed and developed in China and in Korea, the Au1200 PMP reference design delivers an extensible, "go-to-market" PMP platform. This helps free OEMs to focus on delivering their specific market differentiation while also maintaining price points required to be viable in the cost-sensitive consumer electronics market.

Figure 2: Au1200 PMP Reference design block diagram

The PMP reference design offered by RMI supplements the DBAu1200 development board and SDKs, which provide developers the basic development environment for RMI's Alchemy Au1200 designs. These tools provide the environment in which to develop, bring up and debug system software and integrated peripherals --essential steps in the successful development of a PMP.

Cost vs. performance considerations

Cost reduction is one of the primary design challenges that PMP developers will encounter. Consumer products are constantly under pressure to increase functionality while reducing cost. Most companies agree the PMP market increases significantly as prices drop below the $400 and $300 retail price points. SOC integration and design simplification are two of the most effective ways to reduce system costs.

In addition to integrating all of the base functionality a PMP requires, developers can simplify their PMP design with the Au1200 by eliminating the cost and complexity of separate programming and memory for the graphics controller and video acceleration. In addition, the processor provides a glueless interface to standard components such as Flash memory and hard disk drives for added simplicity.

Developers can further reduce their system costs by allowing the system to boot, run and store data in a common memory subsystem. Traditional designs use separate memory types -- one for boot-up and the operating system, and another dedicated to the memory space for applications and data storage. System developers have long desired to use a single type of flash memory in their design. This effort has posed challenges in the past due to performance issues and memory reliability of the technologies: NOR technology provides reliable memory for crucial functions like booting the system, while NAND provides lower cost and higher performance.

Using the Au1200 reference design, developers can solve this problem by implementing a NAND boot loader for reading a block of reliable memory during power-up and allowing the system to use the balance of the flash memory as a standard NAND flash file system.

Peripheral additions

Adding custom peripherals is another perennial concern for system designers using highly integrated SOCs. More often than not, the chip is missing a specific I/O requirement to interface to a crucial device. The design may require an integral GPS receiver that interfaces through a SPI port and a touch-screen controller that needs I2S. The Au1200 design overcomes this dilemma by including a large number of highly configurable interfaces. If a developer needs to add a serial device, the Au1200 contains two programmable serial controllers that can be configured for AC-97, I2S, SMBus or SPI.

The typical PMP today has a number of interrupt-driven controls such as screen navigation buttons; stop, play and rewind; and possibly others. A discrete design would require an external controller chip to manage more than a very small number of switches. By contrast, the Au1200 provides a large number of general purpose I/O (GPIO) pins that can support external events like control buttons and power switches without the need for an additional chip.

There are countless peripherals that a system developer might need to interface with the Au1200. Many devices can be supported through standard interfaces like USB and SDIO. Using a standard interface cuts development time by providing standard drivers and software stacks. Complex solutions can be connected through the Au1200 "static bus" interface. As with USB, SDIO and others, the static bus is designed to be a flexible interface for connecting devices that need full access to the internal data bus. Examples include 3D graphics, video encoders or TV-out solutions.

Complementary products and support

The Au1200 has an established infrastructure of tools, design aids and development assistance, provided by industry-leading companies that understand the pivotal role this device plays in the exploding PMP market. Products and services available from RMI range from simple driver support to a complete system design. For example, RMI currently has multiple partners providing solutions to decode the MPEG-4, part 10 AVC (H.26 ) video format and partners delivering finished goods, ready for resale into the market.

In designing the RMI Alchemy Au1200 processor to specifically meet the demands of PMP use models, RMI has sought to emphasize high-performance processing power, single memory architecture, glue-less interfaces, flexible I/O's and standard connectivity. As an alternative to typical multi-processor designs, the Au1200 can help PMP developers optimally balance the characteristics of low power consumption and high-quality video/audio processing in a single chip.

For the latest information on the selection of tools and partners who support the Alchemy Au1200, visit the RMI Alchemy developer Web site at http://www.razamicro.com/products_alchemy/

By Rob Oliver, Director of Marketing, and Ed WhiteManager of Business Development, Raza Microelectronics Inc.

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:面向以太网电源的高功率设计分析

下一篇:如何延长基于微控制器设计的电池寿命?