- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电源完整性问题以及改进思路分析-Ⅰ

电源完整性概念

简单地讲,电源完整性是指特定电源与理想状态的接近程度,具体取决于电源的自然特性。对于家用设备电源来说,主要关心的是电压幅度和频率,即不管附近的负荷和用电限制如何变化,电压幅度和频率能够保持多大的稳定性。我们可能都会注意到,当大型空调或电冰箱压缩机启动时灯会变暗,这就是电源完整性的劣化现象。

集成电路没有什么不同?虽然它们一般使用几伏到1伏的直流电源。通过了解IC的部分电路在打开和关闭以及增加和减少功能时,在这一恒定电压上产生的降压和过冲,就能很好地理解IC的电源完整性。对于优秀的电源完整性而言,重要的是供电电压差值中发生的降压和过冲或瞬时(和静态)变化保持在很小的范围内,比如标称值的5%,从而使集成电路保持可预测的性能。

IC电源网格中供电电压变化的主要成份是IR压降和L×(di/dt),虽然其他噪声成份有时也会占主导地位,比如传播和反射噪声以及谐振噪声等。目前EDA行业的分析工具采用IR压降变异方法来分析集成电路各个部分的电压下降。随着工艺尺寸的不断缩小,相对重要的电源完整性噪声成份也在快速变化,主要是因为目前的大多数集成电路通过含有电路开关电流的二进制运算发挥功能,并与时钟信号同步。随着工艺向纳米级发展,这些开关速度将迅速提高,相应就提高了片上的di/dt,因此现在必须检查‘总的电源完整性’,包括L×(di/dt)和其他电磁效应,而不仅只是IR压降或它的派生因素。

环路电感、L×(di/dt)和工艺的影响

电源完整性研究表明,从封装电容到处理器的环路电感需要按工艺变化系数的3次至5次方变化才能使改进工艺与前代工艺保持相同的电源完整性。在本例中,环路电感确定了从封装电容到处理器要求的瞬时电荷的响应时延,以及处理器供电电压的相应压降。

同样,片上环路电感决定了从芯片或封装区域中存储的电荷被放电到需要瞬时充电区域的响应延时,这些区域如快速开关的功能块或同时受时钟触发的寄存器组、触发器或大量逻辑门。环路电感L与电流上升速率di/dt也将产生一个电压降——L×(di/dt),这个压降会叠加到由电源分配网络中线电阻引起的任何一个瞬时电压降上。因此有必要通过试验来判断连续的工艺升级如何影响后一代产品的L×(di/dt)电压降(噪声)。为了完成这个试验,考虑到工艺升级、获取的好处和最终结果,根据目前的行业趋势做出以下假设:

• 单位面积的电容Ca,调整比例为 ,大约(1/0.7),其中0.7是典型的制造工艺导致的缩放系数(95nm到65、45、32等),

,大约(1/0.7),其中0.7是典型的制造工艺导致的缩放系数(95nm到65、45、32等),

• 工作电压调整比例为 ,减少量仅约为16%,

,减少量仅约为16%,

• 频率调整比例为 ,可以有40%的改进。

,可以有40%的改进。

• 芯片面积调整比例为 ,只减少30%,而不是50%,这表明为了提高缩放后工艺的性能而集成了另外的电路。

,只减少30%,而不是50%,这表明为了提高缩放后工艺的性能而集成了另外的电路。

在上述假设下,参考“两次缩放的根”可以得到有效功率,此时假设等式αCV2ƒ在工艺缩放前后保持不变。在这种缩放情况中,硅片面积减少了,从而减少了成本,提高了频率和集成度,并增加了性能,同时功率损失保持不变(假设有更好的漏电流控制技术使漏电功率保持不变),从而使经济效益仍然遵循摩尔定律。

• 在上述缩放条件下,平均有效电流的缩放系数为电压缩放系数的倒数,即 ,因为功率保持不变。

,因为功率保持不变。

• 由于频率缩放系数为 ,因此di/dt缩放系数为

,因此di/dt缩放系数为 。

。

• 另外,由于芯片面积缩放系数为 ,因此每边的缩放系数(假设是正方形芯片)为

,因此每边的缩放系数(假设是正方形芯片)为 。

。

• 如果每边尺寸更小,并假设电源总线用相同的宽度和间距绘制,那么每条边的并行总线数量减少 ,或有效电感增加

,或有效电感增加 。

。

将工艺缩放后的该芯片中的L和di/dt相乘可以得到:

• L×(di/dt)缩放倍数为 ,或2倍。

,或2倍。

上述这些计算显然是高度简化的,缩放系数也很不精确,但趋势是肯定的。随着向更精细工艺尺寸的演进,开关边沿速率将越来越快,而为了节省有效功率降低和漏电功耗,器件越来越小,工作电压也越来越低。虽然功耗可能保持不变,甚至有望减小,但更快的工艺要求更快的电荷传送,或通过更少的可用资源(如金属电源线)和更小的电容提供更大的电流,从而导致更高的电压降。

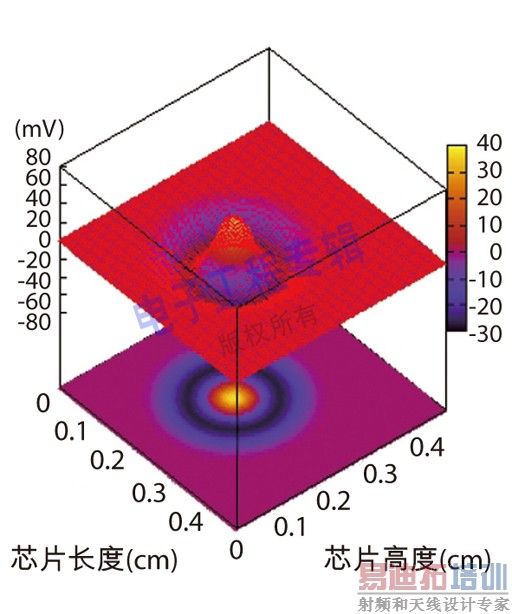

从这个简单的导出公式可以看出,每一次工艺升级都会使L×(di/dt)噪声加倍,从而对支持元件提出更高的要求,详见参考文献[4],虽然功率不变。例如L×(di/dt)或感应噪声导致的电源网络噪声在180nm工艺时为9mv数量级。根据导出趋势,45nm节点将产生16倍之多的感应噪声,或约144mv,约是电源微分值的15%,或3倍的允许最大噪声。学术研究也表明了相同的趋势,即感应噪声随上升时间呈2次方增加,这个上升时间取决于电源分配网格的PEEC建模。IR压降工具可能完全遗漏这种电源完整性。

芯片或模块设计师会发现,更先进的工艺将增加平均供电电流,他们必须在电源分配网格设计方面做出艰难的选择。有时需要依靠被过度吹捧的‘完全拷贝’方法,这时设计师可以将相同部分的金属资源分配给电源分配网格,就像前代芯片那样(这样做可以起作用,但必须正确完成!)。就像我们前面推导的那样,缩放后芯片中的瞬时感应噪声数量将增加一倍。

在本文的第二部分(见下期)将详细介绍电源完整性设计中的最优IR压降方法,以及片上电感对电源完整性所带来的影响。另外,还将详细介绍像45nm这类更新的工艺节点上,电源完整性经常存在的问题(例如呈2次方或指数式增长的L×(di/dt)噪声,能够帮助IP内核和芯片设计师快速仿真和分析物理设计的全面电源完整性技术和EDA工具的严重缺乏,无法清楚地理解芯片电源完整性的各个方面),这些问题共同导致了器件良率的下降,最后将讨论针对上述这些问题的可能解决方法。

作者:

Raj Nair

专家顾问

Anasim公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...