- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电源完整性问题以及改进思路分析-Ⅱ

IR压降与片上电感

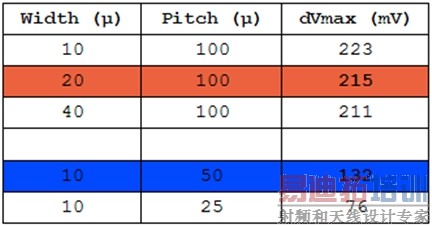

那些更负责任的设计师会遵循最优的IR压降方法,并推导出平均芯片电流会增加,因此需要更多的电源网格金属。设计师面临着两种选择,一种是增加电源总线的数量,这意味着减少总线间距,一种是增加总线中金属走线的宽度,但受布线要求的约束。通常设计师会选择增加金属走线宽度,而不选择减少总线间距而使布线更加拥挤,并利用IR压降工具来改善噪声。遗憾的是,这种解决方案很不实用,特别是当主要的噪声来源是L×(di/dt)时,因为增加金属走线宽度和总线间的轴向隔离度对改善噪声的作用非常有限,甚至会出现负面影响。除此之外,高频电流通常被限制在电源总线的低电感区域。

上述两种都存在缺陷的方法有一个共同的因素,即它们异乎寻常地依赖于先前的知识和经验,而不是依靠全面的验证来弥补方法的不足。可以预见的是,这种不适当的依赖性肯定会降低工作质量甚至最终结果,就像包含许多不确定性的金融投资那样,过去的业绩并不能保证未来结果。这种业界惯性致使人们无法转向全面的电源完整性分析,主要是因为严重缺乏高效和精确的建模技术及EDA工具,以便对IP模块、多内核芯片和整个电源系统进行快速、全面、真正的电磁仿真。

事实上学术界的研究表明,通过在电源网格仿真中包含感应噪声可以更好地优化电源金属面积。某篇关于片上电感对电源分配网络设计的影响的论文中写道,90nm工艺的电源网格中金属面积使用率约有30%的增加或减少,在45nm工艺时通过全面的片上电源网格电感建模可以有高达60%的改进。

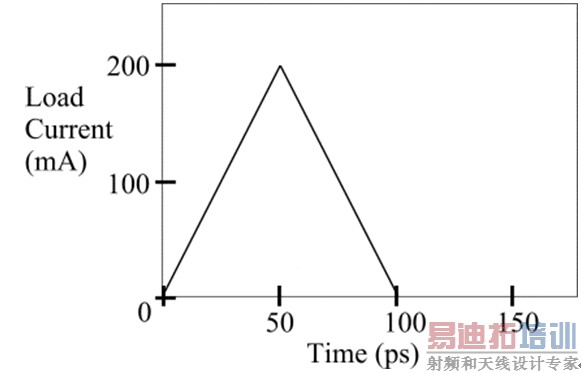

图1:用于栅噪声评估的三角形负载电流外形图。

电源完整性问题

呈2次方或指数式增长的L×(di/dt)噪声,能够帮助IP内核和芯片设计师快速仿真和分析物理设计的全面电源完整性技术和EDA工具的严重缺乏,无法清楚地理解芯片电源完整性的各个方面,SoC设计势不可挡地转向更精细的纳米级尺寸,这些因素共同导致了器件良率的下降,最终造成工艺尺寸减小的经济可行性下降。

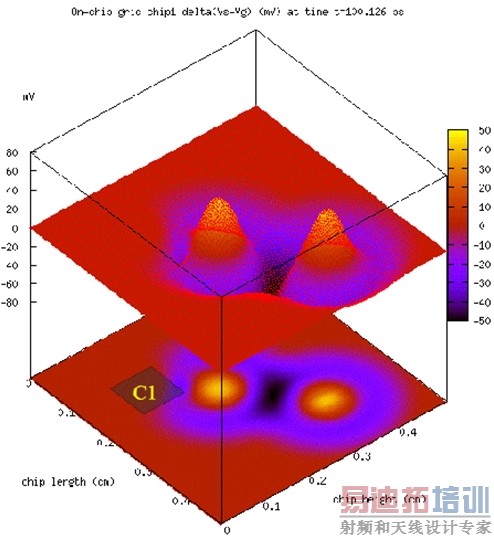

图3:来自两个源的电源噪声叠加(线宽10μm,间距50μm)。

采用纳米级工艺的半导体器件变异以及为了降低能耗而采用越来越低的工作电压进一步加剧了良率问题。低功率和低能耗设计并不等同于没有电源完整性问题。事实上刚好相反,低能耗设计将引入额外的复杂性,如以不是十分显性的方式影响电源完整性的电源选通(Power Gating)。工作电压只有零点几伏的实用性芯片要想达到合理的集成度和性能,需要对它们电源上允许的很窄带宽的噪声进行深入地理解和全面的验证。另外一种方法是将所有已经确定的面积和功效数字逻辑电路转换成采用纳米级工艺,并且特别能容忍噪声,可能差分的电流模式电路。

由于在全面电源完整性方面缺少足够的先进方法和高效工具,我们似乎注定要面对严重的工艺缩减障碍,虽然可能不是比电源障碍更严重。

表1:不同电源栅尺寸对应的最大电压降。

潜在的解决方案途径

因此随着SoC设计向65和45nm节点的纵深发展,必须深刻领会影响IC电源完整性的所有因素。在电源分配网络中包含的所有电磁效应现在已是关键要求,可以通过采用高层抽象和物理仿真(如Anasim公司的π-fp)等工具加以满足。使用这种工具对目前的设计流程进行简单直接的修改措施如下:

* 在架构阶段就开始针对电源完整性的底层规划。

* 采用低电感、对称、IP内核和全局电源网络综合。

* 采用真正的电磁仿真优化电源网络尺寸,并确定最初的片上去耦电容策略。

* 优化底层规划布局以减少电源的‘总噪声’带宽;减少工作电压,并同时满足时序/性能要求。

* 利用静态IR下降仿真检查物理设计中的任何‘热点’及电迁移压力点。

* 包含系统级元件(如封装电容、供电连接等),利用改进的模块电流参数再次运行真正的电磁、动态噪声分析,充分利用互连和去耦电容资源。

IP内核和全芯片/SiP/系统级的真正电磁仿真验证有助于确保设计师在设计过程中深刻理解呈指数式上升的L×(di/dt)噪声及其他噪声成份。这种在全面设计和验证方面做的前端投资非常重要,可有效避免设计反复、设计的重新流片,并防止出现高出基准几个数量级的良率故障或产品故障出现。

作者:

Raj Nair

专家顾问

Anasim公司

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...