- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SoC电源管理中调节器面临的命运

SoC的供电要求越来越高,使得这种设计也越来越复杂。好在设计人员可以选择在电路板级来处理这些任务,SoC开发人员希望将电源网络组件置入到芯片中以期有所帮助。但是最终,电源设计人员仍然要做出一些很难的决定。在决定之前,他们要进行一些模拟电路仿真工作。

不断增长的需求

集成是有成本的。 SoC设计人员在其图纸上画出各种电路,这类电路都有自己的电压、噪声、排序和瞬变响应要求。移植到尺寸更小的电路上不但能够实现集成,而且还降低了供电电压。这一发展趋势也同时增大了峰值工作电流、缩小了噪声余量,使得动态电源管理越来越复杂。

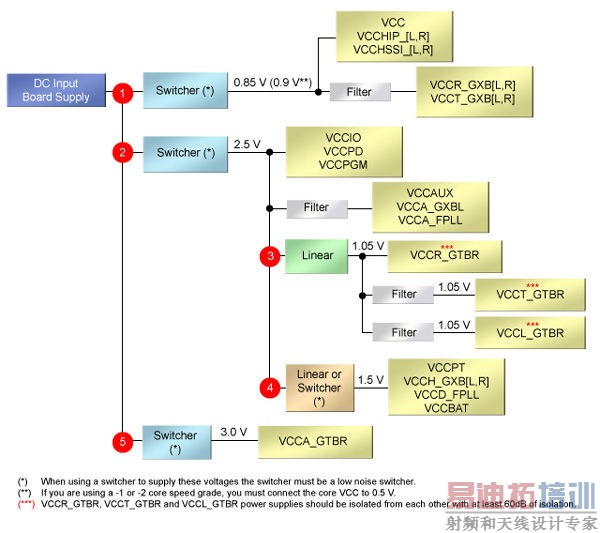

复杂度的提高最明显的结果就是SoC使用的外部电源数量迅速增加 ( 图1 ) 。例如,一片高端FPGA会有15条外部驱动的电源轨。它们都连到哪里

图1. 一片现代SoC需要很多不同的供电线路,每条线路都有自己的稳压和调理要求。

答案之一是不同的电压需求。在FinFET工艺出现之前 , 内核逻辑供电电压一直在大幅度降低 , 但在1V附近却停滞不前。而其他类电路在这方面远远落在了后面。按照工业标准, I/O单元只能使用特定的供电电压。SRAM单元需要的电压要比逻辑级稍高一些,以保证可靠的全速工作,待机时的电压要低很多。高精度模拟电路希望有较高的电压以降低抖动,提高噪声余量。这些各种各样的需求导致供电线路数量的急剧增长。

但是 , 电压数量还不是唯一的问题。某些SoC电路——特别是低噪声放大器、锁相环(PLL) ,以及物理接口等都有非常严格的供电噪声限值。即使电压相同,这些需求也导致电路无法共享同一条噪声源供电线路,例如,数字逻辑或者大电流I/O单元等。因此,需要增加低噪声电源。

非常有意思的是,增加供电线路的另一需求是来自电源管理。数字设计人员越来越多的采用了动态低功耗技术——例如,精细粒度时钟选通、随时供电选通和电压调整等,使用这类技术的电路对其供电线路瞬变响应的要求特别高。负载在微秒甚至更小的量级上变化。为能够响应来自SoC的命令,电压应不断变化。这些负载实际上可以采用不同的恒定电压源或者噪声敏感电压源。

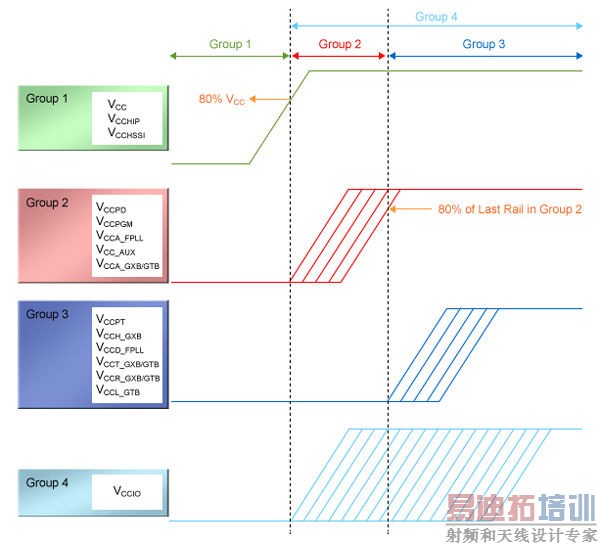

排序也需要单独的供电线路(图2) 。在很多SoC中,对上电顺序有要求——在某些情况下,对关电顺序也有要求。这种时序要求使得电路提供不同的供电线路,不然可以共享一个电源。

图2. 正如这一FPGA所示,复杂的SoC上众多的电源线,通常都有严格的上电排序要求。

[p]

找到策略

系统设计人员会面对SoC上大量不同的电源线 , 遇到棘手的问题。据Altera公司电源业务部研究员兼首席技术官Ashraf Lotfi,解决方法一般是采用某种分布式电源网络。

“一般而言,您会看到在电路板上有体积较大的调节器,对系统的12 V或者24 V进行降压,将其分配给每一个负载点调节器。为满足各种需求,您通常都会针对每一电源线提供负载点供电。 ”

由于电源线数量的快速增长,每一新设计都要求进行分析, 以减少调节器的数量。一块电路板上15条电源线还不够理想。因此,设计人员需要解决一些关键问题。在这种特殊的实现中,这些电源线的电压、噪声和排序要求能够支持它们共享一个调节器吗 如果不能,是否可以采用一条电源线,以稍微不同的电压运行,从而共享调节器——即使是以稍高的功率代价或者稍微降低一些性能 外部排序转换器能有所帮助吗

Lotfi说 , 减少了调节器数量后 , 设计人员可以把注意力转向优化调节器效率和布局。只要噪声和瞬变响应要求允许,那么,最好的起点是使用高效开关调节器,而不是线性调节器。Lotfi认为,最近的高频开关模块极大的扩展了范围,使得这类替换成为可能。

设计人员还可以针对每一调节器的要求尽量减小电路板面积。模块化结构可以在一个混合封装中实现控制器、电压参考、驱动、电源FET ,以及电感。在某些设计中,反馈补偿也含在封装中。原理上,这种集成使得设计人员不能自由的优化调节器的传送功能,以满足某种电源的特殊需求。而在实际中, Lotfi主张,需要电源设计人员提供反馈无源功能,占用较多的设计时间,增加电路板面积,从而提高灵活性,这样做是值得的。供应商可以为调节器内部组件预设最优传送函数,满足一般要求。Lotfi宣称,而且,把关键组件放到模块中,调节器供应商可以提高开关频率,提高总效率,有效的降低开关噪声,使得模块能够均衡线性调节器的噪声指标。

[p]

电网验证

无论选择分立调节器还是小型化模块、线性或者开关调节器 , 系统设计团队都面临对选择进行验证的问题 , 包括 , 调节器、外部组件的选择 , 以及布板是否能够满足SoC 的供电要求等。问题已经发展到包括更多的动态行为,还包括抗噪问题,这类验证不再偏重于根据数据资料进行计算,而是进行仿真。 Lotfi说,经验丰富的设计团队会针对整个电网进行行为仿真。这不但要有运行仿真的技巧,而且还要使用电路板上实际组件的精确模型 —— 小规模设计团队可能得不到这些数据。更简单的替代方案是,使用来自SoC供应商的详细参考设计。

但即使有最好的信息和工具, 也无法在SoC外部来解决某些供电问题。有时候,芯片设计人员不得不负责他们所开发的电路的供电问题。

片内调节

管芯电压调节的历史很长了 , 可以回溯到使用电荷泵为低成本微控制器的嵌入式EEPROM提供可编程电压。在很多情况下,其动机是降低材料成本或者便于使用:例如,微控制器应用,完全可以承受电路板上再采用一个电压调节器的成本。

便于使用一直是一个重要的动机 , 即使是非常复杂的芯片。 Altera IC设计经理Weichi Ding指出,先进的FPGA会使用管芯调节功能为配置RAM或者反向偏压电路提供电压。这类应用还不足以满足技术要求,这是因为外部电源的数量会比现在大幅度增加。

相似的, Altera Stratix V FPGA的很多电路也需要单独的调节器 , 因为 , 它们对噪声敏感 , 不能与其他电路共享调节器。这方面的例子包括PLL和物理介质附加电路(PMA) ,后者是直接连接至多GigaHertz串行I/O引脚的I/O模块。所有这些电路在Stratix V FPGA芯片上都有管芯调节器,从而减少了专门用于外部电压轨的引脚数量。

动态电压频率调整(DVFS)也能够满足片内调节的需求 , 只要您调整的足够大。在早期DVFS实现中,软件会预测模块在后面的几十毫秒中对性能的要求,命令硬件暂停操作,根据预测的新负载来调节电压和频率。例如,进入待机模式的手持式设备会完全关断其图形引擎,使CPU回到极慢的时钟,降低工作电压。这一过程虽然非常繁琐,但采用外部调节器进行设置来产生多路输出电压很容易完成它。但是由于很大的延时以及能耗,系统只适用于长期和可预测的变化。

在6月的设计自动化大会上,Intel首席工程师Tanay Karnik描述了当您暂时让DVFS粒度更精细时会发生什么。在管芯的每个处理单元上采用了粒度非常精细的DVFS后, Intel观察到处理器的功耗增大到100W ,远远高于服务器CPU 。 Intel设计人员放弃了由于操作系统原因而采用的毫秒级频率,开发的电路检查输入缓冲,根据后面几行代码来随时选择电压和频率。这意味着,有可能在十几个纳秒内改变频率和电压,而不是在毫秒量级。更快的DVFS意味着,芯片能够更好的满足每一模块的处理能耗需求。但这也对调节器的要求提高了,仅有外部调节器不能满足需求。

[p]

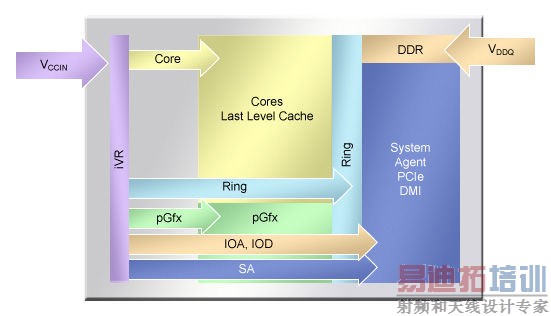

Karnik说 , 为达到这一水平的动态响应, Haswell等Intel芯片使用了可编程管芯线性调节器(图3) 。在处理器固有的数字CMOS中实现这些模块,把2.4 V基本电压降低到可选的输出范围内,在0.6-1.8 V之间,步长是12.5 mV。调节器能够以100 MHz的频率改变电压,摆率达到了令人吃惊的100 A/ns,可跟踪电源和时钟选通数字模块产生的极大的负载变化。毫无疑问,如果调节器控制环只有一两厘米的电路板走线和引线框,是不可能实现这类性能的。

图3. 对Intel Haswell芯片电源分配网络的高层描述,显示了内部电压调节器提供了不同的模块。

Karnik提醒说,采用这类设计并不是出于谨慎的目的。Intel选择的实现方法采用了管芯电感,因此, Intel必须在其后端线路处理流程中引入磁体材料。对于设计团队,对调节器网络建模的难度非常大,这会有很多个区域,数百万个仿真单元。必须在全部电压范围内对设计进行验证——在制造时进行测试,还要在全部负载范围内维持效率不变。

Karnik说 :“ 内部调节器占用了很大的管芯面积 , 需要进行规划和调试。但必须这样做。”这不但能够对电压进行瞬时调节,响应快速变化的负载,而且避免了采用7个外部芯片。

如果Intel能够继续指明其他供应商先进SoC的发展方向, 那么,我们将看到对负载点调节的需求越来越大,看到调节器本身逐步转到SoC中,在某些情况下,自己还会有电感。当然,设计总会遇到挑战,SoC供电技术会不断发展。

作者:Ron Wilson

Altera公司总编辑

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...