- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用工程加工基板实现晶体管微缩化之途径

微缩化涉及两大任务:将晶体管的尺寸做到更小,以减少成本/功能并改善性能与功耗。从以往的历史来看,人们在每一个新的技术节点上都能同时达到密度与性能目标。在工艺向32nm节点技术发展的过程中,在每一代技术中人们都成功而精确地同时实现了集成电路面积的微缩与晶体管密度的翻倍的目标。然而,人们仍然经常需要在性能、功耗以及密度/面积这些因素之间进行权衡。工程师们也在开发弥合代际差别的解决方案方面表现出惊人的创造性。

目前,人们在克服这些技术极限方面已经取得了一些突破性进展。在材料方面,其中一项重大改进是High-K材料的引入为栅极绝缘层微缩化所带来的改善。应变的引入能提升载流子的迁移率,抵消栅氧化层和栅长度减少所导致的有限增益。在功率方面,供电电压降低的速度远远落后于微缩化理论所需的规划值。因此,多核处理器、多阈值电压(multi-Vt)、复杂的功耗管理策略便应运而生。如今,光刻技术正日益成为突破技术限制的羁绊。超紫外线技术(EUV)和在28nm及以下工艺中采用193nm波长的技术被推延,催生了浸没式光刻以及多重光刻技术,即人们所熟知的双重图形曝光技术(double patterning)。可以预见的是,在14nm节点上,三重曝光技术的采用将在所难免。

正是人们的不断地创新才让各种产品遵循着摩尔定律而不断向前发展。微缩化技术的发展史就是一部创新的历史,绝不是简单地重复。最近在22nm纳米技术上取得重大突破技术则是英特尔的3D器件架构。这充分表明全耗尽晶体管能够通过在相同面积上集成更多晶体管,从而改善集成电路性能和/或降低功耗,是一种卓越的解决方案。

[p]

全耗尽晶体管与传统的晶体管在结构上的区别在于,前者的沟道并不由其掺杂程度(doping level)定义,而是由其物理尺寸(physical dimensions)定义,边界由氧化物材料构成。这种结构在设计上的独特性改善了沟道的栅控制,提高了性能并缩短了栅的长度。此外,由于沟道定义不再受限于沟道的掺杂程度,全耗尽技术提供了另外一种选择,既采用未掺杂沟道。这样就能降低变异性,并提升载流子的迁移率。在当前的电子科技条件下,沟道掺杂是导致变异性的主要源头,而提高载流子的迁移率将提高驱动电流,并提高工作频率。

业界公认,全耗尽晶体管能够至多支持到10nm节点工艺,仍能保持可接受的静电性能(最低可至7nm)。因此,该技术基本可以继续推动微缩化,直到2020年。

目前已经有两种可以实现的全耗尽晶体管结构:FinFET和全耗尽平面晶体管技术(FD-SOI)。无论是在SOI上或bulk基板上都能制造FinFET。

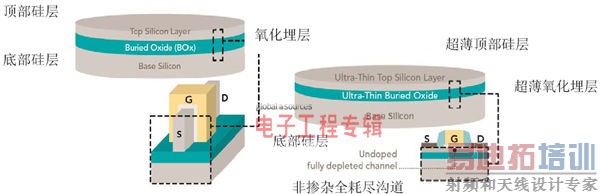

图1. SOI上的3D与平面全耗尽晶体管:(左)Soitec FD-3D基板上的FinFET,鳍片高度由硅层厚度定义;(右)Soitec FD-2D基板上的平面FD-SOI晶体管,沟道厚度由硅层厚度定义

经证明,在微缩尺寸下FinFET架构能够满足高性能/低功耗的需求。然而,FinFET要求进行量化电路设计,每个晶体管仅能拥有数量有限的鳍片。在平面设计中人们可采用不同尺寸的晶体管(从几十纳米到微米级),而在FinFET上则只能选择采用一个或若干个鳍片。当前,由于光刻技术要求重复曝光以获得精确的印刷效果,这局限了设计的发挥。正是因为在当前技术条件下的光刻才是主要的技术限制,因此FinFET的量化对并不是最主要的设计障碍。然而,一旦光刻技术有所改善(如可望引入的EUV技术),当前这种很小的设计影响将会在平面FD-SOI技术对阵FinFET技术的过程中,转化成前者对后者的巨大优势。

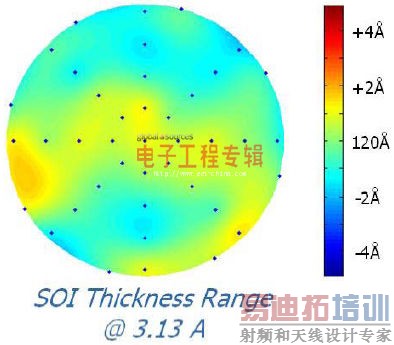

所有的全耗尽结构都对沟道结构非常敏感,尤其是当沟道是非掺杂的时候。从这一点来说,SOI基板能够带来独一无二的极低物理变异性(Physical variability)—— 图2显示SOI基板的一致性误差小于0.5nm,且目前已经实现大量生产。而在FinFET的条件下,FD-3D基板不仅确保了优秀的鳍片高度可复制性,而且确保了高效的鳍片定义流程(fin-definition process),与同类的bulk设计相比实现了大幅度的简化。在FD-SOI的例子中,FD-2D基板甚至可以实现那些对厚度控制要求最为严苛的技术。与FinFET相比,平面FD-SOI可实现与所应用基底偏压动态适应的,良好的功耗优化。此外,在氧化埋层下方的参杂接地面也提供了一种多阈值电压管理的有效选择。

图2:300mm 基板硅晶圆厚度的测量

图2显示出Soitec先进的基板厚度的一致性,误差低于0.5nm。目前的生产线能够生产带有各种点的基板,所有的晶圆的误差都控制在+/- 0.5nm范围内。这些基板已经可以在全耗尽时代实现CMOS的进一步微缩化。

作者:Nicholas Daval

Soitec 设备项目经理

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...