- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

电源设计小贴士36:高压非隔离式电源下产生的共模电流

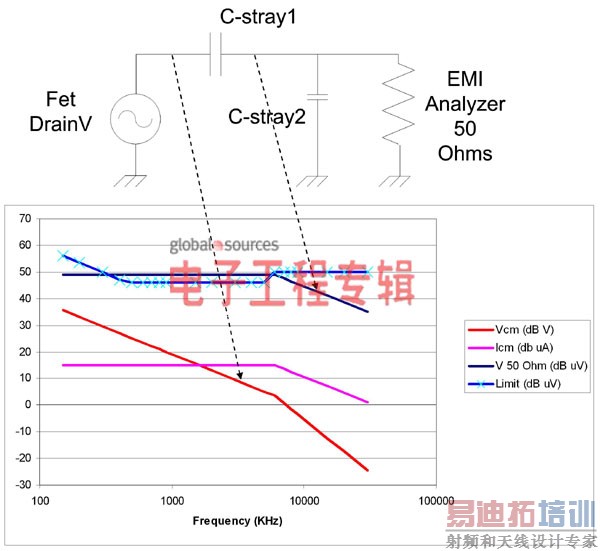

图1是一个LED电源的示意图,其显示了该降压调节器中共模电流产生的主要原因。原因就是开关节点接地电容。令人惊讶的是,如此小的一点电容,仍会产生问题。CISPR B类(适用于住宅设备)辐射规定允许1 MHz下46 dBuV (200 uV)信号的50电源阻抗。这也就是说,仅允许4μA的电流。如果转换器在100 kHz下对Q2漏极的200 Vpk-pk方波进行开关操作,则基准电压约为120伏峰值。由于谐波随频率降低而成比例下降,因此1MHz下会有约9 Vrms。我们可以利用它来计算允许电容,得到约0.1pF,即100 fF(相当于1 MHz 下2兆欧阻抗),其为这个节点完全可能的电容量。另外,还存在电路接地其余部分的电容,其为共模电流提供了一条返回通路,如图1所示C_Stray2。

图1:仅100 fF的开关节点电容却产生了EMI问题

在LED灯应用中,没有基底连接,只有热和绝缘,因此共模EMI滤波便成为问题。这是因为电路为高阻抗。它可以由一个与2兆欧容抗串联的9 Vrms电压源表示(如图2所示),无法增加阻抗来减少电流。要想降低1MHz下的辐射,您需要降低电压,或者减小寄生电容。降低电压共有两种办法:颤动调谐或者上升时间控制。颤动调谐通过改变电源的工作频率来扩展频谱范围。

图2:100 fF可导致超出EMI限制

要讨论颤动调谐,首先请阅读《电源设计小贴士 8》(2009年2月)。上升时间控制通过降低电源的开关速度来限制高频谱,最适合解决10MHz以上的EMI问题。减小开关节点的寄生电容很容易,只需最小化蚀刻面积或者使用屏蔽材料。该节点到整流电源线路的电容,不会形成共模电流,因此您可以将导线埋入多层型印制线路板 (PWB),从而减少大量不需要的电容。但是,您无法彻底消除它,因为FET漏极和电感仍然余留有电容。图2给出了一幅曲线图,引导您逐步计算EMI频谱。第一步是计算电压波形(红色)的频谱。通过计算漏电压波形的傅里叶级数,或者只需计算基本分量然后对包线取近似值(1除以调和数和基本分量),便可完成上述计算。在高频完成进一步的调节(1/(pi *上升时间)),如7MHz以上频率所示。下一步,用该电压除以寄生电容的电抗。有趣的是,低频辐射为扁平稳定状态,直到频率穿过由上升时间设定的极点为止。最后,CISPR B类规定也被绘制成图。仅0.1 pF的寄生电容和一个高压输入,辐射就已接近于规定值。

EMI问题也存在于更高的频率,原因是输入线路传输共振引起的电路共振和辐射。共模滤波可以帮助解决这些问题,因为在C_Stray2存在大量的电容。例如,如果电容大小为20 pF,则其在5MHz下阻抗低于2 K-Ohms。我们可以在电路和50 Ohm测试电阻器之间增加阻抗足够高的共模电感,以降低测得辐射。更高频率时,也是如此。

总之,使用高压、非隔离式电源时,共模电流会使EMI辐射超出标准规定。在一些双线式设计中(无基底连接),解决这个问题尤其困难,因为有许多高阻抗被包含在内。解决这个问题的最佳方法是最小化寄生电容,并对开关频率实施高频脉动。频率更高时,电路其余部分的分散电容的阻抗变小,因此共模电感可以同时降低辐射发射和传导发射。

下次,我们将讨论DDR内存的电源,敬请期待。

作者:Robert Kollman

德州仪器 (TI)

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...