- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

采用多晶锗硅栅减少p沟道功率沟槽MOSFET开关时间

飞兆半导体公司

本文研究了用于p沟道功率沟槽MOSFET的多晶锗硅(poly-Sil-xGex)栅的电气开关特性。当在p沟道功率MOSFET里使用类似的硼掺杂多晶锗硅栅来代替硼掺杂多晶硅栅,可以观察到开关时间减少超过22%。使用多晶锗硅栅的MOSFET的下降时间(fall time,Tf)比多晶硅栅MOSFET要少大约1ns,开关性能提高了大约60%。然而,可以观察到所有的开关性能改善在下降时间(Tf)区域内,原因可能是上升时间(rise time,Tr)内的改善被开关测试电路中较高的串联电阻掩盖了。相比多晶硅(poly-silicon,pSi)材料,由多晶锗硅栅电极提供的较低栅电阻(Rg)可以实现更快的开关速度。在相同器件上的测量发现,多晶锗硅栅的电阻为3.75Ω,而pSi栅的电阻为6.25 Ω。较低的栅电阻(Rg)也意味着在开关期间内功率损耗较低,从而在器件中产生较少的热量。在多晶锗硅栅电极里能够获得非常均匀的硼掺杂分布,这对于功率沟槽MOSFET的芯片均匀成膜和更好的热响应很关键。pSiGe薄膜的优化、性能和器件特性将在以下的章节中详细讨论。

引言

在许多应用中,多晶锗硅(pSiGe/pSiGeC)具有良好的性能,能够很好的替代pSi。主要优点包括较低转化温度、工艺热量预算、大量掺杂能力和更容易与现有硅器件集成。相比p型pSi薄膜,当掺杂硼时pSiGe/pSiGeC薄膜可以达到显著降低的电阻率。伴随着Ge含量的增加,实质上增加了硼活化作用和空穴迁移率,其结果是导致了较低的P+薄膜电阻率。相当低的温度(大约500°C)就能使注硼pSil-xGex薄膜退火,并且与pSi薄膜相比,较低的硼注入量能够在pSil-xGex薄膜中获得较低的电阻率。有报告说,含有高Ge含量(>45%)的N+掺杂的pSil-xGex薄膜的电阻率比N+ pSi更高,这是因为减少了磷的活化作用。也有文章研究指出,通过增加Ge部分可以在硼掺杂中获得显著提高的热稳定性。

在CMOS技术中,pSiGe/pSiGeC已被视为很有前景的可供选择的栅材料,因为它具有较低的多晶硅栅耗尽效应(poly depletion effects,PDE)和硼渗透,并通过改变用于PMOS的栅功能而增强的空穴迁移率。而且,在pSiGe/pSiGeC栅中,可以通过改变薄膜中的Ge含量,来简单地调整阈值电压,比传统离子注入方法更加方便。PSiGe/pSiGeC薄膜也可用于低温(大约550°C)TFT制作和MOS晶体管栅电极。

本文将讨论p型pSiGe/pSiGeC栅与pSi栅MOSFET相比对功率沟槽p-MOSFET开关性能的影响。还将会探讨具有pSi和pSiGe/pSiGeC栅电极的沉积条件依赖的表面形态和MOSFET的其它电气性能。

实验工作

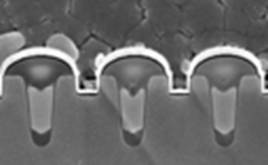

PSiGe/pSiGeC薄膜通过低压化学气相沉积(low pressure chemical vapor deposition,LPCVD)方法在150mm晶片上生长。硅烷(SiH4)和10%H2稀释的锗烷(GeH4)用作气源。锗含量通过改变GeH4和SiH4气体流量来控制。乙硼烷(B2H6)气体是用来作为p型掺杂源。对于pSiGe/pSiGeC薄膜,甲硅烷(monomethyl silane,MMS)被用来作为碳源。SiGe/SiGeC的生长温度在600到720°C范围之间,以便防止表面粗化。使用10 torr生长压力。5700 厚、掺杂硼的pSiGe/pSiGeC/pSiGe/pSiGeC沉积在二氧化硅(silicon dioxide,SiO2)上,作为用于MOSFET的栅极绝缘层材料。pSiGe/pSiGeC薄膜采用干式等离子蚀刻并且深嵌在沟槽中以形成功率沟槽MOSFET栅电极图案,如图1所示。在LAM Research公司的单晶片室里,使用六氟化硫(SF6)和用惰性气体稀释的氯气(Cl2)混合物,采用低压、高密度等离子工艺来进行蚀刻。在同一蚀刻室里,氧化层突破蚀刻工艺先于两步式pSiGe/pSiGeC蚀刻工艺。氧化层突破阶段清除了在pSiGe/pSiGeC薄膜上形成的任何原生氧化层并且帮助防止薄膜蚀刻后颗粒和节结的形成。在首次蚀刻阶段,大部分pSiGe/pSiGeC薄膜被蚀刻,直到光学终点系统触发首次等离子蚀刻结束。第二步,固定时间等离子刻蚀阶段,继续移除薄膜形成栅电极图案,在沟槽内达到所期望的深度。接下来,带图案的薄膜受到BF2注入,形成P+源,并且在炉中退火用于源极掺杂剂活化。最后,钛(titanium,Ti)、钛钨(titanium tungsten,TiW)和铝(aluminum,Al)金属被沉积、硅化和蚀刻,以形成源极和栅极接触区。作为对比,在炉中pSi栅通过在栅氧化层上沉积pSi薄膜来制作,用最大可能剂量注入P+作为源极和栅极区域,然后进行退火以达到最低的电阻率。形成MOSFET器件的所有其它制作步骤和其pSiGe/pSiGeC/pSiGe/pSiGeC C栅对应物是同样的。图1显示了有pSi/SiGe栅的已制作的功率沟槽MOSFET结构的横截面。

图1. 有pSiGe 栅的p沟道MOSFET横截面。

基于工艺条件,p-SiGe薄膜的生长率介于10至60 nm/min,已采用基于电阻率、均匀性、粗糙度和沉积速率的最佳工艺条件来为MOSFET器件生长pSiGe/pSiGeC /pSiGe/pSiGeC栅。通过次级离子质谱分析法(secondary ion mass spectroscopy,SIMS)测量来估算p-SiGe薄膜的锗和硼的含量(以原子百分率)。使用四探针测量薄膜电阻率。表面粗糙度、薄膜厚度和横截面研究则使用原子力显微镜(Atomic force microscopy,AFM)和扫描电子显微镜检查法(Scanning electron microscopy,SEM)技术来进行。使用Eagle测试仪来检测所有器件参数,并且成品封装器件都进行开关特性试验。

[p]

结果和讨论

1. 表面粗糙度

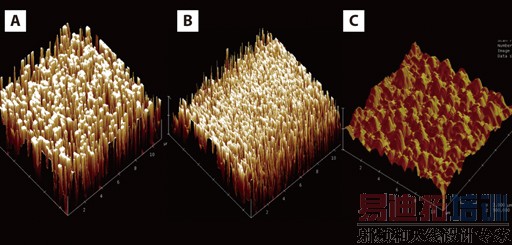

在低压化学气相沉积(LPCVD)室内,随着温度、压力和SiH4气体流速的增加,pSiGe/pSiGeC的沉积速率从10 nm/min增加到60nm/min。然而,使用原子力显微镜(AFM)和横截面扫描电子显微镜(SEM)测量,却显示薄膜质量、粗糙度和均匀性在恶化。增加甲硅烷(monomethyl silane,MMS)气体可改进粗糙度和薄膜质量。很可能是因为引入的碳原子能够减少pSiGe/pSiGeC晶界和/或晶格应力,带来更平滑的表面,在结晶的SiGeC下显得是真实的。RMS粗糙度从75nm到7.5nm,提高了大约10倍,如图2中AFM表面轮廓图所示。在粗糙度方面比PSi薄膜提高了约1.5倍。

图2. PSi (A), pSiGeC (B) 和 PSiGe (C)表面轮廓。

2. 电阻率

相比在熔炉中沉积的pSi 薄膜的5mΩ-cm,使用硼掺杂源(B2H6)后,pSiGe/pSiGeC薄膜的电阻率显著地减少到2mΩ-cm。另外,对于pSiGe/pSiGeC薄膜,不再需要如P+注入和退火工序,从而带来成本改善。

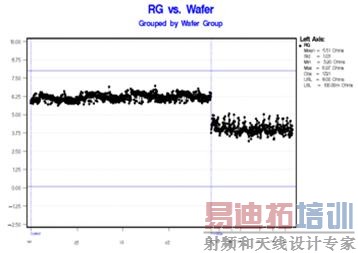

在传统的MOSFET中,当通过在晶体管栅极和源极施加偏压(Vgs)使晶体管反转时,电荷载体耗尽并远离pSi电极和二氧化硅(SiO2)电介质界面。这种电荷载子的耗尽,更多地称为多晶硅栅耗尽效应或PDE,当器件处于偏置反转模式时,在电介质附近多晶硅薄层变成非导电的,导致了电介质明显变厚。该栅极绝缘层的明显增厚转而引起漏源电流密度的降低,而漏源电流密度对于晶体管是一个非常重要的品质因数。相比于Si,pSiGe/pSiGeC具有较小的能带隙,对于相同百分比的有活性的掺杂剂,其活化温度较低,并且对于某些掺杂剂,扩散率较低。尤其是,Ge的存在导致更高的有活性的掺杂浓度,不用依靠更高的注入剂量。如图3所示,相比pSi栅器件,pSiGe/pSiGeC栅器件记录到栅电阻(Rg) 减少了40%。

图3. PSiGe和PSi器件的栅电阻比较

对于pSi栅的平均电阻是6.25Ω,而对于pSiGe/pSiGeC栅,其值为3.75Ω。这主要原因是在多晶锗硅中有更多的硼原子被结合且被电力激发,因为PSiGe/pSiGeC中的硼的固溶度极限比pSi中的高。

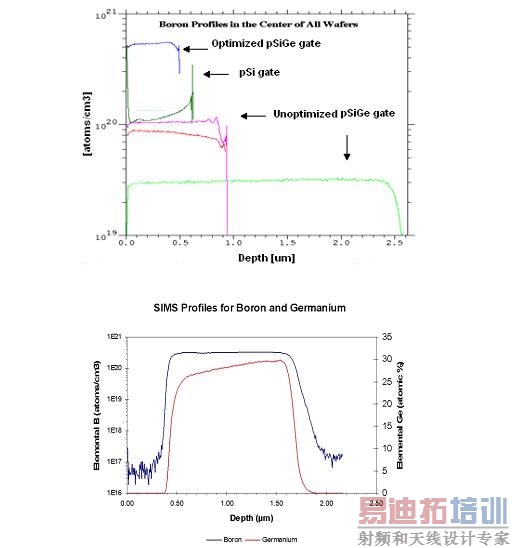

传统pSi栅的另一项表现是在涉及到晶体管制造的热循环期间,pSi中的硼原子趋向于扩散穿过栅氧化层。在图4中显示,使用SIMS技术,在制成的pSiGe/pSiGeC和pSi MOSFET栅电极中硼掺杂剂分布图的比较结果。沿着pSi栅电极的掺杂剂分布图显示硼浓度因为向外扩散而在表面上减少,其在表面和0.1μm之间急剧降低,并且越来越多的深入到栅电极内。此现象导致使用传统pSi栅电极的功率MOSFET中阈值电压(Vth)稳定性的降低。然而,优化的pSiGe/pSiGeC栅电极显示出均匀的掺杂剂分布图,并且在退火后沿着电极长度具有较高的浓度。这种扩散率的减少相当于硼原子从取代位置到间隙位置的局部迁移的减少,从而提高了硼原子的热稳定性。

图4. 硼和锗元素的SIMS分布图

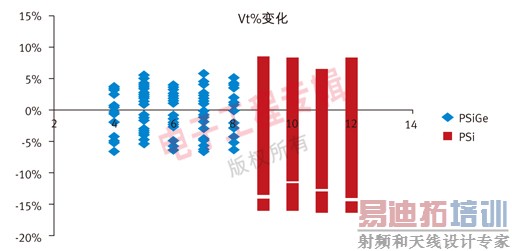

图5显示了传统pSi栅和pSiGe/pSiGeC栅MOSFET的Vth分布比较分析结果。相比pSi栅MOSFET的-1.5V,pSiGe/pSiGeC栅MOSFET具有较低的-1.8 V的Vth值。此外,pSiGe/pSiGeC栅的Vth分布比pSi栅更紧密,仅为约5%的波动,而PSi样品显示的波动超过15%。这是因为具有更好热稳定性的硼掺杂剂进入了pSiGe/pSiGeC栅电极内。

图5. PSiGe和Psi Vt%变化比较。

pSiGe/pSiGeC栅和pSi栅MOSFET采用TO-220 3引脚分立封装,并具有电气特性。对于pSiGe/pSiGeC栅MOSFET,标示开关性能提高了60%,超过传统pSi栅对应产品。出于简洁,讨论中省略了测试电路和条件。从图6的汇总中明显可以看到,pSiGe/pSiGeC栅器件的Toff提高了12ns且Tfall减少了10.7ns。然而, 由于测试电路中的高串联电阻的原因,无法确定Trise的改进。更好的开关性能使得这种p沟道功率MOSFET成为高效能电源电路的强有力竞争产品,不但能省去复杂的用于驱动N沟道高侧功率MOSFET的栅驱动电路,还可降低电源的成本。

图6. pSiGe和pSi器件的开关性能比较。

结论和挑战

总之,多晶锗硅的电气性能和与传统硅工艺的兼容性,使之成为多晶硅的潜在良好替代品,并用作p沟道功率MOSFET的栅材料。使用相似剂量的硼掺杂,pSiGe/pSiGeC薄膜能够达到比pSi薄膜显著较低的电阻率,这得益于更高的掺杂剂结合及较低的工艺热量预算。在本文的实验中,相比其pSi对应品,我们证明pSiGe/pSiGeC栅MOSFET的Rg降低了40%。另外,可以使用较低的温度(大约 500°C)进行硼注入pSiGe/pSiGeC薄膜退火。pSiGe/pSiGeC作为栅电极材料的替换物用于p沟道功率MOSFET技术,在Vth稳定性及提高器件开关性能方面显示出额外的优势。

然而,在半导体制造商业环境中,集成pSiGe/pSiGeC栅在优化薄膜粗糙度/空隙率以填充较小尺寸和这些薄膜的等离子蚀刻方面也面临着挑战。需要通过研究来进一步优化薄膜粗糙度和均匀性,通过碳和其它掺杂剂种类来提高器件的栅泄漏性能。锗的存在极大地增加了蚀刻速率和工艺控制的复杂性。等离子蚀刻有一个很小的工艺窗口,用于同时优化蚀刻速率及光学终点信号强度,以便获得可重复的干式蚀刻过程。控制pSiGe/pSiGeC嵌入沟槽以形成栅电极图案,也需要按照反应气流、RF功率和压力来细调工艺,同时维持栅氧化层的完整性。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:浅析LED显示屏的节能原理

下一篇:使用多相降压转换器的优势