- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA和DSP的音频采集卡的实现

摘要: 本文介绍了一种基于FPGA和DSP的多通道音频采集卡的设计和实现方案,该卡能够工作在多种采样率下并可以使用DSP中不同的音频算法用于满足不同场合,并通过PC104接口将处理后的数据上传至主机。采集卡已应用在船舶航行数据纪录仪VDR中。

关键词: FPGA;DSP;PC104;多采样率;音频数据压缩;航行数据记录仪VDR

0 引言

一个多通道数字音频系统必须考虑两个问题:采集到声音的质量问题和最终数字化后的音频存储的问题。由奈奎斯特定理知,如果要保证把采集到的音频信号完全无失真的恢复出来,采样率就必须至少是需采集音频信号频宽的2倍。由于现在大多数音频CODEC采用了Delta-Sigma Modulator,在保证采样率合适的情况下,声音质量一般是可以满足要求的。在船舶航行记录仪中,音频的频宽是150hz-6000hz,因此我们可以采用16khz的采样率和16位的量化位数。

按照这样的采样率,单路的音频码率为256kbps,24小时音频的数据量就高达2.76GB。为了减少最终存储器的存储空间,需要对原始的音频数据进行压缩处理。一般来说有损压缩比无损压缩的压缩比要高的多,但是同时会造成音质的下降。系统设计时应该进行适当的平衡。

本文设计的基于FPGA和DSP的多通道音频采集卡,采用Altera公司的Cyclone系列FPGA简化逻辑控制和提高硬件速度;采用TI公司的TMS320VC 5416实现音频压缩算法,在满足了音频性能指标的同时减少了最终的音频数据量,满足了系统的设计要求。

1 系统硬件结构

1.1主要芯片选型

(1) 音频CODEC芯片PCM3008

在音频CODEC芯片的选型上采用了Texas Instruments公司的PCM3008。这款音频CODEC芯片采用了16bit的△-∑ADC和DAC。其中立体声ADC具有单端电压输入,内置抗混叠滤波器。优异的性能还表现在其ADC的总谐波失真加噪声低至-84dB,信噪比高达88dB,动态范围至88dB,其内置的1/64× Decimation数字滤波器使得信号在通带内波动仅有±0.05dB,阻带衰减可至-65dB。低压工作,低功耗。其采样率为8khz-48khz可选。数据传输为同步串口方式,操作方便。

(2)FPGA芯片EP1C6Q240

FPGA采用Altera公司的Cyclone系列的 EP1C6Q240实现各器件的接口控制。Cyclone系列的FPGA是Altera公司针对低成本高性能的应用而推出的,具有很高的性价比。EP1C6Q240的最大可用IO数量185;片内92Kbit的RAM可以配为单双口RAM,ROM,FIFO等各式存储模块;两个高精度锁相环,方便地为片内的各个模块提供所需时钟;5980个LE(逻辑单元),为接口电路的实现提供丰富的逻辑资源。Altera公司的QuartusⅡ集成开发环境简便易用,内含大量IP核,其内嵌的Signal TapⅡ逻辑分析仪更是为用户的调试提供了很大方便。

(3)DSP芯片TMS320VC5416

DSP芯片采用TI公司的TMS320VC5416。TMS320VC5416是TI公司5000系列中高性能低功耗的定点DSP,它建立在C54x DSP核基础上。TMS320VC5416是一款16位定点高性能数字信号处理器, 其主要特性有: 速率最高达160MIPS; 3 条16位数据存储器总线和1条程序存储器总线; 1 个40位桶形移位器和2 个40位累加器; 1 个17×17乘法器和1 个40位专用加法器; 最大8M ×16位的扩展寻址空间, 内置128 k ×16位的RAM 和16 k ×16位的ROM; 3 个多通道缓冲串口(McBSP);其丰富的外设和强大的运算能力,使得TMS320VC5416可以进行实时的多路音频处理。在压缩的实现上,使用通用DSP芯片TMS320VC5416与使用专用的硬件压缩芯片相比,不仅可以节约成本,还可以方便地实现系统的升级和灵活的配置。

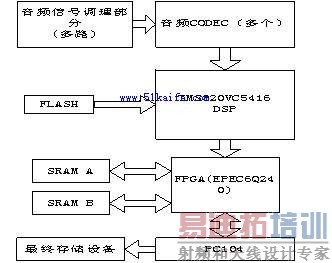

图1

1.2 系统设计思路

硬件结构设计如图1所示。多路音频信号首先通过调理部分,进入音频CODEC PCM3008,通过BCK,LRCK,DOUT三根信号线将音频数据送入DSP的 RAM内,DSP会按照一定的顺序将一帧音频数据整理好放在一个数据缓存里,并对其中的每路音频数据依次调用音频压缩算法,在下一帧音频数据到达该缓存区前将数据通过FPGA中的SRAM控制器发送到SRAM中,并告知PC104主机采集过程完毕。PC104主机通过FPGA内的PC104接口模块,将缓存SRAM中的数据读取出来。

2 FPGA的功能模块设计

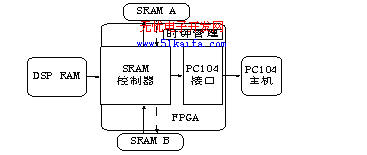

FPGA的设计采用模块化的设计思想。主要模块按功能划分如图2所示。SRAM控制器采用了乒乓机制,一片处于读数据的状态,另一片处于写数据的状态,每15秒钟在PC104主机的控制下切换一次。这种操作方式时序设计简洁可靠,易于做到音频数据连续操作。收到PC104主机发出的切换命令后,待两片SRAM都处于空闲的时候,完成两片SRAM的读写切换。切换的同时,SRAM的读写的地址都会复位,而且会保存刚才15秒内的数据量信息,保证每个15秒读和写都是从零地址开始的,同时也方便读取数据。切换成功后,给出数据就绪的信号,指示主机可以读取数据。PC104接口模块负责采集卡与上位机的通讯和数据传输。

完成两片SRAM的读写切换。切换的同时,SRAM的读写的地址都会复位,而且会保存刚才15内的数据量信息,保证每个15秒读和写都是从零地址开始的,同时也方便读取数据。切换成功后,给出数据就绪的信号,指示主机可以读取数据。PC104接口模块负责采集卡与上位机的通讯和数据传输。

图2

3 DSP硬件和软件设计

3.1 DSP的硬件设计

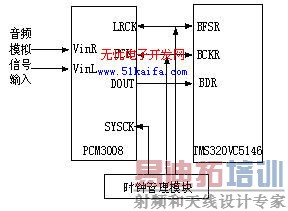

DSP采用McBSP与音频CODEC通信,系统框图(双路音频接收框图)如图3所示,McBSP依靠三个信号实现接收数据:数据线DR、帧同步线FSR和移位时钟线CLKR。DR引脚完成从音频CODEC中接收音频数据,由CLKR、FSR实现时钟和帧同步的控制。接收数据时,来自DR引脚的数据在FSR和CLKR作用下,从数据寄存器DRR中读出数据。CLKR、FSR既可以由内部采样率发生器产生,也可以由外部设备驱动。该音频系统中,CLKR、FSR信号均来自于FPGA。

为了减轻CPU负担,音频数据的传递采用了DMA机制。 TMS320VC5416有6个可独立编程的DMA通道,每个DMA通道受各自的5个16位寄存器控制:源地址寄存器DMSRC、目的地址寄存器DMDST、单元计数寄存器DMCTR、同步事件和帧计数寄存器DMSFC、发送模式控制寄存器DMMCR。

通过设置DMA1通道与McBSP1通道结合来读取PCM3008转换完的数据为例:选择McBSP1通道的接收寄存器DRR11(41h)为DMA传送数据的首地址,并选择源地址工作在访问后不调整方式,选择DMA通道同步事件McBSP1接收事件为DMA同步事件,来实现DMA和McBSP的结合。PCM3008转换完的数据按McBSP1的设置被送到TMS320VC5416内部接收寄存器DRR11中,再由DMA将DRR11中的数读到指定数据存储区来完成数据采集。DMA在传送外部来的数据时不会影响CPU的正常运行,当DMA采集完一组规定个数的数据后产生一个DMA中断事件中断CPU,来通知CPU对其进行相应的处理,此时DMA可以按照设定继续采集下一组数据,实现了数据采集与CPU处理的并行操作。

图3

3.2 软件设计流程

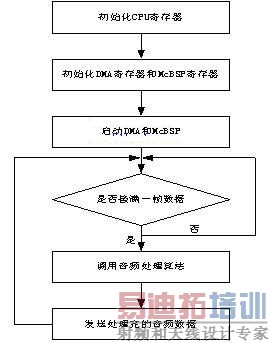

程序流程如图4所示,系统上电后首先初始化CPU,McBSP,DMA寄存器,然后打开中断,当所有DMA的传输完成后,给出一个状态标志,通知CPU音频数据准备好,CPU将原始的音频数据集中在一个缓存中并开始调用音频处理算法依次处理每路音频数据,并将处理后的音频数据通过总线发送出去。然后继续等待处理下一帧音频数据,周而复始。

图4

3.3 音频压缩算法

由于该系统音频所要求的信号频率的范围是150hz-6000hz,因此必须采用一种宽频音频算法,我们设计了一种宽带语音编码。码率24kbps~64Kbps可变。其主要参数如表1:表1 音频编码的主要参数

4 结论

本文设计的多通道音频采集卡可以实现8路麦克风信号,2路VHF(甚高频)信号的采集与处理。24小时生成的数据量不足1.6GB,并且声音质量满足IEC 61996-2中关于音频要求的指标,该多通道音频采集卡已经成功地应用到船载航行数据记录仪中,并且通过了中国船级社(CCS)的检验,装配该多通道音频采集卡的VDR系统已经投入实用。

本文作者创新点:采用了自主的音频编码算法设计,并用DSP芯片实现,在数据存储和读取上采用了巧妙的乒乓设计。

参考文献:

[1]邱效祝, 李志宏, 喻方平; 船舶航行记录仪试验测试系统设计,船海工程 , 2006,05。

[2] 安颖,刘丽娜;基于DSP的高速信号采集与处理系统的设计,微计算机信息,2005,01。

[3] 喻方平; 船载航行数据记录仪(VDR)研究设计,中国航海,2002,02。

[4] 常勇,丘效祝;船载航行数据记录仪系统串行总线接口设计,中国水运,2004.4。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:军用开关电源可靠性设计研究

下一篇:蓄电池名词术语