- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种结构简单的低压低功耗ALU单元设计

摘要:1位的ALU单元在某些集成电路的设计中非常重要,本文提出了一种结构简单的高速,低功耗,低工作电压的ALU单元。在此设计中采用了XOR/XNOR结构,并加入了适当的缓冲电路,有效的提高了运算速度,并可以减少在级连中的阀值损失,同时还保持了较低的MOS管数量。通过HSPICE(CSMC 0.35um工艺)仿真,得了很好的特性。

关键词:低功耗;高度;小面积;新ALU单元

1.引言

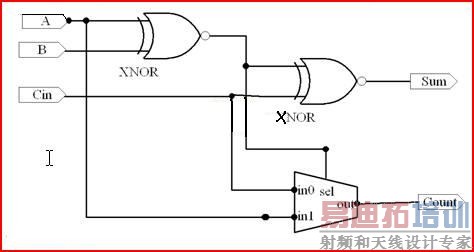

随着手持式个人通讯系统等的发展,低压低功耗高吞吐量电路的需求越来越多,因此低功耗微处理器和元件的设计已经变成了主流。ALU是微处理器最重要的组成部分,其中全加器电路是所有运算电路的基本单元,设计低功耗快速加法器单元是获得低功耗高速运算电路的关键。ALU单元的设计标准是多种多样的,晶体管数量显然是一个主要的关注点,因为它极大的影响了功能单元ALU的设计复杂性。另外两个重要的却又相互矛盾的因素是功耗和速度。与功耗降低相关的一个因素是电路能工作的最低电压, 还有一个是晶体管的数量,而全加器晶体管的数量又极大的影响了ALU单元的晶体管数量,因此全加器的设计也是ALU设计中必须重点考虑的一部分。对于已有的全加器的设计按照种类来分【1-8】有静态CMOS电路,动态电路,传送管和传输门逻辑。其中全静态CMOS电路是最传统的,但需要28个管子。动态电路能极大的减少晶体管的数量但是短路功耗却很大;使用传送门逻辑是一个可选的降低电路复杂性的方案。在【1】中基于传送门和反向器的全加器设计中各使用了20和16个晶体管,为了得到更少管子的全加器,在【2】中基于XOR/XNOR的传送门逻辑电路组成的全加器只用了14个管子,在【3】中,介绍了一个基于传输管的静态能量恢复全加器(SERE),它只使用了10个管子,且不管它自称的功耗小,这个设计相比同类的设计来讲速度比较慢,同时这个设计不能用来级连,因为在低电压下工作时有多阀值损失问题。在【4】中一种新的基于选择电路的10管全加器设计被提出,然而这个设计也同样有多阀值损失问题,以至于不能在低电压级连模式下正确的工作,前面提到的10管全加器都是基于图1的原理来的。文中的ALU单元将采用一种新的10管全加器,它可以减轻阀值损失问题,这个设计可以在使用少量管子的情况下组成快速的并行加法器(RCA)同时保持较低的能量损耗,另外,这个设计可以在较低的工作电压下正确运行。

图1 .现有的10管全加器结构

Figure 1. 10-T Full adder Architecture of existent

2.新的基于CLRCL全加器的ALU单元

首先考虑全加器的设计,全加器的逻辑表达式为:

Sum=(A⊙B)·Cin+(A⊕B) ·!Cin Count=(A⊕B) ·Cin+(A⊙B) ·A

可以看出有两个基本的模型需要使用――XOR和2选1选择器。一个XOR/XNOR功能用传送门逻辑只用四个管子就可以达到【5】,一个2选1选择器可以用两个管子实现。但是这些电路都有不同程度的阀值电压损失,所以在使用时必须小心,文中将采用一种新的全加电路,这个全加器的特点是进位逻辑电平恢复称之为(Complementary and Level Restoring Carry Logic or CLRCL)。目的是为了减小电路的复杂性和达到快速的级连运作。为了避免进位链的多阀值电压损失,为此重写全加器的和以及进位逻辑公式:

Sum =(A⊕Cin) ·!Cout+(A⊙Cin) ·B Count =(A⊕Cin) ·B+(A⊙Cin) ·A

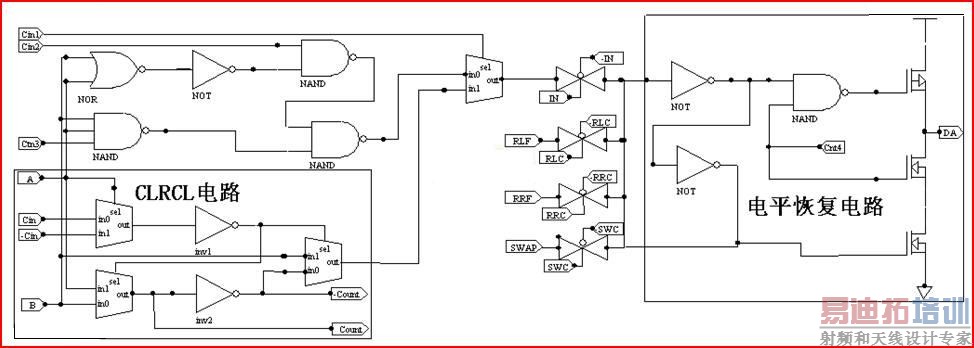

图2.新的1位ALU单元电路图

Figure 2. New 1-bit ALU unit

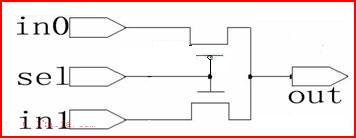

改进后的电路图如图2.其中MUX的电路如图3所示。这样设计的合理之处在于以下几点:首先,避免了使用有阀值损失的信号作为下一个单元的控制信号,这是在现有的10管全加器中普遍存在的问题,这将导致在电路级连的时候有多阀值电压损失从而使电路不能正确工作;第二,在传送管链中去除了没有缓冲的进位信号传送。根据Elmore公式,传送延迟时间跟级连的传送门数目是二次方的关系【6】。即使是中等数目的级连长度,这样的延迟也是不能忍受的。

图3 .MUX 的MOS电路图

Figure 3 . MOS schematic circuit of MUX

正如图2中全加器部分电路所示,XNOR电路采用了一个2选1选择器加一个反向器来实现,这个反向器的功用有三个:第一,反向器INV1可以用来补偿输出传送门输出电压的损失,这个输出将用来与另外两个2选1选择器一起实现和以及进位功能,这样和以及进位信号的阀值电压损失可以控制在一个|V t|;第二,反向器INV2在进位链中充当了一个缓冲器的作用,从而加速了进位的传送;第三,同时这个反向器提供了一个进位的互补信号(!Count)供下一级电路使用。这样全部的全加器部分电路就只需要10个管子(5个PMOS和5个NMOS),这是目前我们所知的最少的实现全加器电路的晶体管数目。

在逻辑与或的功能部分,采用了两个信号来控制(Cnt2和Cnt3)(Figure 2所示),当全加器的和信号以及逻辑与/或功能信号产生后,再使用一个2选1选择器(控制信号为Cnt1),共使用了三个控制信号实现了全加及逻辑与/或的功能(见Table 1),使用了两个用传送门实现的2选1选择器串联后,这个电路会有两个阀值电压的损失,不过这并不影响最终电路的正确操作,因为两个阀值电压的损失在3.3v的工作电压下还是可以正确工作。

至于左移、右移和SWAP功能可以通过传输门来实现(见Figure 2右部分),通过不同的控制信号可以轻易的实现这些功能。

前面提到了本文中提出的电路会有两个阀值电压的损失,为了后续电路的正确工作我们可以加一个电平恢复电路,同时这个电路还可以加快电路的传送速度(见Figure 2右半部分),在此恢复电路中我们使用了一个控制信号(Cnt4)来实现三态门的功能以控制信号的输出与否。加上这部分电路后输出信号会取反,在许多处理器中信号采用的是补码形式,而这为补码的实现提供了便利。

3. 电路分析和仿真结果

一些其他的全加器设计将用来和本文的全加器比较,因为设计的目标是降低电路的复杂性和提高电路的速度以及能量损耗的降低,所以主要关注于门数少并基于传送门的全加器之间的比较。已有的全加器总结如下表2。

在0.35um工艺下仿真一些10管的全加器的DC特性,其中Vdd为3.3v,反向器的(W/L)p=1.4um/0.35um 以及(W/L)n=0.7um/0.35um(table3)。另外,此电路在1.9v的电压下依然可以正确工作,这为进一步降低功耗提供了一个很好的途径。

TALBE 3. Simulation results of 10-T adder designs in 0.35um CMOS technology .(td=time delay)

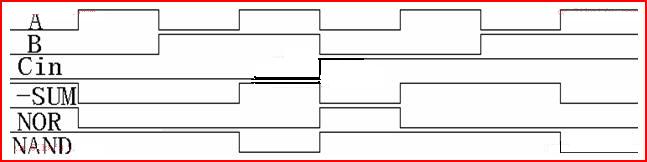

对整个电路进行DC分析,得到整个电路的功耗为12.12 uw,延时1.5ns,仿真结果见图5。另外在AC方面,这个电路的工作频率也是比较高的。

图5 . 电路仿真结果

Figure 5. simulation result for all circuit

4.结论

本文提出了一种新的1位的ALU单元。所提议的ALU单元在DC方面,可以在很低的工作电压下工作,功耗小且速度快;在AC方面,由于采用了CLRCL全加器可以工作在很高的频率下。同时,比较了现有的一些全加器的性能,可以看到文中的CLRCL电路不仅使用的晶体管的数目较少,同时它的功耗和速度性能也是比较优良的,极大的提高了1位ALU的性能。

本文创作者新点:

本文针对目前在RISC结构的MCU/MPU等中需要使用低功耗,小面积,快速的ALU单元,提出了一种新的结构简单的ALU单元结构,在此结构中使用的全加器是目前比较流行的10-T全加器,通过对全加器布尔逻辑的重组,使这种全加器在级连结构中不会产生多阀值损失的情况,最后在电路输出部分采用了电平恢复结构,使电路的输出波形很好,同时这种结构与现有的结构相比有着明显的面积,速度,功耗方面的优势。

参考文献:

[1] N.Zhuang and H. Wu,"A new design of the COMS full adder," IEEE J. of solid state circuits, Vlo.27,pp.840-844,May 1992.

[2] J.Wang, S.Fang, and W. Feng, "New efficient designs for XOR and XNOR function on the transistor level ,"IEEE J. Solid-State Circuits, Vol. 29, pp. 780-786, July 1994.

[3] R. Shalem, E . John, and L.K. John ,"A novel low-power energy recovery full adder cell," in Proc. Great Lakes Symp. VLSI,pp.380-383, Feb.1999.

[4] Fartash Vasefi and Z. Abid ,"10-Transistor 1-bit Adders for n-bit Parallel Adders," IEEE J. of solid state circuit ,pp.7803-8656,Apr, 2004.

[5] H.T.Bui, A.K.Al-Sheraidah, and wang,"Design and analysis of 10-transistor full adders using novel XOR-XNOR gates," in Proc. Int. Conf. Signal Processing 2000(Wold Computer Congress),Beijing, China,Aug.2000

[6] N.Weste and K. Eshraghian, Principles of CMOS VLSI Design, a System Perspective. Reading, MA: Addison-Wesley,1993.

7] Yingtao Jiang, Abdulkarim Al-Sheraidah, Yuke Wang , Edwin Sha, and Jin-Gyun chung, "A Novel Mutipleser-Based Low-Power Full Adder," IEEE Transactions on circuits and systems-II: express briefs, Vol.51,No.7 ,July 2004.

[8] 卢君明,徐锋,胡鹏飞,"低电压低功耗全加器的研究设计,"固体电子学研究与进展,第24卷,第3期,2004年8月

[9] 张杰; 基于FPGA的八位RISC CPU的设计[J]; 微计算机信息,2006-35-05

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...