- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

具有多个电压轨的FPGA和DSP电源设计实例(二)

实现电源轨的受控单调上升

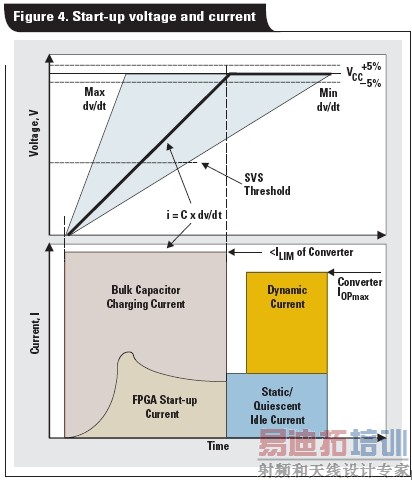

最后推的电源设计方案是在启动时单调上升,在图4的上图所示。

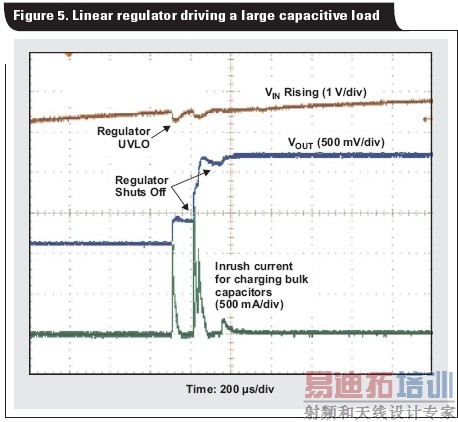

大容量电容的容量过大将迫使POL转换器在启动期间进入电流限制,进而可能使转换器反复进出热停机状态而永远不会达到期望的稳压输出。对快速启动型线性稳压器而言,一个很常见的启动问题是,如果输入电源在启动时电压下降,在输入电容重新充电之前将暂时激活该稳压器的欠压锁定(UVLO)。这引起该调解器重复地短时停机然后恢复,导致输出电压振荡并最终锯齿状上升到终值电压。图5显示了由一个样板电源供电的快速启动型线性稳压器的例子,输入电源的电压下降,激活UVLO并停机,该过程重复进行,最终达到期望的稳压输出。

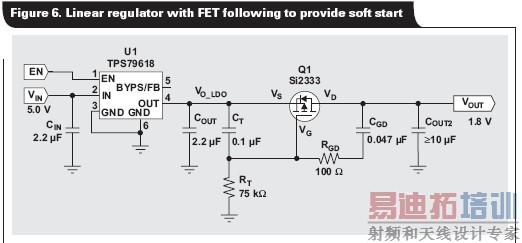

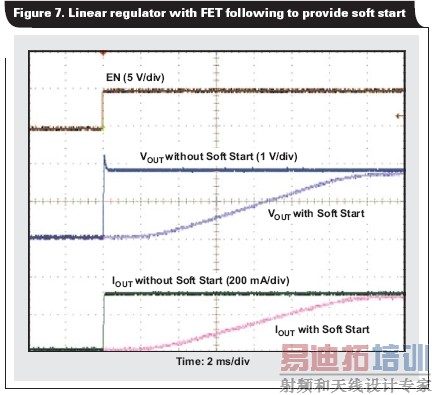

只有少数线性稳压器带有可以控制启动过程的软启动功能。在启动时,除非进入热限制或输入轨电压被拉下来,这些稳压器向输出电容提供最高到其电流限定值的充电电流(如图5所示)。不管是内部固定的还是外部可调的,所有的开关转换器都带有某种软启动。把跟在直流/直流转换器之后的FET用作电流限制开关可以实现软启动。图6和图7显示了此类应用的一个实例和软启动的结果。

线性稳压器和开关转换器实现软启动的常用方案有两种,即参考电压控制或电流限制控制。在这两种方案中,都使用一个小的外部电容(在皮法到1μF的范围)来控制软启动定时。电压控制的软启动通常通过慢慢提升参考电压来实现。因为反馈环迫使该转换器提供足够的电流使输出电压跟随参考电压,输出电压提升的速度(dv/dt)正比于在软启动期间提供参考电压的启动电容。设定输出电压的上升速度所需要的外部电容值由一个简单的定时方程来决定。假设突入电流(inrush current)由充电大容量电容CBulk决定,突入电流将是固定的(i = CBulk dv/dt),如图4所示。让两个这类软启动共享同一个的软启动电容可以实现在本系列论文第一部分所讨论的比率(ratiometric)排序。

|

当使用电流限制控制的软启动时,转换器缓慢地或以步进方式把电流限制提升到最大值。此时,该转换器看起来像一个电流源,把一个慢慢提高的电流提供给负载。由于电压反馈环仍然试图提供期望的输出电压,所以该转换器将提供电流限制和各种热保护所允许的最大电流。输出电压的提升速率(dv/dt)是输出电压的绝对数值(即一个1.2V轨将比3.3V轨提升的更快)、该轨上的阻性和容性装载以及该转换器的电流限制设定值的函数。

|

|

负载跃变所产生的暂态过程

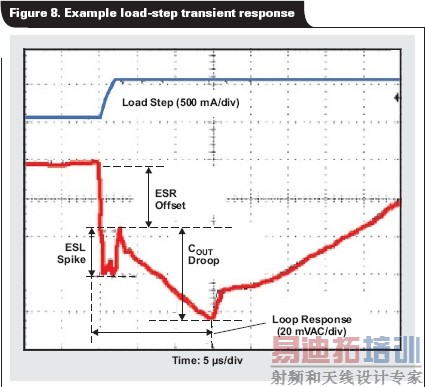

不论依赖于传统PWM转换器的环路带宽还是依赖于磁滞转换器的固定的开关时间,所有POL直流/直流转换器都有有限的暂态响应时间。图8显示了低电流线性稳压器对输出负载电流变化(如一行引起DSP完成复杂运算的代码)的响应。

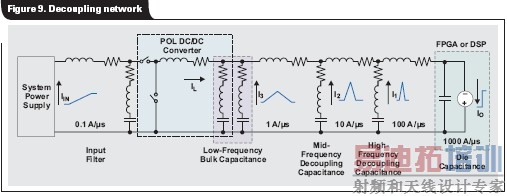

使用低ESR和低ESL(等效串联电感)的输出电容有助于减小暂态下垂。然而,为了帮助该转换器应付阶跃暂态,几乎总需要在该电源轨的输出端另外附加电容,并需要增加局部旁路电容。图9显示了负载阶跃暂态过程的传播和由解耦网络产生的抑制作用。不同容量的电容抑制不同频率的负载阶跃暂态成分,以至于POL转换器(从根本上说,其输入电源)被迫只能小幅度支持该阶跃负载的低频成分。例如,如果FPGA或DSP产生1000 A/μs的负载阶跃,由于解耦网络对该暂态的抑制作用,该转换器被迫只能对1A/μs的暂态做出反应。

小电容(在几皮法到1μF的范围)处理负载阶跃的高频成分。1到22 μF的电容处理中频成分,从47到1000μF的低ESR大容量电容处理低频成分。优化解耦网络(即把所增加的电容量降到最小)的常见方法是目标阻抗方法,参考文献4全面介绍了该方法。该方法要求设计者知道被供电器件的负载阶跃暂态的最坏情况(如在0.5 μs从200mA上升到2.2A或4A/μs阶跃的持续时间为10μs)并对POL转换器的暂态响应能力有所了解。

如果POL转换器的位置远离被供电的数字IC和/或板布局要求电源轨使用窄的箔线和/或小的过孔连接到负载,则需要为如图9所示的模型提供板电阻和电感的近似值。

|

对大多数FPGA和DSP应用来说,负载阶跃暂态的最坏情况大多是未知的,因而,使用经验法则来设计解耦网络更为简单一些。例如,常常根据数字IC所使用的电源引脚总数(或根据每个部分所使用的电源引脚数)按某个比例来放置各类电容(高、中、低频)。这种解耦网络设计方法是有效的,但趋向于过设计,没有充分利用线性稳压器的或开关转换器的暂态响应能力并因加入了额外的电容而占用较大的板空间。

可以采用经验法则相互独立地完成解耦网络和POL转换器的设计。但这种方法存在一个风险,POL转换器可能会因为解耦网络的附加电容而变得不稳定,因而需要对该转换器在输出端的总电容进行补偿。TI公司在power.ti.com/swift网址提供的参考文件和设计软件可以对转换器的设计和补偿提供帮助。人为地把一个负载阶跃暂态加到转换器的输出端并观察因该转换器响应该暂态而产生的输出电压振铃(振荡)是另一种确定转换器稳定性的方式。作为一个经验法则,如果该转换器在进入稳态之前振荡三次以上,则认为系统濒临不稳定(欠阻尼)。如果响应较慢且没有振铃或超调,则可认为系统是非常稳定的(过阻尼)。

|

PC处理器可以发生多个在1000A/μs的范围内的负载阶跃暂态,所以既需要保证POL转换器的暂态过程短也需要较大的解耦网络。为降低解耦网络的成本并减小它所使用的板空间,PC母板制造商现在使用目标阻抗方法(或类似方法)来减少电容的数量和充分利用直流/直流转换器的暂态能力。与PC处理器相比,目前单独的FPGA和DSP应用的功率和开关速度均较低。所以,除非FPGA或DSP产生类似于PC处理器的负载阶跃或解耦网络的尺寸太大或成本太高,确定解耦网络尺寸的经验法则是在设计的最优度和快速上市之间进行合理的折衷。

本文小结

对于多轨应用,要在线性稳压器和各种类型的开关转换器之间做出合适的选择,不仅需要综合考虑尺寸、效率和成本,也必须考虑通电顺序和启动电流管理等问题。另外,为了在负载阶跃暂态过程中保持调节,转换器很可能需要借助于解耦电容。

作者:Jeff Falin,德州仪器, Email: j-falin1@ti.com

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...