引言

随着电子技术的进步,数字电视也得到了迅猛发展,其中视频数字编解码芯片是它的核心部件,而ADC又是影响其性能的关键模块,因此设计高性能的模拟前端ADC成为Ic设计的挑战。本文设计了一种在12位精度、80MHz采样率的ADC中负责采样保持的核心电路-运算跨导放大器(OTA)。

运放结构的选择

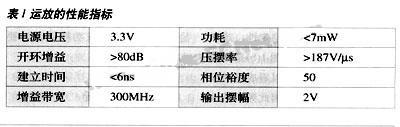

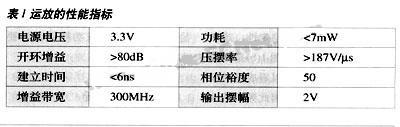

根据ADC的要求可以推算出运放的性能指标,如表1所示,据此可以选择运放的结构。

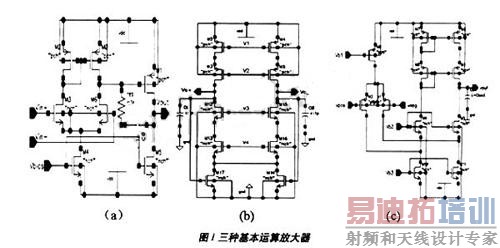

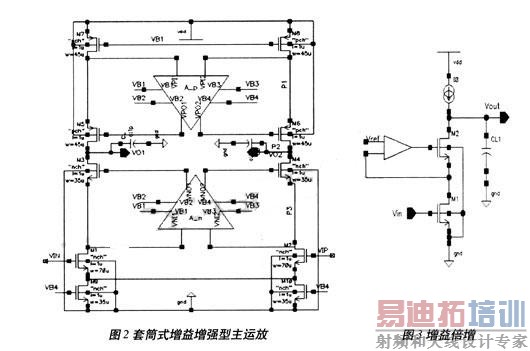

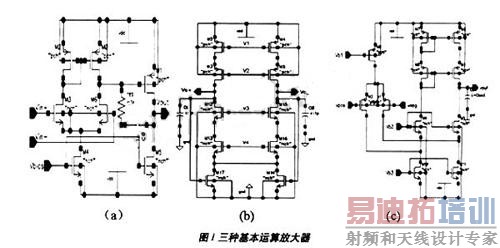

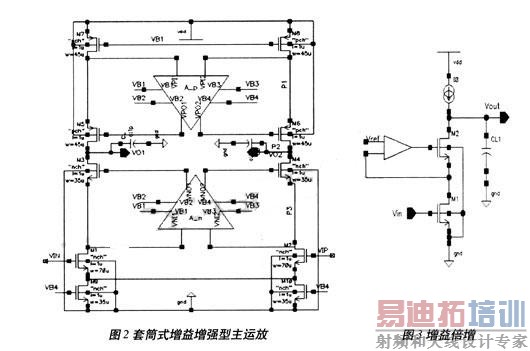

目前常见的三种基本的运算放大器结构如图所示。图 1(a)是简单的两级运放,它具有火的输出摆幅2(Vdd-2Vds,sat),但频率特性差,一般用Miller法补偿,使得相位裕度变小,但会导致电路稳定性变差。另一种改进的补偿方式是增加调零电阻R2=l/Cc(1/gmb-R),但由于工艺的不稳定性,难以得到精确的电阻值。图1(b)是套筒式运放,整个电路可以看成是单极点系统,无需补偿,因此频率特性好;又因为它只有2条主支路,因此功耗低,但输入/输出摆幅小。图1(c)是折叠式共源共栅结构,它改进了套筒式输入/输出摆幅小的缺点,但存在4条主支路,功耗大且稳定性变差。综上所述,本文结合图l(b)、(c)的优点,设计了全差分套筒式增益增强型运放,如图2所示,它能满足高增益带宽、低功耗等设计要求。

电路原理分析

增益倍增

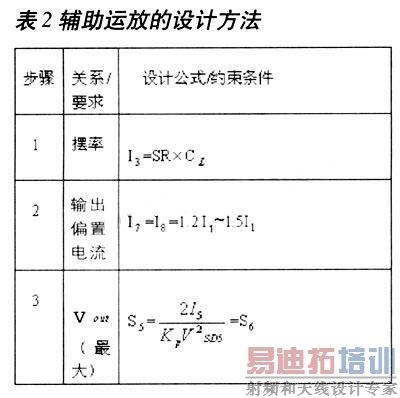

为了提高增益,在共源共栅结构上附加辅助运算放大器,如图3所示,可以增强共源共栅效应。辅助运放的放大倍数为Aadd,通过减小由输出到输入管漏极的反馈,输出可增大Aadd。倍,也即等效于:Rout≈(gm2rds2(Aadd+1)+1)rdsl+rds2。其中,g m2是M2管跨导,rds1与rds2:分别为Ml与M2的输出阻抗。因此电路的直流增益也会增大同样的倍数,Av=gm1Rout≈-gm1rds2 (gm2rds2((Aadd+1)+1)。

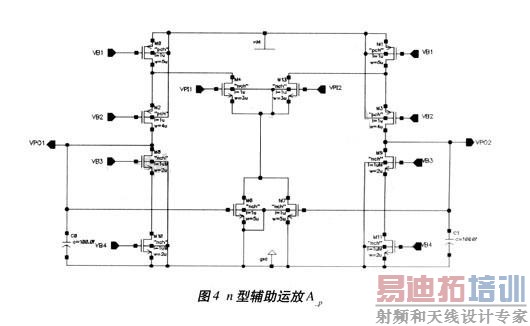

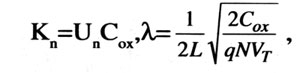

同理,给图2中的套筒式主运放加上辅助运放后,其直流增益可提高为Av=-gm1[(gm5rds5 rds7 (Aadd_p)// (gm3rds3 (rds9// rds1) Aadd_n)分别是辅助运放Aadd_n和Aadd_p。的放大倍数。图4中示了n型辅助运放A_p的结构。

p型辅助放A_n用于推进主运放的M 3、M4管,n型辅助运放A_p.用于推 进主运放的M5、M6管。辅助运放采用折叠式结构,不需要太快的速度和建立时间,因此其尾电流取为主运放的l/10,大大降低了整个电路的功耗和面积。 频率响应分析

图2中全差分套筒式共源共栅运放的主极点在P.点,频率为Wpl=-l/RoutCL;次极点位于P2或P3点。通常由于p管的迁移率比n管的迁移率小,因此p管的过驱动电压较大,导致宽长比W/L。也较大,即P2点的电容比P3的电容大。因此可以认为P2点为次主极点,wP2=-gm5/cp,其中gm5为M5管的跨导,Cp主要包括M5管的栅源电容c。。和M3管的栅漏电容Ggd。而主运放的单位增益频率为WU=gm1/CL。,其中gm1为M1管的跨导。当加入辅助运放时,附加的增益部分与M5管形成闭环,若附加增益部分速度太快,电路就可能变得不稳定。又因为辅助运放增加了一对零极点Wdoiblet,如果设计不好,就会严重影响运放的建立特性。因此应使这对零极点尽量靠近,并且尽量远离主运放的单位增益频率,同时还要小于主运放的次主极点,即:βWU Wdoublet WP,其中β是闭环反馈系数。

主运放和辅助运放的设计方法

在设计套筒式共源共栅主运放时,首先根据最大输出摆幅的要求,分配过驱动电压Vod并设置静态工作点。由图可得:Vout.max=Vdd一(|Vod7|+|Vod5 |),Vout.min=Wod9+Voal+Vod3,设输出摆幅为1.5V,则|Vod7|+|Vod5 |+Vod9+V0d1+Vod3=3.3-1.5=1.8V,由于p管M7、M5的迁移率低,给它们均分配0.45V的过驱动电压,剩余的平均分配给M9、M1、M3各0.3V。再由阀值电压公式Vgs=Vt+Vod知:允许的最小输入共模电平等于Vgsl+Vod9=1V,VBl的最小值为Vgs3+Vodl+Vod9=1.3V,Vod5的最大值为:VDD-(|Vgs5+Vod7|)=1.6V。因此,综合考虑合理设置其偏置电压VB4、VIN VG3、VG5、VBl分别为:0.8V、1.2V、1.79V、1.6V、2.21V。

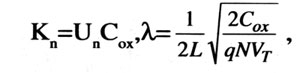

在进行电路设计时,首先需要手工估算宽长比W/I。,这可以根据C M 0 S管饱和电流公式IDS=Kn(W/L一)(VGs一VTN)2(1+λVDS)得到,式中器件跨导参数  其中COX为单位面积的氧化层电容,N为衬底掺杂浓度,Un为n沟道器件的表面迁移率。同理可计算P管参数。

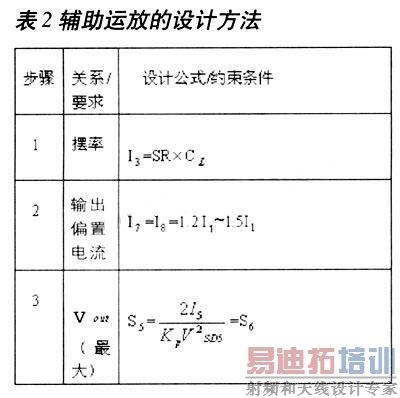

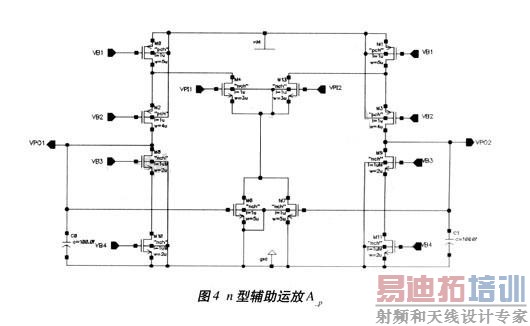

折叠式共源共栅辅助运放的设计方法如表2所示,其中设宽长比Sn=(W/L)n。 仿真验证和结论

在Cadence的Spectre平台下,本设计采用TSMc公司的0.35μmCM0s工艺模型,在3.3V电源电压下,分别在tt(典型)、sr(慢NMOS,快PMOS)、ff(快NMOS,快PMOS)3种工艺条件下对所设计的运放进行了仿真。仿真结果表明,本文采用的增益增强型套筒式共源共栅结构的全差分cM0s运算放大器具有llOdB的直流开环增益,320MI-Iz的增益带宽,65。的相位裕度,压摆率大于200V/lxs,建立时间小于6ns,功耗小于5.7mW。 结语

本文对增益提高技术的原理和全差分套筒式共源共栅运算放大器进行了分析,在此基础上设计了一个带增益提升的全差分折叠式共源共栅运算放大器,它能有效地提高增益,同时对运算放大器的速度及稳定性等影响很小。因此,该运放达到了设计性能的要求,可以运用于高速、高精度的ADC等。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:自动电平控制(ALC)为扬声器提供有效保护

下一篇:一种新型ZCS-PWM

Buck变换器研究

射频工程师养成培训课程套装,专家授课,让您快速成为一名优秀的射频工程师【More..】

射频工程师养成培训课程套装,专家授课,让您快速成为一名优秀的射频工程师【More..】

网站地图

| | | | | |