- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高性能nanoDAC AD5611的原理及应用

概述

AD5611是一款易控制、小尺寸、低功耗的10位DAC,在5V时的最大工作电流为100μA,并保证有单调的性能。在节电模式下,AD5611工作电压为3V时的功耗电流小于100nA,芯片还可通过软件选择输出负载。AD5611利用通用三线串口将时钟频率上升到30MHz,同时与SPI、QSPI、MICROWIRE、DSP等接口标准兼容。AD5611的基准电压源来自电源输入,因此获得了很宽的动态输出范围,该部分同时合并了加电复位电路,确保无输入信号时DAC的输出端电平始终保持为0V。AD5611具有轨到轨输出缓冲放大器,可实现0.5V/μs的转换速率,还具有同步中断控制功能。

由于以上这些特点,使AD5611很适合作为电压准位设定,主要用于消费类电子产品和手持设备、数字增益和偏移量调整、可编程电压源、可编程电流源和可编程衰减器等场合,例如数码相机、PDA、手机音量控制或背光显示屏亮度控制等。

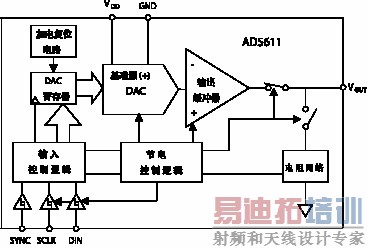

AD5611的内部结构如图1所示,芯片由施密特触发输入电路、基准源、加电复位电路、移位寄存器、输入控制逻辑、节电控制逻辑模块、输出缓冲放大器及电阻网络等部分组成。

设计要点

AD5611的内部主要器件为DAC移位寄存器、电阻网络和输出缓冲放大器。由于输入到DAC的数据是直接二进制格式,因此,从理论上得到的输出电压应该为,其中,VDD是芯片的工作电源电压,D是输入二进制数据的十进制形式。

AD5611的三线串口(SYNC、SCLK和DIN)可兼容SPI、QSPI、MICROWIRE接口协议标准。AD5611为单向通信,只有外部的写操作,当SYNC由高电平跳至低电平时,通信开始,DIN在SCLK时钟信号的控制下,在SCLK的下降沿将数据输入16位移位寄存器。只有当16位数据全部输入寄存器,即SCLK的第16个下降沿过后,移位寄存器才将最新的数据加载进去,从而完成一次完整的写操作。在串行数据输入过程中,SYNC必须保持为低电平,直到通信结束,否则,写操作无效。如果在对AD5611进行一次写操作后,紧接着要进行第二次写操作,那么在第一次写操作完成后至少应保持33ns的高电平,以使SYNC能产生一个下降沿来启动下一次写时序。

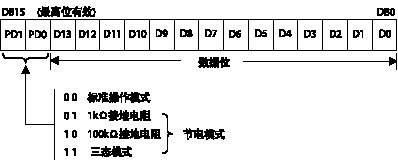

输入移位寄存器为16位宽度,如图2所示。PD0位和PD1位是控制位,用以控制功率操作模式(标准模式或三种节电模式中的一种模式)。D0~D13位是数据位,在SCLK波形的第16个下降沿时传输至DAC寄存器。

AD5611有四种独立的工作模式,工作模式的选择通过软件设置寄存器的DB15和DB14位来完成,工作模式和真值表的对应关系见图3中。AD5611在标准模式下,输出端VOUT输出与数字量成正比的模拟电平;而在节电模式下,其输出端VOUT将在芯片内部通过一个电阻接地或保持开路。节电模式下的三种工作模式分别为输出端接1kΩ电阻到地、输出端接100kΩ电阻到地、输出端断开电路(三态)。

节电模式被激活时,偏压发生器、输出放大器及其他相关的线性电路将全部关闭,但DAC寄存器中的内容不受影响。在VDD=5V和VDD=3V两种情况下,退出节电模式的时间分别对应为2.5μs和5μs。

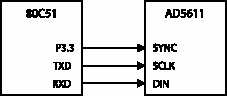

飞利浦公司生产的80C51单片机在微控制器领域有着十分广泛的应用,而AD5611的通用三线串口可方便地与其接口。图3给出了AD5611与80C51单片机传输数据的接口原理图。当RXD信号驱动AD5611的串行数据线(DIN)时,TXD信号则用来作为串行时钟线(SCLK)的驱动信号。当数据传输到AD5611时,P3.3应被置为低电平。因为80C51是以8位数据(1字节)作为数据传输的单位,所以传输周期只经历8时钟的下降沿。为了将数据加载到转换器,当前8位数据传输完毕时,P3.3就应该置为低电平,启动一个新的写周期以传输下一个字节。当完成一个写周期后,P3.3即变为高电平。传输数据时,80C51先输出数据的最低有效位(LSB),而AD5611则只能先接收数据的最高有效位(MSB),这一点是在对80C51编程时需要加以考虑的。

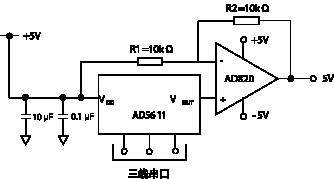

前面介绍到AD5611为单极性电源操作,但在实际应用中也可通过运算放大器等相关元件和AD5611组成双极性电压输出D/A转换电路。图4所示电路是由AD5611和运算放大器AD820组成的双极性电压输出D/A转换电路,其数字量0x0000对应于模拟输出电压的-5V,而0x3FFF则对应+5V的模拟输出电压。输出电压可根据下式计算得到:

这里,D表示输入数据的十进制形式。

结束语

AD5611具有接口简单、使用方便、便于精密输出控制等特点,同时又具备很低的功耗,能够满足当前系统对低功耗、小封装和低成本的要求。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...