- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

实用的调频接收机电路设计

录入:edatop.com 点击:

本设计主要由以下三部分组成:一、音芯片CXA1691,它是集调幅、调频、锁相环、立体声解码等电路为一体的AM/FM立体声收音IC。二、相环芯片BU2614,通过合理设计环路滤波器,频率能够稳定在88~108MHz。三、DC-DC变换电路,实现了系统的低功耗和单电源供电。

系统硬件电路设计

1 接收电路设计

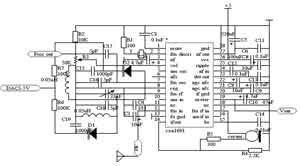

CXA1691S的电源电压适应范围宽,2~10V范围内电路均能正常工作,此外,它还具有立体声指示LED驱动电路以及FM静噪等功能。由于本系统没有涉及到调幅,所以芯片中的16引脚(AM中频输入)、15引脚(波段选择)、10引脚(AM天线输入)和5引脚(AM本振)均悬空,也可接电容到地。将7引脚(FM本振)和12引脚(FM输入)与环路滤波器的输入相连,从而利用锁相环实现频率的可控。具体电路如图1所示。

系统硬件电路设计

1 接收电路设计

CXA1691S的电源电压适应范围宽,2~10V范围内电路均能正常工作,此外,它还具有立体声指示LED驱动电路以及FM静噪等功能。由于本系统没有涉及到调幅,所以芯片中的16引脚(AM中频输入)、15引脚(波段选择)、10引脚(AM天线输入)和5引脚(AM本振)均悬空,也可接电容到地。将7引脚(FM本振)和12引脚(FM输入)与环路滤波器的输入相连,从而利用锁相环实现频率的可控。具体电路如图1所示。

|

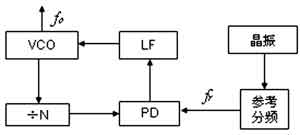

图1 CXA1691收音电路 2 锁相方案设计 本设计的第二个主要部分是锁相环电路的设计。在这里考虑了以下几种方案。 方案一:使用D/A控制压控振荡器产生可变的本振频率,该方案的调谐方式比较简单,很容易实现自动搜索功能,而且可以微调频率,使收音效果达到最佳状态。通过调试软件调试硬件,所以调试相对容易些。但它也有两个缺点:一是DAC产生的信号幅度是量化的,不能精确地锁定本振频率;二是没有环路控制,稳定性不及锁相环好。但是通过使用8位的DAC就可以使控制电压的步进为20mV,如果使用12位的DAC,则控制更精确。可见,上述两个缺点是可以克服的。 方案二:采用PLL频率合成方式。PLL频率数字调谐系统主要由压控振荡器 (VCO)、相位比较器(PD)、低通滤波器(LE)、可编程分频器和高稳定晶体振荡器组成,其结构如图2所示。其中参考分频器、PD以及可编程分频器可以全部集成在芯片BU2614内部,VCO振荡器输出fosc作为本振频率。BU2614可以用单片机来控制。高稳定度的晶振使得本振频率稳定性极大地提高,而且通过单片机控制分频系数也可以实现频率步进扫描、预置电台、电台存储等多种功能。

|