- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

全新的“智能功率”

录入:edatop.com 点击:

未来几年人们看待高科技界的方式将会发生巨大变化。我们现在刚开始认识到:电子工业将成为解决全球变温问题的一个主角。到目前为止,企业都在谈论降低能耗计划,但其实能够做的还有很多。从"智能功率"(Power Smart) 芯片和系统的设计,到形成整个电子工业的能效指导标准,新的功率范例要求电子工业承担降低能耗的责任,从而提高能效,最终降低温室气体排放。

"功率"概念正在变化

在上世纪90年代,谈到"功率"时,都是指为某一系统提供功率,或者说向一块PC板卡提供电压和电流。而对大多数人来说,"低功耗"也只涉及一些对功耗在乎的产品,而且很多都只是纸上谈兵,通常成功率甚微。

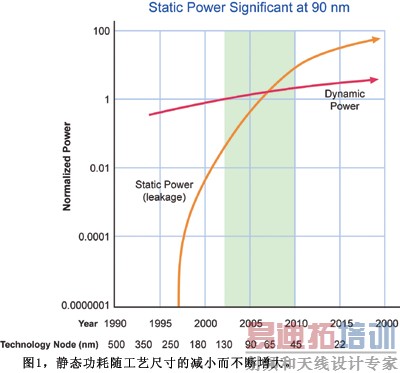

半导体器件的功耗有两种基本形式,即动态功耗和静态功耗。静态功耗是部件不做任何有用工作时的功耗,而动态功耗 则是器件主动工作时的功耗。直到最近,动态功耗都是整个功耗的主要部分。器件电源电压 (Vcc) 曾一度借助于动态功耗管理技术,以及工艺尺寸的减小和系统电压的降低而不断降低,但这种继续降低的日子已不复存在。此外,越来越小的集成电路 (IC) 工艺尺寸加剧了电流泄漏,使器件功耗大幅增加。随着泄漏电流的加剧,静态功耗开始成为功耗的主要部分,成为人们最关心的问题 (图1)。

不幸的是,为电子设备供电需要发电,而发电所产生的温室气体排放对全球变暖这个严重问题的影响高得惊人。根据联合国2007年5月的报告,即使采取强有力的抑制措施,到本世纪末全球平均温度也将升高多达华氏11度。

因此,业界各电子厂家都在讨论如何降低从芯片到系统的整个统一体的能耗,希望有助于环境保护。尽管电子业界已采取了一些环保措施 (如无铅及RoHS标准),但还是未能充分地解决功率问题。电子器件中有少量铅的确是个问题,但其影响较之于由全球温度失控变暖而造成的灾难还是很轻微的。

值得注意的是,到目前为止美国环保总署 (EPA) 还没有针对半导体产品设定Energy Star 标准。虽然这些半导体产品直接影响Energy Star评级产品的能效和管理,但业界一直未形成一个确定"低功耗"IC功效基准的方法。如果针对半导体产品提出功耗要求,就可最大限度地降低板卡、系统和最终产品的功耗,从而提高功效和减少温室气体。

显然,这个问题的解决方案有一部分握在电子行业手中。有了当今的智能功率技术,业界能够做到的更多。业界承担这个责任是必需的,责无旁贷。新的"功率"概念意味着从芯片到系统整个统一体降低功耗的协同作战。

智能功率芯片

依赖电池供电的便携设备设计人员现正面临一个可怕的挑战,即消费者对于产品尺寸更小、功能更丰富、电池寿命更长、价格更低及推出产品的周期更短等永无止境的追求。电池寿命延长意味着消费者的拥有成本降低。如果智能电话的电池寿命能正常供电6个小时,又如果锂离子电池通常在充电300次~500次后才需要 "破费地"被更换,那么,如果能将电池寿命由6小时延长到数周或数月,这样的产品岂不是更有吸引力?

便携产品的设计人员过去依赖于面向特定应用集成电路 (ASIC) 实现其低功耗目标。但ASIC固有某些负累,即掩模工艺昂贵和开发周期较长。设计人员的另一个选择是可编程逻辑解决方案,尤其是基于SRAM技术的可编程逻辑器件,这种器件缩短了开发周期,但也有不足之处,如静态功耗高。事实上,当今市场上的一些所谓"低功耗"FPGA和CPLD (复杂可编程逻辑器件) 的电流消耗达30mA,这通常比典型便携应用所能容忍的耗电高出1个~2个数量级。

基于SRAM技术的器件在上电启动时还会产生电涌,导致额外的电池消耗或造成系统初始化失败。不仅如此,由于基于SRAM技术的FPGA的晶体管密度极高,半导体工艺尺寸每次缩小,其静态功耗都会增加;这是因为尺寸缩小后,量子隧道效应和亚阈值区漏电之类的问题变得越发严重;这对面向便携应用的器件是个实实在在的挑战。如果采用那些利用 Flash 技术来配置SRAM内容的新型SRAM解决方案,功率问题还会更加复杂,虽然这种解决方案在市场上称之为基于 Flash 的器件,但还是需要在耗电巨大的SRAM FPGA上额外增加一些电路。

幸好,现在已有真正的 Flash可编程逻辑技术。由于基于 Flash的非易失性FPGA不需要数百万个耗电的SRAM存储位来配置数据,其静态功耗较之于基于SRAM的解决方案低很多,因而是低功耗应用的理想器件。事实上,市面上有一些基于 Flash 的FPGA是专门针对低功耗应用设计的产品。这类FPGA的静态功耗仅为5mW,提供更高的复杂性及更多功能,而且较之于CPLD,其静态功耗降低了四分之一,更可在便携应用中延长电池寿命达5倍。

Actel以 Flash 为基础IGLOO系列FPGA的功耗是当今最好的SRAM FPGA的1% ~ 0.1%。降低2个~3个量级的静态功耗意味着电池可应对数周到数月的待机运行。就电池供电的便携应用开发而言,基于 Flash 的器件还有一些其它优点,包括能够迅速恢复工作状态的灵活节能模式、低动态功耗及时钟管理功能。

智能功率芯片不仅功耗低,还可以智能化方式控制和降低整体系统功耗 。例如,混合信号Actel Fusion可编程系统芯片可将FPGA逻辑与其它用于系统管理的元件 (如Flash、模拟电路、微控制器及时钟管理电路) 集成在一起。这种集成产品能减少板卡上的部件,降低整体功耗及部件材料成本,同时还可对系统进行精细的功率管理。

智能功率系统

通常在设计某种系统时,都会设定功耗指标。然而,当设计人员能"大概"满足这个指标后,通常都不会再尽力改进设计,因而留下功耗缺陷的隐忧。由于电子设备的产量往往多达数亿,每个设备多浪费几瓦就意味着巨大的能源浪费,加上汽油价格上涨,最终会对环境造成影响。不幸的是,一般很难跟踪每个部件的功耗或电压,使得消除器件的多余功耗的工作变得非常困难。而且,在系统工作时,也几乎无法测量这些电压、电流和温度,使得判别系统何时出现问题的工作更为复杂。

越来越多新标准的出现,如ATCA (高级电信计算架构)、MicroTCA以及智能平台管理接口 (IPMI),表明我们需要系统层面和企业层面的功率管理。这些应用需要实时测量电压、电流和温度及发现问题的能力;记录和交换这些测量数据的能力;以及适时采取纠正措施的能力。毕竟,仅仅知道电源提供了多余的电流或板卡温度太高是无用的,还需要采取措施来纠正。

系统管理过去采用多芯片解决方案来实现。这类设计需额外增加10个~15个芯片,即耗费财力,又占用宝贵的板卡空间,还要额外耗电,因此实在不算是一种"解决方案"。多芯片方案还要耗费可观且通常是稀缺的工程技术资源。可是,业界却无视这些可观的成本,在管理和控制系统功耗方面一直努力甚少。

在意识到"全能普适"是世界上最大的谎言后,人们似乎明白需要采用现场可编程解决方案。使用基于 Flash 技术的单芯片现场可编程器件是实现简单及低成本系统管理解决方案的最好方法。这种具有上电即用的器件在市场已有供应,能减少系统的部件数量,并完成系统功率管理。由于具有现场可编程能力,这种灵活的器件还能轻松满足各种独特需求,并可应对项目、系统、板卡和工程师的需求变更。采用非易失性存储技术的混合信号Actel Fusion 可编程系统芯片则进一步降低了工程技术资源需求,是包括软件和硬件的完整解决方案。

而且,由于这种芯片集成了必要的管理功能 (如启动和上电顺序管理、功率管理),因此系统成本得以降低。构建智能功率系统的前期投入少,运行成本也大幅降低。由于每年节省1W的能量就会使系统运行成本节省1美元~2美元,在企业层面开发高成本效益的功率管理解决方案就能节省数量惊人的能量,从而节省大量金钱,而且,更重要的是对环境还有极大好处。

智能功率解决方案一例

电机在当今生活中几乎无处不在,从电梯到家用电器。2005年,美国的电力消耗为40550亿千瓦小时。其中50% 以上用于电机消耗,即达到惊人的2万亿千瓦小时。不幸的是,许多使用中电机的效率都很低,将供应的电能浪费了一大部分。

随着半导体工艺和集成度的提高,混合信号FPGA开始成为实现电机控制的重要替代产品。这类集成度高、灵活性强的平台能提供电机控制所需的大多数资源,且集成在低成本的单芯片器件上。采用FPGA替代固定逻辑产品,设计人员能够灵活地实现针对应用的最高效设计,并可将相同器件用于不同的电机。

"功率"概念正在变化

在上世纪90年代,谈到"功率"时,都是指为某一系统提供功率,或者说向一块PC板卡提供电压和电流。而对大多数人来说,"低功耗"也只涉及一些对功耗在乎的产品,而且很多都只是纸上谈兵,通常成功率甚微。

半导体器件的功耗有两种基本形式,即动态功耗和静态功耗。静态功耗是部件不做任何有用工作时的功耗,而动态功耗 则是器件主动工作时的功耗。直到最近,动态功耗都是整个功耗的主要部分。器件电源电压 (Vcc) 曾一度借助于动态功耗管理技术,以及工艺尺寸的减小和系统电压的降低而不断降低,但这种继续降低的日子已不复存在。此外,越来越小的集成电路 (IC) 工艺尺寸加剧了电流泄漏,使器件功耗大幅增加。随着泄漏电流的加剧,静态功耗开始成为功耗的主要部分,成为人们最关心的问题 (图1)。

不幸的是,为电子设备供电需要发电,而发电所产生的温室气体排放对全球变暖这个严重问题的影响高得惊人。根据联合国2007年5月的报告,即使采取强有力的抑制措施,到本世纪末全球平均温度也将升高多达华氏11度。

因此,业界各电子厂家都在讨论如何降低从芯片到系统的整个统一体的能耗,希望有助于环境保护。尽管电子业界已采取了一些环保措施 (如无铅及RoHS标准),但还是未能充分地解决功率问题。电子器件中有少量铅的确是个问题,但其影响较之于由全球温度失控变暖而造成的灾难还是很轻微的。

值得注意的是,到目前为止美国环保总署 (EPA) 还没有针对半导体产品设定Energy Star 标准。虽然这些半导体产品直接影响Energy Star评级产品的能效和管理,但业界一直未形成一个确定"低功耗"IC功效基准的方法。如果针对半导体产品提出功耗要求,就可最大限度地降低板卡、系统和最终产品的功耗,从而提高功效和减少温室气体。

显然,这个问题的解决方案有一部分握在电子行业手中。有了当今的智能功率技术,业界能够做到的更多。业界承担这个责任是必需的,责无旁贷。新的"功率"概念意味着从芯片到系统整个统一体降低功耗的协同作战。

智能功率芯片

依赖电池供电的便携设备设计人员现正面临一个可怕的挑战,即消费者对于产品尺寸更小、功能更丰富、电池寿命更长、价格更低及推出产品的周期更短等永无止境的追求。电池寿命延长意味着消费者的拥有成本降低。如果智能电话的电池寿命能正常供电6个小时,又如果锂离子电池通常在充电300次~500次后才需要 "破费地"被更换,那么,如果能将电池寿命由6小时延长到数周或数月,这样的产品岂不是更有吸引力?

便携产品的设计人员过去依赖于面向特定应用集成电路 (ASIC) 实现其低功耗目标。但ASIC固有某些负累,即掩模工艺昂贵和开发周期较长。设计人员的另一个选择是可编程逻辑解决方案,尤其是基于SRAM技术的可编程逻辑器件,这种器件缩短了开发周期,但也有不足之处,如静态功耗高。事实上,当今市场上的一些所谓"低功耗"FPGA和CPLD (复杂可编程逻辑器件) 的电流消耗达30mA,这通常比典型便携应用所能容忍的耗电高出1个~2个数量级。

基于SRAM技术的器件在上电启动时还会产生电涌,导致额外的电池消耗或造成系统初始化失败。不仅如此,由于基于SRAM技术的FPGA的晶体管密度极高,半导体工艺尺寸每次缩小,其静态功耗都会增加;这是因为尺寸缩小后,量子隧道效应和亚阈值区漏电之类的问题变得越发严重;这对面向便携应用的器件是个实实在在的挑战。如果采用那些利用 Flash 技术来配置SRAM内容的新型SRAM解决方案,功率问题还会更加复杂,虽然这种解决方案在市场上称之为基于 Flash 的器件,但还是需要在耗电巨大的SRAM FPGA上额外增加一些电路。

幸好,现在已有真正的 Flash可编程逻辑技术。由于基于 Flash的非易失性FPGA不需要数百万个耗电的SRAM存储位来配置数据,其静态功耗较之于基于SRAM的解决方案低很多,因而是低功耗应用的理想器件。事实上,市面上有一些基于 Flash 的FPGA是专门针对低功耗应用设计的产品。这类FPGA的静态功耗仅为5mW,提供更高的复杂性及更多功能,而且较之于CPLD,其静态功耗降低了四分之一,更可在便携应用中延长电池寿命达5倍。

Actel以 Flash 为基础IGLOO系列FPGA的功耗是当今最好的SRAM FPGA的1% ~ 0.1%。降低2个~3个量级的静态功耗意味着电池可应对数周到数月的待机运行。就电池供电的便携应用开发而言,基于 Flash 的器件还有一些其它优点,包括能够迅速恢复工作状态的灵活节能模式、低动态功耗及时钟管理功能。

智能功率芯片不仅功耗低,还可以智能化方式控制和降低整体系统功耗 。例如,混合信号Actel Fusion可编程系统芯片可将FPGA逻辑与其它用于系统管理的元件 (如Flash、模拟电路、微控制器及时钟管理电路) 集成在一起。这种集成产品能减少板卡上的部件,降低整体功耗及部件材料成本,同时还可对系统进行精细的功率管理。

智能功率系统

通常在设计某种系统时,都会设定功耗指标。然而,当设计人员能"大概"满足这个指标后,通常都不会再尽力改进设计,因而留下功耗缺陷的隐忧。由于电子设备的产量往往多达数亿,每个设备多浪费几瓦就意味着巨大的能源浪费,加上汽油价格上涨,最终会对环境造成影响。不幸的是,一般很难跟踪每个部件的功耗或电压,使得消除器件的多余功耗的工作变得非常困难。而且,在系统工作时,也几乎无法测量这些电压、电流和温度,使得判别系统何时出现问题的工作更为复杂。

越来越多新标准的出现,如ATCA (高级电信计算架构)、MicroTCA以及智能平台管理接口 (IPMI),表明我们需要系统层面和企业层面的功率管理。这些应用需要实时测量电压、电流和温度及发现问题的能力;记录和交换这些测量数据的能力;以及适时采取纠正措施的能力。毕竟,仅仅知道电源提供了多余的电流或板卡温度太高是无用的,还需要采取措施来纠正。

系统管理过去采用多芯片解决方案来实现。这类设计需额外增加10个~15个芯片,即耗费财力,又占用宝贵的板卡空间,还要额外耗电,因此实在不算是一种"解决方案"。多芯片方案还要耗费可观且通常是稀缺的工程技术资源。可是,业界却无视这些可观的成本,在管理和控制系统功耗方面一直努力甚少。

在意识到"全能普适"是世界上最大的谎言后,人们似乎明白需要采用现场可编程解决方案。使用基于 Flash 技术的单芯片现场可编程器件是实现简单及低成本系统管理解决方案的最好方法。这种具有上电即用的器件在市场已有供应,能减少系统的部件数量,并完成系统功率管理。由于具有现场可编程能力,这种灵活的器件还能轻松满足各种独特需求,并可应对项目、系统、板卡和工程师的需求变更。采用非易失性存储技术的混合信号Actel Fusion 可编程系统芯片则进一步降低了工程技术资源需求,是包括软件和硬件的完整解决方案。

而且,由于这种芯片集成了必要的管理功能 (如启动和上电顺序管理、功率管理),因此系统成本得以降低。构建智能功率系统的前期投入少,运行成本也大幅降低。由于每年节省1W的能量就会使系统运行成本节省1美元~2美元,在企业层面开发高成本效益的功率管理解决方案就能节省数量惊人的能量,从而节省大量金钱,而且,更重要的是对环境还有极大好处。

智能功率解决方案一例

电机在当今生活中几乎无处不在,从电梯到家用电器。2005年,美国的电力消耗为40550亿千瓦小时。其中50% 以上用于电机消耗,即达到惊人的2万亿千瓦小时。不幸的是,许多使用中电机的效率都很低,将供应的电能浪费了一大部分。

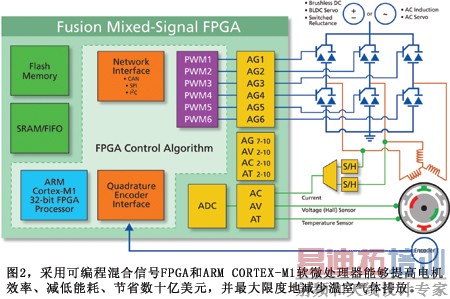

随着半导体工艺和集成度的提高,混合信号FPGA开始成为实现电机控制的重要替代产品。这类集成度高、灵活性强的平台能提供电机控制所需的大多数资源,且集成在低成本的单芯片器件上。采用FPGA替代固定逻辑产品,设计人员能够灵活地实现针对应用的最高效设计,并可将相同器件用于不同的电机。

小型AC交流电机的效率可能会低到50%。虽然,随着电机尺寸增加,其效率也增加到90%以上,但仍然还有提高效率和降低能耗的空间。通过引入智能化的负载匹配技术或变频控制技术,可以提高电机在整个速度范围的功效。采用可重编程混合信号FPGA和用软件方式优化的微控制器 (如ARM7或ARM Cortex-M1处理器),就可以在许多类型的电机上达到这个目的,而且实现成本对大多应用都具有吸引力。事实上,在最佳情况下采用此技术,电机效率可接近95%;如果大规模应用,美国年度能耗便可降低3,000亿千瓦小时,即节省数十亿美元,并减少温室排放气体1.8亿吨(图2)。

结论

近20年来,功率的概念已发生巨大变化。同时,各种电子设备大量涌现。可悲的是, 为这些电子设备供电而发电所产生的温室气体排放,对全球变暖造成的影响高得惊人。

业界各电子厂家都在讨论如何降低能耗,希望这样会有助于环境保护,但其实我们能够做到的更多。无论是智能功率芯片和系统的设计,还是形成整个电子工业的能效指导标准。新的功率范例要求电子工业承担降低能耗的责任,从而提高能效,最终减少温室气体排放。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:第三方IP:SoC设计的一种不稳固基础

下一篇:电压检测电路对锂离子电池组的影响

射频和天线工程师培训课程详情>>