- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

flash接口电路的实现

我们在进行嵌入式系统设计的过程中,根据需求,要设计出特定的嵌入式应用系统,而嵌入式应用系统的设计包含硬件系统设计和软件系统设计两个部分,并且这两部分设计是互相关联、密不可分的,嵌入式应用系统的设计经常需要在硬件和软件设计之间进行权衡与折中。因此,这就要求嵌入式系统设计者具有较深厚的硬件和软件基础,并具有熟练应用的能力。在整个设计过程中,硬件设计是系统设计的基础和核心,而各功能部件在整个设计中的调试又是该环节的重点和难点。本文详细介绍嵌入式系统Flash存储器的接口电路的调试。

1 Flash存储器接口电路的引脚信号及各项特性

1.1 Flash存储器接口电路的特点

Flash存储器是一种可在系统(In-System)中进行电擦写,掉电后信息不会丢失的存储器。它具有低功耗、大容量、擦写速度快、可整片或分扇区在系统编程(烧写)、擦除等特点,并且可由内部嵌入算法完成对芯片的操作,因而在各种嵌入式系统中得到了广泛的应用。作为一种非易失性存储器,Flash在系统中通常用于存放程序代码、常量表以及一些在系统掉电后需要保存的用户数据等。常用的Flash为8位或16位数据宽度,编程电压为单3.3V。主要有ATMEL、AMD、HYUNDAI等生产厂商,他们生产的同型器件一般具有相同的电气特性和封装形式,可通用。

1.2以HY57V641620为例的SDRAM接口电路的基本特性

本文以Flash存储器HY29LV160为例,简要描述一下Flash存储器的基本特性:

HY29LV160的单片存储容量为16M位(2M字节),工作电压为2.7V~3.6V,采用48脚TSOP封装或48脚FBGA封装,16位数据宽度,可以以8位(字节模式)或16位(字模式)数据宽度的方式工作。

HY29LV160仅需单3V电压即可完成在系统的编程与擦除操作,通过对其内部的命令寄存器写入标准的命令序列,可对Flash进行编程(烧写)、整片擦除、按扇区擦除以及其它操作。

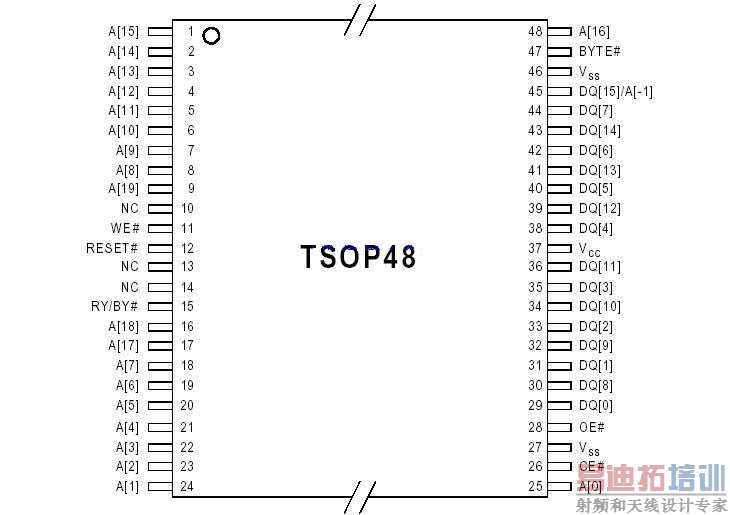

HY29LV160的逻辑框图、引脚分布及信号描述分别如图1和表1所示:

图1 HY29LV160引脚分布(TSOP48封装)

表1 HY29LV160的引脚信号描述

| 引 脚 | 类型 | 描 述 |

| A[19:0] | I | 地址总线。在字节模式下,DQ[15]/A[-1]用作21位字节地址的最低位。 |

| DQ[15]/A[-1] DQ[14:0] | I/O 三态 | 数据总线。在读写操作时提供8位或16位数据的宽度。在字节模式下,DQ[15]/A[-1]用作21位字节地址的最低位,而DQ[14:8]处于高阻状态。 |

| BYTE# | I | 模式选择。低电平选择字节模式,高电平选择字模式 |

| CE# | I | 片选信号,低电平有效。在对HY29LV160进行读写操作时,该引脚必须为低电平,当为高电平时,芯片处于高阻旁路状态 |

| OE# | I | 输出使能低电平有效输出使能,低电平有效。在读操作时有效,写操作时无效。 |

| WE# | I | 低电平有效写使能,低电平有效。在对HY29LV160进行编程和擦除操作时,控制相应的写命令。 |

| RESET# | I | 硬件复位,低电平有效。对HY29LV160进行硬件复位。当复位时,HY29LV160立即终止正在进行的操作。 |

| RY/BY# | O | 用就绪/忙 状态指示。用于指示写或擦除操作是否完成。当HY29LV160正在进行编程或擦除操作时,该引脚位低电平,操作完成时为高电平,此时可读取内部的数据。 |

| VCC | -- | 3.3V电源 |

| VSS | -- | 接地 1.3 以HY29LV160为例的Flash接口电路的使用方法 下面,我们使用HY29LV160来构建存储系统。由于ARM微处理器的体系结构支持8位/16位/32位的存储器系统,对应的可以构建8位、16位、32位的Flash存储器系统。32位的存储器系统具有较高的性能,而16位的存储器系统则在成本及功耗方面占有优势,而8位的存储器系统现在已经很少使用。下面主要介绍16位和32位的Flash存储器系统的构建。 射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师... 天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:超低压差CMOS线性稳压器的设计 射频和天线工程师培训课程详情>>

|