- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

如何构建仪表放大器

典型的被测信号可以是生物信号,如心电图(ECG)信号或者是来自诸如惠斯登电桥等传感器的微弱信号。由于这些信号源常常具有几千欧姆或更高的输出阻抗,因此仪表放大器需要具有很高的输入阻抗(典型数值在千兆欧姆级)。此外,由于仪表放大器往往要驱动输入阻抗很低的后级电路,如A/D转换器等,因此要求仪表放大器的输出阻抗很低。仪表放大器工作频率通常在直流到1 MHz之间,而在MHz级的速度下,输入电容比输入电阻更为重要,因此这类应用要考虑使用差分放大器。这种差分放大器输入阻抗较低,但速度要快很多。

常见仪表放大器

差动放大器

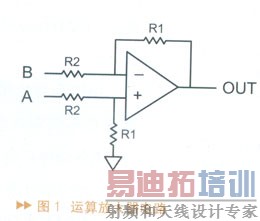

差动放大器不是仪表放大器,但是有时可以用在仪表放大器的场合。其电路只需一个运算放大器,如图1所示。在对高输入阻抗或者增益没有苛刻要求的场合,使用它是很方便的。

该电路的传递函数为:

Vout=R1/R2(VA-VB)

这一传递函数是在理想运算放大器和理想电阻器匹配条件下得出的。然而,当电阻不完全匹配时,同相放大电路和反相放大电路的传递函数不相等,就会有共模信号泄露出来。以0.1%的电阻匹配误差为例,最差情况下CMRR为54 dB,即10 V的共模信号会产生20 mV的输出误差。

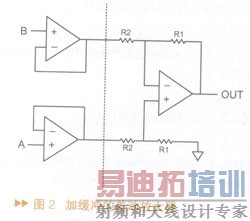

差动放大器的优点是结构简单,最主要的缺点是输入阻抗很低。由于增益由R1/R2决定,因此需要在高增益和高输入阻抗间做出折中。此外,将信号分压变小后再进行放大(如同相通路),并不是获得良好噪声性能的方法。对于反相通路而言,加入了额外的电阻,并且反相放大电路的噪声增益总比信号增益高。提高输入阻抗就要求增加电阻的数值,这样将会产生更多的噪声。最后,共模抑制比也受到限制。为了改善这些缺点,第一步是对输入进行缓冲,这样就解决了输入阻抗的问题,如图2所示。

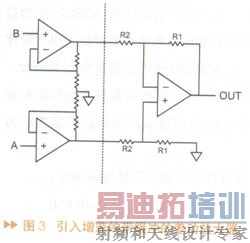

在对输入进行缓冲的同时,如果引入一些增益,除了可以得到高阻抗,还会产生很好的噪声性能,如图3所示。

电路中差动放大器的噪声仍然存在,但折算到输入端时噪声要除以第一级的增益。由于可以使用阻值非常小的电阻器,因此第一级的噪声可以做得非常低,而且不影响输入阻抗。这种结构的另外一个好处是在高增益时有较宽的带宽。原因是电压反馈放大器具有一定的增益带宽乘积,通过把增益分散到两级放大器,可使每一级的增益比较低,降低差动放大器级的增益,从而不会被增益带宽乘积所限制。然而还有一个没解决的问题就是共模抑制比。图3的电路将共模信号和差分信号都放大了,而所有的共模抑制都在差分放大级实现,因此,很容易超过第一级的输入电压范围。

三运放仪表放大器

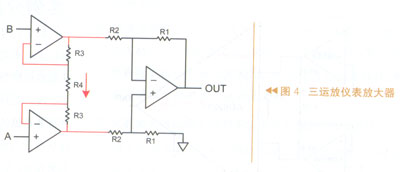

将图3中第一级放大电路中的接地点去掉来解决共模抑制的问题,从而构成三运放结构仪表放大器,如图4所示。

第一级电路让共模信号有效地通过,没有任何放大或衰减,第二级差动放大器将共模信号去除。由于额外提升了差分增益,虽然电阻器的匹配状况并没有改善,但是系统的有效共模抑制能力却得到了增强。在实际应用中需要注意:

1)必须在第一级提供增益;

2)系统的共模抑制不是由前两个放大器的共模抑制比性能决定的,而是取决于两个共模抑制的匹配程度。然而双运算放大器从来不会给出这一指标,因此选择时必须要求CMRR性能指标比需要的目标性能指标至少好6 dB;

3)如果电阻器有某些对地的泄露通路,CMRR指标就会降低;

4)仪表放大器前面的元件要尽可能设计得平衡。如果仪表放大器同相通路中低通滤波器和反相通路中低通滤波器具有不同截止频率,系统的CMRR特性将会随着频率的升高而降低。

对于仪表放大器的第一级,每个运算放大器都要保持其两个电压输入端的电压相同。图4中R4两端的差分电压应当和两个输入端的电压相同,这个电压产生一个电流,流过电阻器R3并产生了放大器的增益。

三运放仪表放大器通常会遇到的问题有:

1)这一结构放大差分信号,然后去除共模信号。两级电路之间的中间节点载荷着大约一半的差分信号再加上共模信号。须确保这个信号处于运放的工作范围之内。当改变输入电压的共模成分时,如果看到类似于饱和的现象,则应首先检查这里。

2)流过R4的电流。当把仪表放大器的增益设置得很高时,R4就会很小,这意味着差分电压很大的时候,R4上产生的电流也会相当大。需要检查这种情况对系统是否有负面作用。

3)反馈通路中的电容。反馈通路的走线应尽可能地短,反馈通路过大的电容在高频时会使共模抑制比性能降低。

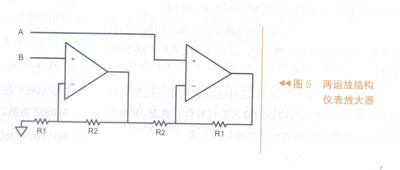

如果不需要三运放结构如此高的性能,可使用两运放结构进行简化。这种结构的主要优点是结构简单,它只需要两个运算放大器和四个电阻器,如图5所示。由于很少有包含三个运放的器件,因此三运放结构通常需要使用一个四运放器件。而多余的一个运放需要消耗更多的功率,所以两运放结构在能耗方面也会更低。此外,和三运放结构一样,两运放结构电路也具有很高的输入阻抗。但是两运放仪表放大器的性能要差一些,通过计算分析,这种结构的共模抑制比对电阻器阻值变化的灵敏度比差分放大器结构略高一些。最坏情况下,对于0.1%的电阻器匹配条件下的CMRR不是54 dB,而是50.5 dB。与三运放仪表放大器不同的是这个CMRR数值不随增益的增加而改善。由于两个通路不平衡,同相通路信号的频率响应与反相通路信号不同。由于反相通路要通过两级电路而不是一级电路,因此在反相通路中出现了一个相位延迟,并且压摆率和带宽特性也会不同,其噪声性能也会差一些。

1)由于第一级的输出电压即放大了的输入电压,其中包括共模电压,因此需要注意第一级的输出电压;

2)由于两运放仪表放大器的CMRR对于电阻的匹配情况极为敏感,因此需要注意电阻器的匹配;

3)高频性能。因此,对于这三种结构来说:差动放大器 这种放大器很好,也很简单,只需要一个运算放大器和四个电阻器。然而,它的输入阻抗与所选电阻器的数值有关,而且噪声和CMRR的性能也较差。

2)三运放仪表放大器 第一级电路提供高输入阻抗。当我们在第一级电路中引入增益时,还提高了噪声和CMRR的性能。

两运放结构仪表放大器 这种电路结构比三运放结构简单得多,并且也具有很好的输入阻抗特性。然而,其噪声和CMRR性能不能随着增益的增加而改善。

实例分析:混合设计

如果已经找到了基本符合要求的仪表放大器,但某一指标无法满足需求,此时可以利用现有仪表放大器加上辅助电路达到目的。

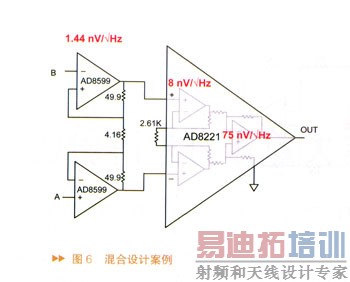

噪声是仪表放大器的一个重要指标,现在很多运放都具有非常低的噪声系数,如果要求更低的噪声,则可以采用分立设计方法构建仪表放大器。然而这需要花费很大的精力来设计、布局和调试,而得到的共模抑制比又低于单芯片仪表放大器。图6所示的混合设计节省了设计时间和电路板空间,同时得到了与单芯片仪表放大器同样好的共模抑制性能。

这里所示的混合设计分为三级:运放组成的前置放大器,后面是仪表放大器。每一级的噪声都比前一级大,然而,由于为每一级都分配了增益,所以各级对系统最后的噪声没什么影响。如果用一个2.61 K的电阻将AD8221的增益设定为20,也可以将所有的增益都放在前置放大级,而使AD8221的增益为1。而AD8599的增益带宽积为10MHz。如果将总的增益都放在第一级,那么其带宽将会被限制在20 kHz。在两个元件之间分配增益,得到总带宽大约为300 kHz。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:太阳能电池及材料研究

下一篇:电子连接器接触电阻测试程序