- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

外部电源设计中新技术与芯片的应用

最近几年电源产品已经取得了突破性的进步,但与此同时,当今能源浪费的问题已成为国内外越来越关注的问题,它反映在以下几个方面:

⑴ 突出的问题包括:使用矿物燃料的能源资源是有限的,获取能源的成本也在增加,矿物燃料的消耗也带来其它负面影响(即环境污染),而可替代能源资源还没有成热;

⑵ 所有的家电产品和电子设备都要消耗电力;

⑶ 不断增长的个人用电子产品通过使用适配器和充电器[外部电源(EPS)]也在消耗能源外部电源。

每年到底消耗多少能源呢 能源浪费的数量估算每年销售的EPS为10亿个以上;估算正在使用的EPS为100亿个低效线性电源所占EPS的百分比为46%(几乎一半)。如世界上某发达国家每年EPS浪费的能源(30~60)BkW/小时,约浪费(25~50)亿美金,它等效于26个中等规模的电厂。

2 用节能理念来推动或重新设计

电源在轻载时的高效率是关键因素。工作模式的效率是当电源工作在25%、50%、75%及100%负载时效率的平均值。在整个负载范围内持续的高效率比重载时的高效率更加重要,最理想的控制方案是随负载的降低频率也相应地降低。

为了解决电源系统提供更高的能量利用效率,国际上颁布了许多标准,如国际能源署"1W计划"、美国新版能源之星、美国80PLUS等。有哪些新的EPS能效标准呢?

新的外部电源(EPS)能效标准:适用于所有功率从小于1W到250W的单路输出的外部电源(EPS);等同于Energy Star(EPA)标准(CEC,CECP,AGO,EU);同时适用于AC-DC和AC-AC适配器及充电器;美国其它的州也会用的标准/法规正在进行中;中国CECP标准从2005年1月1日开始生效;在澳大利亚从2006年4月1日开始生效;欧盟从2007年1月1日也将采用标准中工作模式时的相应规定。

随着这些新标准的出台,对电源设计有了新的挑战。为此,需要有新的举措来面对新的挑战。首先就是要用节能理念来推动或重新设计。即:节能已成为一个重要的设计要求;而今60%的现有方案都无法满足新标准的要求;关于外部电源(EPS)的节能标准已经颁布;不少公司新推出的产品系列能令您的设计符合所有日前及提议中的标准.再则要用新技术来应对设计挑战,如为了降低待机模式的能耗,安森美半导体则侧重于其他技术,如跳周期待机模式,PWM控制器主控PFC(轻载时关断PFC以降低待机能耗)。此外,将诸多新技术和功能集成到芯片内,如DDS(动态自供电)、频率抖动、Soxy-less(无线圈去磁检测)等,可起到简化外围电路设计的作用,也相应减少了功率损耗。值此仅就选择节能芯片和利用智能电源管理技术节省能源二个方面加以研对。

3 节能芯片的选择

3.1 Link Switch-LP器件特点及工作方式

⑴ LinkSwitch-LP系列的产品特性

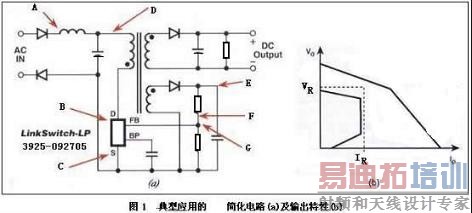

易于设计、外围元件数目很少的解决方案;原边电路控制器在负载超过峰值功率点时限制了输出电流,无需电流检测电阻;完善的故障保护—过热、短路及开环;可在通用输入电压范围(85VAC-265VAC)内操作;图1为典型应用的简化电路(a)及输出特性(b),突出的特点是节能技术:无需任何附加元件,轻松达到全球所有的节能标准;在265VAC输入时的空载能耗<150mW;开/关控制可在极轻负载时具备恒定的效率,是达到强制性CEC标准的理想选择。

⑵ LinkSwitch-LP的系统成本优势

从图1可知:频率抖动降低了EMI,采用简单的EMI滤波;电感既用于滤波又用于保险丝功能,见图1中A点部分;内部高压恒流源省去了启动和偏置电路,见图1中B点部分;内部电流检测电路省去了外围的电流检测电阻,见图1中c点部分;严格的器件参数公差,低的限流点,允许初级绕组上不使用箱位电路,见图1中D点部分;低成本的变压器反馈稳压,见图1中E点部分;输出电压由分压电阻决定,有精确的FB脚电压,见图1中F点部分;开/关操作不需要频率补偿元件,见图1中G点部分。针对有最低成本要求,且对恒压/恒流要求宽松的应用进行了优化。

3.2典型应用

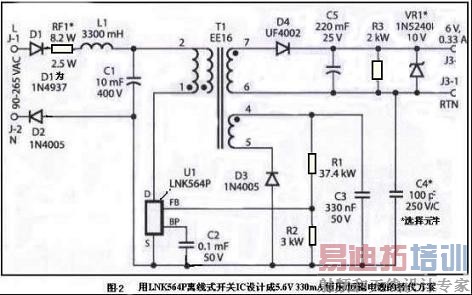

图2显示的是一个典型的用LNK564IC构成的6V 330mA恒压/恒流(CV/CC)输出电源电路的替代方案。以下对方案特点作一分析。

[p]

⑴ 输入电路

AC输入差模滤波可由C1和L1形成的极低成本的输入滤波器得以实现。LNK564的频率抖动特性省去输入pi(C、L、C)滤波元件,仅需要一个大容量电容。加上一个套管还可使输入电感L1既用作保险丝,又用作一个滤波元件。这一简单的滤波保险丝输入级更进一步地降低了系统成本。另一个可选方案是用一个保险丝电阻RFl来提供保险丝的功能。

在某些应用中如果允许EMI的裕量较低及/或降低的输入耐浪涌能力,那么可以从中线上去掉输入二极管D2。在这类应用中,D1需要是一个耐压为800V的二极管。

⑵ 关于LNK564开/关控制

该设计采用简单的偏置绕组(T1脉冲变压器的1和2端)电压反馈方式,由LNK564进行开/关控制。当开关关闭时,由R1及R2形成的电阻分压器决定了脉冲变压器T1偏置绕组的输出电压。在V/I曲线[见图1(b)]上的恒压工作区域,LNK564器件使能/禁止开关周期以维持FB引脚的电压为1.69V。二极管D3及低成本陶瓷电容C3提供初级反馈绕组(T1/3.4)电压的整流滤波功能。当加重的负载超出恒定功率阈值,FB引脚电压开始随电源输出电压的下降而降低。内部振荡器频率在这一区域内线性下降,直到达到启动频率50%为止。当FB引脚电压下降到低于自动重启动阈值(FB引脚通常为0.8V,这相当于电源输出电压在1V到1.5V之间),电源将关断100ms,然后再重新开启100ms。它将会持续进行这一工作模式直到FB脚超过自动重启动阈值。这一功能在输出短路的情况下可降低平均输出电流。

该方案中,可将C3提高到0.47mF或更高来进一步降低空载耗。

由于LNK564中使用了限流调节技术从而使得限流点公差非常精确,同时采用较新的变压器结构技术得以在初级电路中实现无箝位电路的设计。峰值漏极电压在265VAC输入时可以控制在550V之下,对700V耐压(BVDss)的MOSFET管来说有非常大的裕量。

⑶ 输出整流管的选择

输出的整流滤波由输出整流管D4和滤波电容C5来实现。由于自动重启动特性,平均短路输出电流大大低于1A,因而可以使用低成本的D4整流管。输出电路只要能处理电源输出短路时的持续短路电流就可以了。二极管D4为超快恢复型二极管,用来优化输出V/I特性。备选电阻R3作为假负载,在空载输出时将输出电压加以限制。尽管存在这个假负载,空载能耗在265VAC时仍能保持在140mW左右的目标范围内。通过将R3的值提高到2.2kW或更高,就可满足更低的空载能耗要求,并同时可将输出电压限制在9V以下。如需要,可将备选的Zener(齐纳)嵌位二极管(VRl)安装在电路板的左侧的空白位置以便在开环情况下限制电源最大输出电压。

4 利用智能电源管理技术节省能源

近几年来,电源管理技术有飞跃的发展,可供选择的设计方案也越来越多。政府环保团体及消费者不断向电子产品厂商施加压力,敦促他们在增加产品功能的同时,也必须降低系统的能耗。目前,便携式电子产品市场的发展尤其令人瞩目。例如,无线通信产品不断推陈出新,功能也越趋多样化,是带动整个市场发展的功臣。照目前的发展趋势看,移动电话、个人数字助理、MP3播放机、数字相机及便携式电子游戏机都朝着外型更小、速度更高、功能更齐备的方向发展。为了确保/通话时间/(即电池寿命)可以延长至满意的水平,工程师便一直致力于改善电源供应子系统的设计。

便携式电子产品的电池寿命取决于两个关键因素,其一是电源转换效率,而另一个因素是系统的能源管理方法。电源转换系统负责将电池的供电电压尽量以最高的效率转为设计规定的供电干线电压,而能源管理系统则针对实际的应用情况,实时提供刚好能满足其需要的供电,以节省能源。

4.1利用Power Wise技术降低能耗

新—代的节能技术侧重于调节处理器的频率及电压以降低能耗。对于以电池供电的系统来说,究竟系统能否长时间处于开启状念,取决于其能耗的大小。单单降低其频率只会减少其平均功耗,但不会减少某一计算上作所需耗用的能源。系统电压必须调低,才可真正是节省能源。动态电压调节(DVS)及自适应电压调节(AVS)这两种电源管理技术都可降低系统电压.

⑴ 什么是自适应电压调整?该技术有哪些优点?

用于跟踪系统处理器性能变化的嵌入式自适应电源控制器(APC)作出自适应电压调整。APC通过一个Power Wise高速低电源接口将系统处理器的频率、温度和处理变化准确地传递给外部适应电源管理芯片。然后,该电源管理单元根据性能需求自动调整系统处理器的供给电压。以前的电压调整方案都是开环回路。CPU控制在频率/电压检查表中维护的电压,通过一个专用接口和电源管理电路来提供电压。检查表中的值是否是假与最糟糕情况下的值。自适应电压调整减轻了CPU干扰并降低了闭环回路方式的电压。Power Wise技术提供的自适应电源管理与ARM的Intelligent Energy Manager提供的准确动态性能设置相结合,提供了空前理想的结果。

⑵ 动态电压调节(DVS)技术先是将不同的电压及频率配对成不同的组合,调节时便根据实际需要挑选最适用的电压/频率组合。

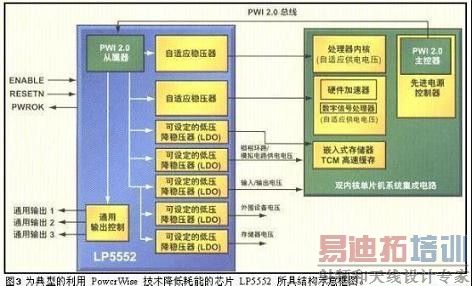

己可提供多款电源管理集成电路PMIC,其中包括可支持DVS模式的LP3906、LP3907,以及可支持DVS和AVS两种模式的LP5550、P5551及LP5552。动态电压调节(DVS)技术可以节省耗电及能源,还为供电电压预留一些额外的空间,以支持不同工艺及温度的系统,这个预留的额外空间虽然足以应付最环的情况,但实际应用时便会浪费较多耗电。我们只要关闭系统的电源供应环路,控制环路便可灵活调节操作电压,并将之降至最低,以便尽量节省能源。Power Wise技术便是利用这个方法节能。

4.2 Power Wise特征

Power Wise接口(PW)可以支持智能的能源管理系统。Power Wise是一种针对系统整体需要的能源管理技术,确保以电池供电的电子产品可利用自适应电压调节(AVS)技术以及控制不同状态的切换。Power Wise技术采用闭环AVS系统搭配高速的串行电源管理总线,确保处理器无论在任何时候,以任何频率操作,都可采用最低的电压,以便将动态能耗降至最低。

Power Wise技术也可为处理器的电位提供偏压。由于供电电压Vdd已调低,以减少动态损耗,晶体管的阈值电压也必须调低,以确保驱动电压可以保持在较高的水平,但缺点是漏电与静态功率损耗会增加。只要为电位阱提供反向偏压,漏电便会减少。此外,以同—供电电压(Vdd)为例来说,也为电位阱提供正向偏压,以提高驱动电压。

可以支持Power Wise闭环AVS功能的标准系统配置必须有以下的基本元件:内置于处理器之内的先进电源控制器、设有PWI从属器的电源管理集成电路,以及将两者连接一起的双线PWI串行总线。电源管理集成电路负责为处理器提供电压,电压大小则由先进电源控制器内的PWI主控器负责调节,辨法是由主控器将有关的命令传往PWI从属器,再由相关的电路进行调节。

先进电源控制端负责接收主处理器的命令,为电压控制过程提供一个不受处理器影响的操作环境,以及实时跟踪逻辑电路的操作速度。先进电源控制器永远处于戒备状态,不断监测系统的一切参数,例如,系统温度、负载、瞬态、工艺及其他有关的变动都会受到监测。每当先进电源控制器收到有关频率即将转变的消息,便会先行做出研判,以确定若以新频率操作,系统最少需要多少供电才称为可稳定操作。整个过程由闭环电路负责监控,例如先进电源控制器先将电压调节命令经由PWI接口传送到PWI从属器,然后再由伺服装置将电压凋节到适当的水平。

其技术参数如下:LP5552输出数目为7;输出电压及电流有:2个降压稳压器为0.8v到1.235v输出电压,800mA的输出电流;5个降压稳压器为0.8v到3.3v输出电压,高达250mA的输出电流。输入电压范围为2.7V至4.8V。接口为PWl 2.0。封装为micro SMD-38。

4.3 Power Wise技术应用

Power Wise®技术是先进的能源管理解决方案,主要针对当前和未来受能源所限制的数字设备,适用于双内核处理器、手机、便携式收音机、个人数字助理、以电池供电的电子产品以及便携式设备。可将数字处理器的能耗降低70%,从而延长电池寿命、支持更多功能和改善使用者的体验。Power Wise采用自适应电压调节(AVS)和阈值电压调节等技术,将数字逻辑集成电路的工作和泄漏功耗自动降至最低,同时保持最小的系统开销。

Power Wise技术提供在单芯片系统和支持组件之间的一种优化的闭环回路,而无需CPU干涉。嵌入式Power Wise技术因为可以合成,所以可不受处理器影响。

5 结束语——电源排序技术也是一种较为理想之节能方案

除上述选择节能芯片和利用智能电源管理技术节省能源二个方面之外,需指出的是对于不同类型的产品其节能技术方式也有所不同。而电源排序技术的应用也是一种较为理想之方案。因为在很多大功率系统中,空间和冷却系统的成本都很高。因此,就任何POL转换器而言,做到紧凑、高效率并具有低静态电流以满足新的"绿色"标准都是极端重要的。另外,很多微处理器和数字信号处理器(DSP)都需要一个内核电源和一个输入/输出(1/O)电源,这些电源在启动时必须排序。设计人员必须考虑加电和断电操作时内核和I/O电压源的相对电压和时序,以符合制造商的性能规格要求。没有恰当的电源排序,就可能出现闭锁或过大的电流消耗,这有可能导致微处理器I/O端口损坏,或存储器、可编程逻辑器件(PLD)、现场可编程门阵列(FPGA)、数据转换器等支持性器件的I/O端口损坏。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:韩国

LED

路灯工程采用Golden

DRAGON

Plus

LED

的GALED

路灯

下一篇:PIC单片机原理