- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高性能CMOS集成电压比较器设计

录入:edatop.com 点击:

电压比较器是对输入信号进行鉴幅与比较的电路,其功能是比较一个模拟信号和另一个模拟信号(参考信号),并以输出比较得到的二进制信号。其在A/D转换器、数据传输器、切换功率调节器等设备中有着广泛的应用。在高速度、高精度A/D转换器中,比较器的精度和速度直接影响转换电路的转换精度和转换速度等关键指标;在数据传输器中,比较器的性能对数据传输的误码率有着很大的影响;在切换功率调节器中,调节器的功率调节性能在很大程度上依赖于电压比较器的性能。因此,是高工作频率、高增益、低失调电压、高性能的电压比较器,在模拟集成电路和数/模混合集成电路中十分重要。仿真结果表明,该电压比较器适用于高速A/D转换器、高速数据传输器及高性能切换功率调节器等设备中。

1 比较器电路设计

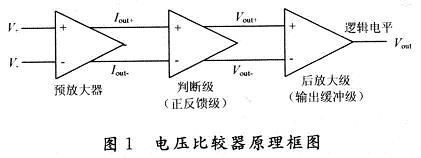

这里介绍的电压比较器是传统的预放大锁存比较器,采用预放大器、锁存比较器和输出缓冲级级联的方式来实现,其原理框图如图1所示。

1.2 锁存比较电路

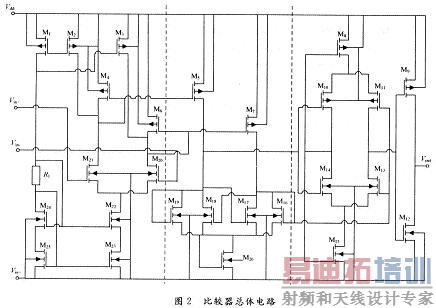

锁存比较电路是整个比较器的核心部分,它应能区分毫伏量级的输入信号差。如图2中第二部分所示, M17,M18交叉互连实现正反馈,以提高比较电路的增益。利用前级预放大器的输出,控制锁存器输入电流I+,I_的变化,若I_远大于I_,则M16和 M18导通,Vout-△0,Uout+=(2L16I+/WμnCox)+VTHN;若I_增大而I+减小,M18的漏一源电压升高,当高到M17的 VTHN时,M17导通,此时M17管开始抽取原来流过M16管的电流,这会使M16管的漏一源电压下降,并导致M18管截止,电路的输出状态发生转换。当I-增大到一定程度时会导致M18进入饱和区,此时临界电流值I-=(I+)(W17μnCox/L17)/(W16μnCox/L16),该电流临界点也是输出电压发生转换的临界点。同理可得,当I+增大时,发生转换的电流临界点I+=(I-)(W17μnCox/L17)/ (W16μCox/L16)。

1.3 输出缓冲驱动级

输出缓冲驱动级(又称后放大器)的主要作用是把锁存比较电路的输出信号转化成逻辑电平(0 V或5 V)。如图2中第三部分所示,M8,M10,M11,M13,M14,M15组成差分自偏置电路,它能吸人和供出较大的电流,使比较器在驱动大的容性负载时速度不受摆率的限制。M9,M12组成一个反相器,用作附加的增益级,同时实现负载电容和自偏置差分放大器之间的隔离。要使输出缓冲级工作在线性区,输入信号的幅度一般要在1~3.5 V之间,所以在电路中串入M26管来提升锁存器输出电压的幅值。

2 电路仿真

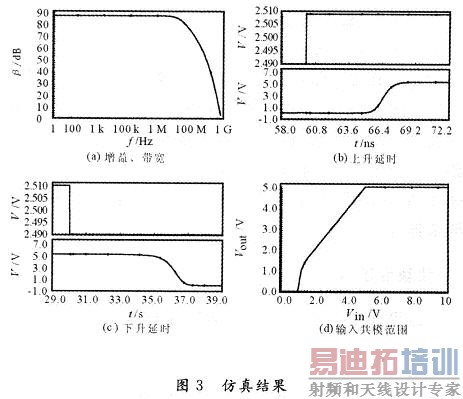

在5 V电源的电压下,Vin-端加2.5 V参考信号,在Cadence软件平台下用Spec-tre工具对基于CSMC 0.5 μmCMOS工艺模型的电路进行仿真,得到比较器的增益、带宽、上升延时、下降延时、输入共模范围如图3所示。

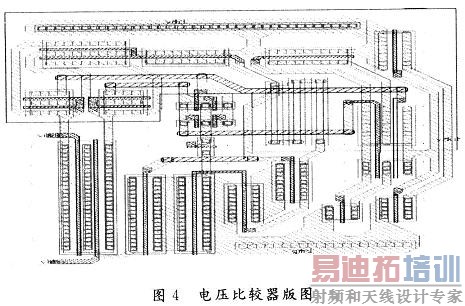

集成电路的版图是芯片在实际制作时物理掩模图形的集合,是从电路原理图到实际芯片的关键过渡环节。版图的设计直接影响着芯片的最终性能。模拟集成电路版图的设计要求更高,它不仅有技术成分,还需要许多艺术性的布局和走线。

基于CSMC 0.5μm CMOS(N-Well硅栅)工艺设计的集成电压比较器版图如图4所示。其中电阻为制作在N-well中的P+扩散条;MOS管为NORMAL器件,其沟道宽长为多晶硅栅覆盖有源区部分的宽长。包围有源区的N+diff和P+diff,用来表明管子是NMOS管,还是PMOS管,版图面积为57μm×69 μm。

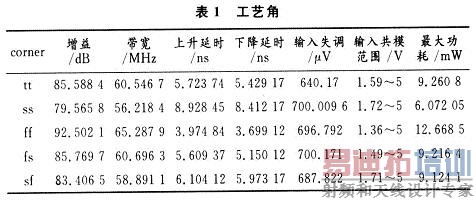

在CSMC O.5μm CMOS工艺条件下,采用预放大器、锁存比较电路和输出缓冲级级联的锁存比较电路结构,设计了一个高速、高精度的高性能集成电压比较器,它具有低输入失调电压、低功耗的特点。完成从电路原理图设计到版图设计和验证(DRC,LVS)以及工艺角仿真和分析的整个设计流程。从仿真结果可以看出,这一高性能电压比较器适用于高速A/D转换器、高速数据传输器及高性能切换功率调节器等设备中。

1 比较器电路设计

这里介绍的电压比较器是传统的预放大锁存比较器,采用预放大器、锁存比较器和输出缓冲级级联的方式来实现,其原理框图如图1所示。

![]()

1.2 锁存比较电路

锁存比较电路是整个比较器的核心部分,它应能区分毫伏量级的输入信号差。如图2中第二部分所示, M17,M18交叉互连实现正反馈,以提高比较电路的增益。利用前级预放大器的输出,控制锁存器输入电流I+,I_的变化,若I_远大于I_,则M16和 M18导通,Vout-△0,Uout+=(2L16I+/WμnCox)+VTHN;若I_增大而I+减小,M18的漏一源电压升高,当高到M17的 VTHN时,M17导通,此时M17管开始抽取原来流过M16管的电流,这会使M16管的漏一源电压下降,并导致M18管截止,电路的输出状态发生转换。当I-增大到一定程度时会导致M18进入饱和区,此时临界电流值I-=(I+)(W17μnCox/L17)/(W16μnCox/L16),该电流临界点也是输出电压发生转换的临界点。同理可得,当I+增大时,发生转换的电流临界点I+=(I-)(W17μnCox/L17)/ (W16μCox/L16)。

1.3 输出缓冲驱动级

输出缓冲驱动级(又称后放大器)的主要作用是把锁存比较电路的输出信号转化成逻辑电平(0 V或5 V)。如图2中第三部分所示,M8,M10,M11,M13,M14,M15组成差分自偏置电路,它能吸人和供出较大的电流,使比较器在驱动大的容性负载时速度不受摆率的限制。M9,M12组成一个反相器,用作附加的增益级,同时实现负载电容和自偏置差分放大器之间的隔离。要使输出缓冲级工作在线性区,输入信号的幅度一般要在1~3.5 V之间,所以在电路中串入M26管来提升锁存器输出电压的幅值。

2 电路仿真

在5 V电源的电压下,Vin-端加2.5 V参考信号,在Cadence软件平台下用Spec-tre工具对基于CSMC 0.5 μmCMOS工艺模型的电路进行仿真,得到比较器的增益、带宽、上升延时、下降延时、输入共模范围如图3所示。

集成电路的版图是芯片在实际制作时物理掩模图形的集合,是从电路原理图到实际芯片的关键过渡环节。版图的设计直接影响着芯片的最终性能。模拟集成电路版图的设计要求更高,它不仅有技术成分,还需要许多艺术性的布局和走线。

基于CSMC 0.5μm CMOS(N-Well硅栅)工艺设计的集成电压比较器版图如图4所示。其中电阻为制作在N-well中的P+扩散条;MOS管为NORMAL器件,其沟道宽长为多晶硅栅覆盖有源区部分的宽长。包围有源区的N+diff和P+diff,用来表明管子是NMOS管,还是PMOS管,版图面积为57μm×69 μm。

在CSMC O.5μm CMOS工艺条件下,采用预放大器、锁存比较电路和输出缓冲级级联的锁存比较电路结构,设计了一个高速、高精度的高性能集成电压比较器,它具有低输入失调电压、低功耗的特点。完成从电路原理图设计到版图设计和验证(DRC,LVS)以及工艺角仿真和分析的整个设计流程。从仿真结果可以看出,这一高性能电压比较器适用于高速A/D转换器、高速数据传输器及高性能切换功率调节器等设备中。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>