- ������ѵ,רע��������Ƶ��������ƹ���ʦ������

Keithley�������ף��뵼��C-V��������

¼�룺edatop.com �����

ͨ�ò���

����-��ѹ��C-V�����Թ㷺���ڲ����뵼�������������MOSCAP��MOSFET�ṹ�����⣬����C-V���������Զ��������͵İ뵼���������ս�����������������˫�����;���ܣ�BJT����JFET��III-V�廯���������������ء�MEMS�������л�TFT��ʾ�����������ܡ�̼���ܣ�CNT���Ͷ��������뵼��������

��������Ļ��������dz������ڸ���Ӧ�ú���ѵ����ѧ���о�ʵ���ҺͰ뵼�峧������������������²��ϡ��¹��ա����������µ�·��C-V�������ڲ�Ʒ��������ǿ����ʦҲ�Ǽ�����Ҫ�ģ����Ǹ�����߹��պ����������ܡ��ɿ��Թ���ʦ������������������Ϲ��������ղ���������ʧЧ���ơ�

����һ���ķ��������������������Եõ����ְ뵼�������Ͳ��ϵIJ��������������������Ķྦྷ��ʼ����Щ��Ϣ�������������ж����õ�����������ƽ������Ũ�ȡ����ӷֲ��������������Ȳ�������ԲƬ�����У�C-V���������ڷ���դ����ȡ�դ����ɡ������ӣ����ʣ��ͽ������ܶȡ��ں����Ĺ��ղ�����Ҳ���õ���������������̡���ʴ����ϴ������ʺͶྦྷ��������������ȡ�����ԲƬ����ȫ���������֮���ڿɿ��Ժͻ����������Թ����п�������C-V��������ֵ��ѹ������һЩ���������������������������ܽ��н�ģ��

�뵼����ݵ���������

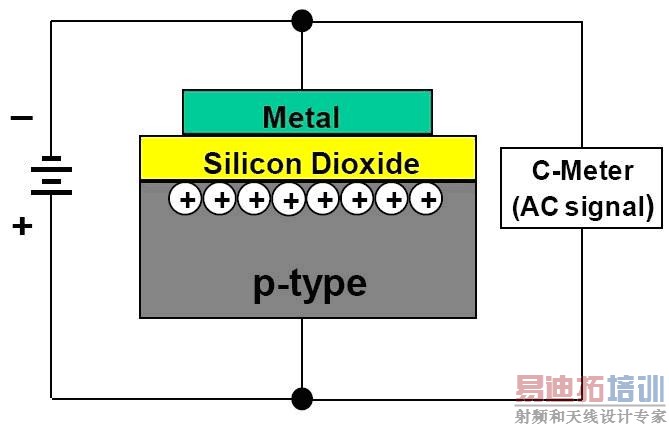

MOSCAP�ṹ���ڰ뵼������������γɵ�һ�ֻ��������ṹ����ͼ1��ʾ��������������������������ʵ��·�У���������ͨ��������Ϊһ�ֲ��Խṹ���������칤���С��������ֽṹ�Ƚϼ���������������ƣ��������������ײ㹤�յ�һ�ַ���ķ�����

ͼ1�еĽ���/�ྦྷ���ǵ��ݵ�һ�������������Ǿ�Ե�㡣���ھ�Ե������ijĵ���һ�ְ뵼����ϣ���������������ǵ��ݵ���һ����ʵ���ϣ����еĶ����������ǵ��ݵ���һ���������϶��ԣ�����C����ͨ�����й�ʽ�еı������������

C = A (κ/d), ����

A�ǵ��ݵ������

κ�Ǿ�Ե��Ľ�糣��

d�������ļ��

��ˣ�A �� κԽ��Ե����Խ��������ֵ��Խ�ߡ�ͨ�����ԣ��뵼����ݵĴ�С��Χ�Ӽ��ɷ�����Ƥ����������С��

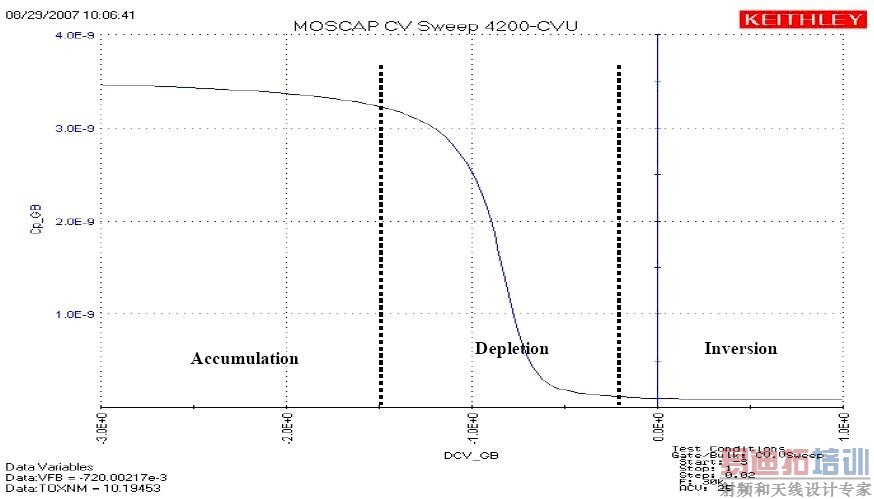

����C-V����ʱҪ�ڵ��ݵ���������ֱ��ƫѹͬʱ����һ�������źŽ��в�������ͼ1��ʾ����ͨ������£��������ʹ�õĽ���Ƶ�ʷ�Χ��10kHz��10MHz�������ص�ƫѹ��Ϊֱ����ѹɨ������MOSCAP�ṹ���ۻ�������ľ�����Ȼ����뷴��������ͼ2��ʾ����

[p]

ǿ���ֱ��ƫѹ���³ĵ��еĶ����������ھ�Ե����渽���ۻ�����������������Ե�㣬��˵���ɻ����ڽ��渽������dΪ��Сֵ��ʱ�������ۻ����ﵽ���ֵ����ͼ1��ʾ����C-V�ۻ��������Եõ���һ�������������Ƕ�������ĺ��tox��

��ƫѹ����ʱ�����������Ӵ���������汻�ų���ľ����γɡ���ƫѹ����ʱ�����������Զ��������ﵽ�����룬���ݴﵽ��Сֵ����dΪ���ֵ����������ʱ�ķ��������ݣ�������������������ӵ���������һ����ԭ��ͬ��������MOSFET����ܣ�ֻ�����ǵ������ṹ�Ͳ��Ӹ��Ӹ��ӡ�

��ƫѹɨ�����������Ĺ����л����Եõ�����������������ͼ2��ʾ�����ò�ͬ�Ľ����ź�Ƶ�ʿ��Եõ�����ϸ����Ϣ����Ƶ���Խ�ʾ��ν����̬����������Ƶ��������Ա��ֳ���̬���ܡ�������C-V����ͨ��������Ҫ�ġ�

������������

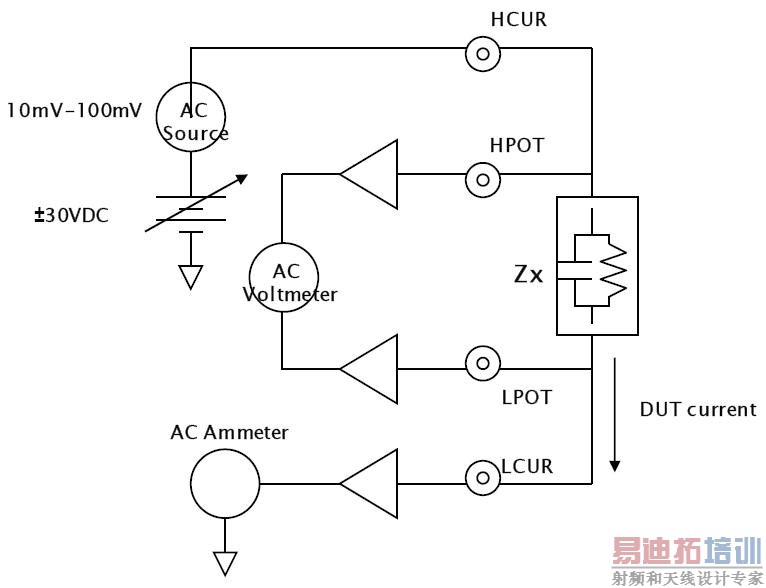

ͼ3�����˻���C-V�������õĿ�ͼ������C-V����ʵ�������ڽ���Ƶ���½��еģ���˴���������DUT���ĵ��ݿ��Ը������й�ʽ����õ���

CDUT = IDUT / 2πfVac������

IDUT������DUT�Ľ���������ֵ��

f�Dz���Ƶ�ʣ�

Vac�Dz�õĽ�����ѹ�ķ�ֵ����ǡ�

������֮�����ֲ���ͨ�����ؽ�����ѹȻ����������Ľ���������������ѹ������֮����迹��ǣ����ղ��DUT�Ľ����迹��

��Щ�����������������صĴ����벢�����裬�Լ���ɢ���ӣ�©������ͼ4����������������Բ������Ҫ��·������

z, theta���迹�����

R+jX��������翹

Cp-Gp������������絼

Cs-Rs���������������

���У�Z=�迹

D=��ɢ����

θ=���

R=����

X=�翹

G=�絼

[p]

�ɹ�C-V��������ս

C-V�������õĿ�ͼ��Ȼ����ȥ�dz����������ֲ���ȴ����һ������ս��һ����ԣ�������Ա�����漸������������鷳��

• �͵��ݲ�����Ƥ����С��ֵ��

• C-V����������ԲƬ����������

• ©���ݣ���D���IJ���

• ����Ӳ���������ɼ�����

• ������ȡ

�˷���Щ��ս��Ҫ��ϸע�����õļ����Լ����ʵ�Ӳ����������

�͵��ݲ����� ���C��С����ôDUT�Ľ�����Ӧ�����ͽϵͣ����Բ��������ǣ��ڽϸߵ�Ƶ���£�DUT�迹����С���Ӷ����������Ƚ����ײ������뵼�����ͨ���dz��ͣ�����1pF�������ںܶ�LCR���IJ�����Χ����ʹ��Щ�����ܹ�������ЩС����ֵ�IJ����ǿ���Ҳ������˵�����ɬ�Ѷ��������ж����յIJ������ȡ��������ȷ�����������������̵ľ��ȣ���ô�û���Ҫ��˶���ѯ�����̡�

��D��©�����ݡ��뵼����ݳ���Cֵ�ϵ�֮�⣬������й©���ص㡣������ݲ����ĵȼ۵���̫��ʱ�ͻ���������������ᵼ�µ������迹�����������迹��Cֵ����������û�����ھ��г���դ�����������D��ֵ���ܴ���5��һ����ԣ�����D�������ݲ����ľ���Ѹ���½�����˸�D��ʵ��ʹ�õ��ݼƵ�һ���������ء�ͬ�����ϸߵ�Ƶ�������ڽ����һ���⡣�ڽϸߵ�Ƶ���£��������迹�ϵͣ�ʹ�õ��ݵ����ϸߣ��������в�����

C-V�����Ļ�������������Ի����£�DUT����ԲƬ�ϵ�һ�����Խṹ����ͨ��̽������̽�뿨�������Ϳ��ؾ�������C-V�����ǡ���ʹû�п��أ���ȻҲ��ʹ��̽�����ʹ��������ߡ��ڽϸߵ�Ƶ���£�������������У���Ͳ���������ͨ������£�����ͨ�����ʹ�ÿ�·����·����У������ʵ�ֵġ�����Ӳ�������ߺͲ��������dz����ӣ���˾�����C-V����Ӧ�ù���ʦ���н�����һ���õİ취�������ó�ʹ�ø���̽��ϵͳ���˷����ֻ������⡣

��ȡ���õ����ݡ����������ľ������⣬C-V���ݲɼ���ʵ����Ҫ���ǵ����ذ������Ա������������̣�������ȡ�����Ķ���Ժ�Ӳ���������ԡ�һ����ԣ�C-V�����ѽ�����Լ30V��10mAֱ��ƫѹ�����ǣ��ܶ�Ӧ�ã�����LD MOS�ṹ��������������k�в����ʡ�MEMS�������л�TFT��ʾ���������ܣ���Ҫ�ڽϸߵĵ�ѹ������½��в��ԡ�������ЩӦ�ã���Ҫ�����ĸ�ѹֱ����Դ�͵��ݼƣ��ߴ�400V�IJ��ֱ��ƫѹ��0��±400V���ߴ�300mA�ĵ�������Ƿdz����õġ���C-V�����ǵ�HI��LO�˼��ز��ֱ��ƫѹ�ܹ������ؿ���DUT�ڵĵ糡������������������о��ͽ�ģ�Ƿdz����õģ���������Ԫ����

��������Ӧ�ð��������û���̿�ֱ��ʹ�õIJ������̡���ЩӦ�������ڴ�����㷺ʹ�õ��������պͲ��Լ�����������ǰ�������ἰ���й����ݡ���Щ�о��߿��ܻ��һЩ�������IJ��Ը���Ȥ�������MIM������-��Ե��-�������͵��ݽ���C-V��C-fɨ�裬����ԲƬ�ϵĻ���С���ݣ����߶�˫��������������C-Vɨ�衣�����Զ���ͼ�����ܹ������ʵ�ֲ�����ȡ�����磬��ͼ5��ʾ����

����-��ѹ��C-V�����Թ㷺���ڲ����뵼�������������MOSCAP��MOSFET�ṹ�����⣬����C-V���������Զ��������͵İ뵼���������ս�����������������˫�����;���ܣ�BJT����JFET��III-V�廯���������������ء�MEMS�������л�TFT��ʾ�����������ܡ�̼���ܣ�CNT���Ͷ��������뵼��������

��������Ļ��������dz������ڸ���Ӧ�ú���ѵ����ѧ���о�ʵ���ҺͰ뵼�峧������������������²��ϡ��¹��ա����������µ�·��C-V�������ڲ�Ʒ��������ǿ����ʦҲ�Ǽ�����Ҫ�ģ����Ǹ�����߹��պ����������ܡ��ɿ��Թ���ʦ������������������Ϲ��������ղ���������ʧЧ���ơ�

����һ���ķ��������������������Եõ����ְ뵼�������Ͳ��ϵIJ��������������������Ķྦྷ��ʼ����Щ��Ϣ�������������ж����õ�����������ƽ������Ũ�ȡ����ӷֲ��������������Ȳ�������ԲƬ�����У�C-V���������ڷ���դ����ȡ�դ����ɡ������ӣ����ʣ��ͽ������ܶȡ��ں����Ĺ��ղ�����Ҳ���õ���������������̡���ʴ����ϴ������ʺͶྦྷ��������������ȡ�����ԲƬ����ȫ���������֮���ڿɿ��Ժͻ����������Թ����п�������C-V��������ֵ��ѹ������һЩ���������������������������ܽ��н�ģ��

�뵼����ݵ���������

MOSCAP�ṹ���ڰ뵼������������γɵ�һ�ֻ��������ṹ����ͼ1��ʾ��������������������������ʵ��·�У���������ͨ��������Ϊһ�ֲ��Խṹ���������칤���С��������ֽṹ�Ƚϼ���������������ƣ��������������ײ㹤�յ�һ�ַ���ķ�����

ͼ1�еĽ���/�ྦྷ���ǵ��ݵ�һ�������������Ǿ�Ե�㡣���ھ�Ե������ijĵ���һ�ְ뵼����ϣ���������������ǵ��ݵ���һ����ʵ���ϣ����еĶ����������ǵ��ݵ���һ���������϶��ԣ�����C����ͨ�����й�ʽ�еı������������

C = A (κ/d), ����

A�ǵ��ݵ������

κ�Ǿ�Ե��Ľ�糣��

d�������ļ��

��ˣ�A �� κԽ��Ե����Խ��������ֵ��Խ�ߡ�ͨ�����ԣ��뵼����ݵĴ�С��Χ�Ӽ��ɷ�����Ƥ����������С��

����C-V����ʱҪ�ڵ��ݵ���������ֱ��ƫѹͬʱ����һ�������źŽ��в�������ͼ1��ʾ����ͨ������£��������ʹ�õĽ���Ƶ�ʷ�Χ��10kHz��10MHz�������ص�ƫѹ��Ϊֱ����ѹɨ������MOSCAP�ṹ���ۻ�������ľ�����Ȼ����뷴��������ͼ2��ʾ����

[p]

ǿ���ֱ��ƫѹ���³ĵ��еĶ����������ھ�Ե����渽���ۻ�����������������Ե�㣬��˵���ɻ����ڽ��渽������dΪ��Сֵ��ʱ�������ۻ����ﵽ���ֵ����ͼ1��ʾ����C-V�ۻ��������Եõ���һ�������������Ƕ�������ĺ��tox��

��ƫѹ����ʱ�����������Ӵ���������汻�ų���ľ����γɡ���ƫѹ����ʱ�����������Զ��������ﵽ�����룬���ݴﵽ��Сֵ����dΪ���ֵ����������ʱ�ķ��������ݣ�������������������ӵ���������һ����ԭ��ͬ��������MOSFET����ܣ�ֻ�����ǵ������ṹ�Ͳ��Ӹ��Ӹ��ӡ�

��ƫѹɨ�����������Ĺ����л����Եõ�����������������ͼ2��ʾ�����ò�ͬ�Ľ����ź�Ƶ�ʿ��Եõ�����ϸ����Ϣ����Ƶ���Խ�ʾ��ν����̬����������Ƶ��������Ա��ֳ���̬���ܡ�������C-V����ͨ��������Ҫ�ġ�

������������

ͼ3�����˻���C-V�������õĿ�ͼ������C-V����ʵ�������ڽ���Ƶ���½��еģ���˴���������DUT���ĵ��ݿ��Ը������й�ʽ����õ���

CDUT = IDUT / 2πfVac������

IDUT������DUT�Ľ���������ֵ��

f�Dz���Ƶ�ʣ�

Vac�Dz�õĽ�����ѹ�ķ�ֵ����ǡ�

������֮�����ֲ���ͨ�����ؽ�����ѹȻ����������Ľ���������������ѹ������֮����迹��ǣ����ղ��DUT�Ľ����迹��

��Щ�����������������صĴ����벢�����裬�Լ���ɢ���ӣ�©������ͼ4����������������Բ������Ҫ��·������

z, theta���迹�����

R+jX��������翹

Cp-Gp������������絼

Cs-Rs���������������

���У�Z=�迹

D=��ɢ����

θ=���

R=����

X=�翹

G=�絼

[p]

�ɹ�C-V��������ս

C-V�������õĿ�ͼ��Ȼ����ȥ�dz����������ֲ���ȴ����һ������ս��һ����ԣ�������Ա�����漸������������鷳��

• �͵��ݲ�����Ƥ����С��ֵ��

• C-V����������ԲƬ����������

• ©���ݣ���D���IJ���

• ����Ӳ���������ɼ�����

• ������ȡ

�˷���Щ��ս��Ҫ��ϸע�����õļ����Լ����ʵ�Ӳ����������

�͵��ݲ����� ���C��С����ôDUT�Ľ�����Ӧ�����ͽϵͣ����Բ��������ǣ��ڽϸߵ�Ƶ���£�DUT�迹����С���Ӷ����������Ƚ����ײ������뵼�����ͨ���dz��ͣ�����1pF�������ںܶ�LCR���IJ�����Χ����ʹ��Щ�����ܹ�������ЩС����ֵ�IJ����ǿ���Ҳ������˵�����ɬ�Ѷ��������ж����յIJ������ȡ��������ȷ�����������������̵ľ��ȣ���ô�û���Ҫ��˶���ѯ�����̡�

��D��©�����ݡ��뵼����ݳ���Cֵ�ϵ�֮�⣬������й©���ص㡣������ݲ����ĵȼ۵���̫��ʱ�ͻ���������������ᵼ�µ������迹�����������迹��Cֵ����������û�����ھ��г���դ�����������D��ֵ���ܴ���5��һ����ԣ�����D�������ݲ����ľ���Ѹ���½�����˸�D��ʵ��ʹ�õ��ݼƵ�һ���������ء�ͬ�����ϸߵ�Ƶ�������ڽ����һ���⡣�ڽϸߵ�Ƶ���£��������迹�ϵͣ�ʹ�õ��ݵ����ϸߣ��������в�����

C-V�����Ļ�������������Ի����£�DUT����ԲƬ�ϵ�һ�����Խṹ����ͨ��̽������̽�뿨�������Ϳ��ؾ�������C-V�����ǡ���ʹû�п��أ���ȻҲ��ʹ��̽�����ʹ��������ߡ��ڽϸߵ�Ƶ���£�������������У���Ͳ���������ͨ������£�����ͨ�����ʹ�ÿ�·����·����У������ʵ�ֵġ�����Ӳ�������ߺͲ��������dz����ӣ���˾�����C-V����Ӧ�ù���ʦ���н�����һ���õİ취�������ó�ʹ�ø���̽��ϵͳ���˷����ֻ������⡣

��ȡ���õ����ݡ����������ľ������⣬C-V���ݲɼ���ʵ����Ҫ���ǵ����ذ������Ա������������̣�������ȡ�����Ķ���Ժ�Ӳ���������ԡ�һ����ԣ�C-V�����ѽ�����Լ30V��10mAֱ��ƫѹ�����ǣ��ܶ�Ӧ�ã�����LD MOS�ṹ��������������k�в����ʡ�MEMS�������л�TFT��ʾ���������ܣ���Ҫ�ڽϸߵĵ�ѹ������½��в��ԡ�������ЩӦ�ã���Ҫ�����ĸ�ѹֱ����Դ�͵��ݼƣ��ߴ�400V�IJ��ֱ��ƫѹ��0��±400V���ߴ�300mA�ĵ�������Ƿdz����õġ���C-V�����ǵ�HI��LO�˼��ز��ֱ��ƫѹ�ܹ������ؿ���DUT�ڵĵ糡������������������о��ͽ�ģ�Ƿdz����õģ���������Ԫ����

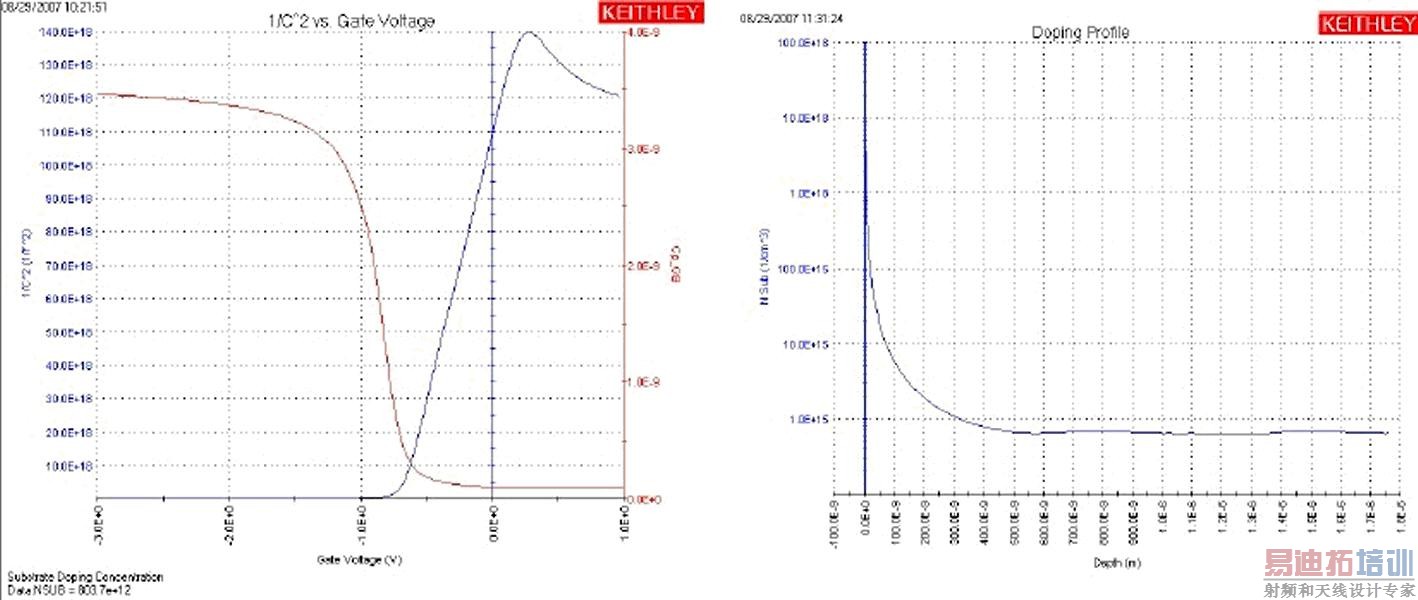

��������Ӧ�ð��������û���̿�ֱ��ʹ�õIJ������̡���ЩӦ�������ڴ�����㷺ʹ�õ��������պͲ��Լ�����������ǰ�������ἰ���й����ݡ���Щ�о��߿��ܻ��һЩ�������IJ��Ը���Ȥ�������MIM������-��Ե��-�������͵��ݽ���C-V��C-fɨ�裬����ԲƬ�ϵĻ���С���ݣ����߶�˫��������������C-Vɨ�衣�����Զ���ͼ�����ܹ������ʵ�ֲ�����ȡ�����磬��ͼ5��ʾ����

ʾ������C-V��

ʾ������C-V��

• ���㼯�������ⲿ����

• ����̽��ĸ߷ֱ��ʺ߾��Ȳ�����ֱ��ƫѹ���������������ݲ��������ɷ�����

• �������úͿ�������

• �ṩ���/������Ϲ��߰����û�ȷ��ϵͳ�Ƿ���������

�����

Lee Stauffer��λ�������������ݿ�������еļ�ʱ��������˾�ĸ��г���������������뵼��������о��г����з���֧�ֲ�Ʒ�������ܹ����ӹ��̺Ͱ뵼����������רҵ������������ڰ뵼�幤�պͲ�Ʒ���̡�����������������������������20��ķḻ���顣������ϵ�绰Ϊ440-248-0400����������Ϊlstauffer@keithley.com��

��Ƶ����ʦ������ѵ�̳���װ���������ٳ�Ϊһ��������Ƶ����ʦ...

������ƹ���ʦ��ѵ�γ���װ������ר���ڿΣ���������Ʋ�����...

��һƪ�����ƴ���LEDɢ�ȵĹؼ�����

��һƪ�������������շ���·���

��Ƶ�����߹���ʦ��ѵ�γ�����>>

��Ƶ����ʦ������ѵ�γ���װ��ר���ڿΣ��������ٳ�Ϊһ���������Ƶ����ʦ��More..��

��Ƶ����ʦ������ѵ�γ���װ��ר���ڿΣ��������ٳ�Ϊһ���������Ƶ����ʦ��More..��

- ������Ƶ����ʦ������ѵ�γ���װ

- �м���Ƶ����ʦ������ѵ�γ���װ

- ����Ƶ����ʦ������ѵ�γ���װ

- SmithԲͼ��ƥ���·�����ѵ�γ�

- ʸ�������������ѵ�̳�

- Agilent ADS ��ѧ��ѵ�γ���װ

- ���߹���ʦ��ѵ�γ���װ

- �ֻ����������ѵ

- 2.4GHz�������������ѵ�̳�

- 13.56MHz NFC���ߺ�RFID���������ѵ

- WiFi���ߺ���Ƶ��·�����ѵ�γ�

- HFSS��ѧ��ѵ�γ���װ

- HFSS���������ѵ�γ���װ

- CST�������ҽ�ѧ��ѵ�γ���װ

- CST���������ѵ��Ƶ�γ���װ