- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

可配置电源管理ASIC--当今的系统黏合剂

录入:edatop.com 点击:

数字ASIC--上个世纪的黏合逻辑

上个世纪,在数字化思维主导设计领域时,系统是标准处理器,ASSP,模拟电路和"黏合逻辑"的混合物。"黏合逻辑"是通过小型和中型集成电路把不同数字芯片的协议和总线连在一起。为了降低成本实现一体化,"黏合逻辑"曾经风靡整个ASIC业。

如今,整个数字系统发展到深亚微米(DSM)半导体阶段,"黏合逻辑"也慢慢退出了系统设计应用。但是"黏合逻辑"真的过时了吗?答案因人而异。现在,对于数字"黏合逻辑"的需求不如以前那么强烈,但是模拟"黏合功能"却在增长。

复合信号ASIC—今天的"系统胶连"

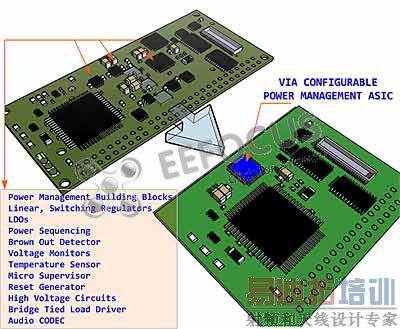

现在的系统有许多模拟功能,但是却并不适合90和65纳米硅芯片应用。这些系统需要多个电源层,若干电压等级,电源的排序,睡眠模式功耗,高电压LED驱动器,高质量音频处理器以及这些功能的智能控制。系统级芯片数字化解决方案的增长导致我们需要复合信号集成电路,囊括了诸多为了节约成本,提高性能和集成的模拟功能。如图1所示:

上个世纪,在数字化思维主导设计领域时,系统是标准处理器,ASSP,模拟电路和"黏合逻辑"的混合物。"黏合逻辑"是通过小型和中型集成电路把不同数字芯片的协议和总线连在一起。为了降低成本实现一体化,"黏合逻辑"曾经风靡整个ASIC业。

如今,整个数字系统发展到深亚微米(DSM)半导体阶段,"黏合逻辑"也慢慢退出了系统设计应用。但是"黏合逻辑"真的过时了吗?答案因人而异。现在,对于数字"黏合逻辑"的需求不如以前那么强烈,但是模拟"黏合功能"却在增长。

复合信号ASIC—今天的"系统胶连"

现在的系统有许多模拟功能,但是却并不适合90和65纳米硅芯片应用。这些系统需要多个电源层,若干电压等级,电源的排序,睡眠模式功耗,高电压LED驱动器,高质量音频处理器以及这些功能的智能控制。系统级芯片数字化解决方案的增长导致我们需要复合信号集成电路,囊括了诸多为了节约成本,提高性能和集成的模拟功能。如图1所示:

|

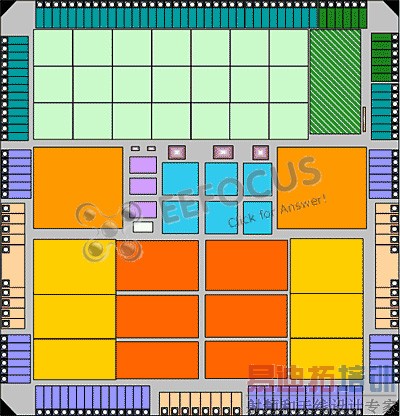

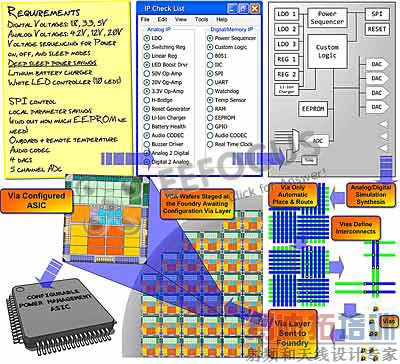

图1 : 分离的电源管理功能组合在一个可配置的集成电路上 便携式电子设备可能包括广泛的电源电压:用于数字集成电路的1.8V和3.3V电压,用于锂离子电池的4.2V电压,用于传统接口的5V电压,用于LED背光的36V电压,单独的用于敏感模拟电路的电压以及用于电机控制的高电压。根据每个功率源的要求,设计师们选择不同的电源转换拓扑结构,其中包括线性,开关以及低压降稳压器。 不仅是调节器的纯粹数量在增加,这些系统往往有复杂的电源排序要求,每个供应源相互之间在电源开关,睡眠和降低的操作模式时的开启和关闭需要精确的控制。通常这些供应源不仅仅是简单的打开,而需要电源电压的斜升或斜降行为,从而增加了电源管理系统的额外的复杂性。在设备的电源管理设计中,随着调压器相互之间的正确排序,系统复位信号,振荡器开启和PLL稳定时间必须考虑进去。 一个电源管理系统集成了多种电源转换拓扑结构,数字排序逻辑,控制电源管理功能的数字通讯,模拟电压以及电流测量;不变性记忆器用来存储电压设置点,排列顺序,序列周期和工厂校准数据。这些电源管理资源消耗了了许多电路板空间,需要多位包装,并加入到组装成本中,使其成为电源管理集成电路的理想候选。这些专用集成电路建立在混合信号处理的基础上,因此相关功能不能与电源管理正常联系,比如音频处理,蜂鸣器驱动器和马达控制,在设备中成为内含物的选择器件。对于PMIC ASIC来说,负责集成和控制许多IP模块很平常。功能如表1: 表1 PMIC 电源管理集成电路功能 线性调节器 电机控制 转换器 音频扬声器驱动 低压降稳压器 自定义数字逻辑 发光二极管升压稳压器 电源排序 电池管理-充电,监视 复位发生器 LED驱动 电压监视器 LCD电压发生器 电流监视器 电压转换器 风扇控制 音频处理 温度传感器 非易失性存储器 欠压检测器 可配置电源管理集成电路 所有的模拟和电源管理"胶连"的进入让一个单一设备实现了整合,提高了侧寻性能,降低了整个系统的成本。然而,全定制的电源管理IC开发一向昂贵,进入市场缓慢,并且有很大的风险。 可配置阵列技术(VCA)的发展产生了硅验证的电源管理ASIC的解决方案,通过一个单一的遮罩层的变化来配置和定制特定的应用。一个VCA在ASIC模块上集成了硅验证模拟化,数字化和内存资源。然后这些资源由整体的路由结构所覆盖。包含这些VCA的晶片经过特殊处理和铸造,所有的模拟和数字资源可相互联系并由一个遮罩层来配置。由于只有一个遮罩层铸造加工,制造成本大大降低,制造时间从几个月到几周,硅验证的IP和互联路的使用大大降低了风险。

|