- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

自制 CMOS 集成电路测试仪

录入:edatop.com 点击:

电子技术的电控电路常采用 CMOS 逻辑控制系统,通过多年的维修实践,我们自行设计和安装了简易集成逻辑门电路测试仪。只要掌握了各种逻辑门电路输入和输出的逻辑关系,通过该测试仪即可很快判断集成电路的好坏。

一、测试仪电路构成及原理

1 .电路构成该测试仪电路由 +12V 直流电源、 16 只小型豆型开关、 15 只发光二极管、 15 只普通碳膜电阻 (1k Ω O . 25W) 和一个 16 脚的集成电路管座等组成。为了便于测试判断和分析,对于 14 脚集成电路,开关 K1 和发光二极管 D1 对应控制集成块的①脚,开关 K2 和发光二极管 D2 对应控制集成块的②脚,依次类推,直到开关 K13 和发光二极管 D13 对应控制集成块的⑩脚,一般⑦脚接地.由 K7 控制选择, K14 必须合上控制⑩脚接 +12V 电源,对于测试 14 脚的集成电路管脚号见图中内部标识.一定要与集成块管脚对号插入。对于 16 脚集成电路,开关 K1 和发光二极管 D1 对应控制集成块的①脚,开关 K2 和发光二极管 D2 对应控制集成块的②脚,依次类推到第⑦脚 ( 开关 K7 置于 +12V 电源位置 ) ,⑥脚接地,从开关 K 9 ' 、 K 10 ' 、 K 11 ' 、 K 12 ' 、 K 13 ' 、 K 14 ' 、 K 15 ' 、 K14 分别控制⑨脚到⑩脚的输入和控制发光二极管 D9 、 D 10 ' 一直到 D 16 ' 的指示,根据各种集成块选择接 +12V 电源。

2 .基本测试原理集成逻辑门电路各个管脚输入电平高或低可以由开关 K 来选择,当输入为高电平时,将对应的开关合上;输入电平为低时对应的开关断开,当各组对应的逻辑输出电平为高电平时.对应的发光二极管点亮:输出电平为低时,发光二极管不发光。通过不同输入电平作用使输出电平变化和实际逻辑运算电平关系相对比,可以判定和分析其好坏。制作本测试器,有两点要引起注意: (1) 必须考虑集成电路的管脚第⑦脚与第⑧脚的接地转换。 (2) 集成电路的最后脚⑩脚不一定接电源正端,需要增加开关 K14 隔离。如: CD1413 的 16 脚就不接电源正端。

二、测试举例将各型号的集成电路制作成卡片

根据卡片的对应脚接通相应的开关 K ,合上电源开关 K0 。

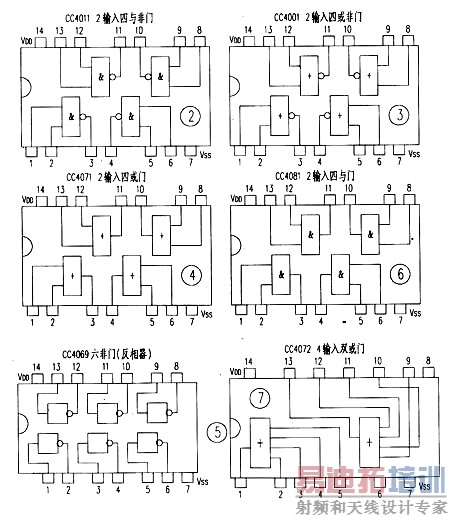

1 .测 CC4011 时.卡片如图 2 测量时先将 K14 合上 ( 加电源 ) , K7 置在接地位置。此被测集成电路为 2 输入四与非门,将 K1 、 K2 开关接通,③脚输出低电平。

D3 不亮, D1 、 D2 亮。如果 Kl 、 K2 断开,则对应的输出端③脚输出高电平, D3 亮, D1 ,。 D2 不亮。只接通 K1 、 K2 一个时, D1 、 D2 有一个亮,③脚也输出低电平,发光二极管 D3 也不亮。其他门测量也如此.不再叙述。 。

2 .测 CC 4001 .卡片如图 3 测量时先将 K14 合上加电源, K7 置接地位置。当 K12 、 K13 都未接通时,对应的输出端⑩脚输出高电平, D11 亮,只要 K12 、 K13 一个合上,则 11 脚输出低电平, D11 不亮, K12 、 K13 都合上,则 11 脚输出低电平, D11 不亮。其他门测量也如此。

3 .测量 CC4071 卡片如图 4 测量时先将 K14 合上 ( 加电源 ) . K7 置接地位置。当 K12 、 K13 都未接通时,对应的输出端 11 脚输出低电平, D11 不亮,只要 K12 、 K13 合上一个, D13 , D12 有一个对应发光二极管亮,则 11 脚输出高电平, D11 亮, K12 、 K13 都合上. D13 、 D12 都亮,则⑩脚输出高电平, D 1l 亮。其他门测量也如此。

4 .测量 CC4069 卡片如图 5 测量时先将 K14 合上 ( 加电源 ) , K7 置接地位置。当合上 K1 时. Dl 发光二极管亮,②脚输出低电平, D2 不亮。当断开 K1 时,②脚输出高电平, D2 亮。其他门测量也如此。

5 .测 CC4081 .卡片如图 6 此集成电路为 2 输入四与门。

测量时先将 K14 合上加电源. K7 置接地位置。将 K1 、 K2 开关接通, Dl 、 D2 发光二管亮,输出端③脚输出高电平,发光二极管 D3 亮。

如果 Kl 、 K2 断开,则③脚输出低电平, D1 不亮,只接通 Kl 、 K2 一个时, Dl 、 D2 有一个发光二极管亮,⑧脚也输出低电平, Dl 也不亮。其他门测量也如此。

6 .测 CC4072 .卡片如图 7 .此集成电路为 4 输入双或门。

测量时先将 K14 合上 ( 加电源 ) . K7 置接地位置。只要输入端②、③、④、‘⑤有一脚是高电平 (K2 、 K3 、 K4 、 K5 脚有一个接通或全接通, D2 、 D3 、 D4 、 D5 有一个发光二极管亮或全亮 ) ,①脚输出高电平。

发光二极管 Dl 亮, K2 、 K3 、 K4 、 K5 全断开,①脚输出低电平. Dl 不亮。注:另一个或 I-] 测试也如此。

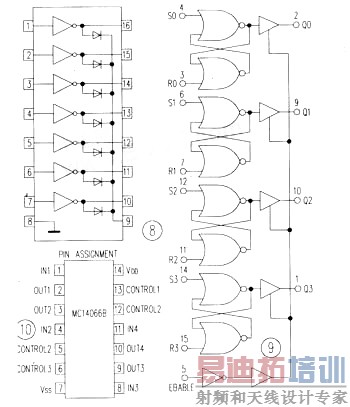

7 .测 CDl413 ,卡片如图 8CDl413 为 16 脚集成电路,测量时先将 K 9 ' 合上给集成块供电 (D9 亮 ) , Kl 置于 +12V 电源位置 (Dl 亮 ) ,说明此路非门工作正常.用此方法可以依次测量其他 6 路非门是否正常。 NEC 公司生产的斗 PC2002 系列同 CDl413 功能作用和管脚排列完全一样。

8 .测/ VICl4043 卡片如图 9MCl4043 为 16 脚集成电路 ( 其第⑧脚直接接地 ) ,将 K7 由接地转换为接高电平。将 E ⑤接高电平 (D5 亮 ) ,④脚输入低电平 (K4 断开 ) ,③脚输入高电平 (K3 接通, D3 亮 ) ,则②脚输出低电平, D2 不亮,④脚输入高电平 (K4 接通, D4 亮 ) ,③脚输入低电平 (K3 断开 ) ,则②脚输出高电平, D2 亮,④脚输入高电平 (K4 接通, D4 亮 ) ,③脚输入高电平 (K3 接通, D3 亮 ) ,则②脚输出高电平, D2 亮,其他门测量也如此。 9 .测量 MC14066 ,卡片如图 10 测量时先将 K14 合上 ( 加电源 ) , K7 置接地位置。

将控制端⑤接高电平 (K5 接通 ) , D5 发光二极管亮,④脚接高电平 (K4 接通 ) , D4 亮,则③脚输出高电平 (D3 亮 ) 。

K4 不接通, D4 不亮, D3 也不亮。将 K3 接通 (D3 亮 ) , K4 断开, D4 亮。③、④脚互为输入、输出端。控制端 K5 断开, D5 不亮,③、④脚不论哪一端加高电平,另一端都是低电平。

三、小结

本测试仪可测 MC 、 CD 、 CC 、 HEF 等系列集成电路。还有许多集成电路也可以在此测试仪上测试.如: CD4541 、 CD40175 、 CD4023 、 CD4025 、 CD4002 、 CD4012 、 CI)4073 、 CD4082 、 CD4013 、 4N25 、 2G03D 等等。 ( 注: CC 、 CD 、 MC 、 HEF 等系列通用,可直接代换 ) 。

一、测试仪电路构成及原理

1 .电路构成该测试仪电路由 +12V 直流电源、 16 只小型豆型开关、 15 只发光二极管、 15 只普通碳膜电阻 (1k Ω O . 25W) 和一个 16 脚的集成电路管座等组成。为了便于测试判断和分析,对于 14 脚集成电路,开关 K1 和发光二极管 D1 对应控制集成块的①脚,开关 K2 和发光二极管 D2 对应控制集成块的②脚,依次类推,直到开关 K13 和发光二极管 D13 对应控制集成块的⑩脚,一般⑦脚接地.由 K7 控制选择, K14 必须合上控制⑩脚接 +12V 电源,对于测试 14 脚的集成电路管脚号见图中内部标识.一定要与集成块管脚对号插入。对于 16 脚集成电路,开关 K1 和发光二极管 D1 对应控制集成块的①脚,开关 K2 和发光二极管 D2 对应控制集成块的②脚,依次类推到第⑦脚 ( 开关 K7 置于 +12V 电源位置 ) ,⑥脚接地,从开关 K 9 ' 、 K 10 ' 、 K 11 ' 、 K 12 ' 、 K 13 ' 、 K 14 ' 、 K 15 ' 、 K14 分别控制⑨脚到⑩脚的输入和控制发光二极管 D9 、 D 10 ' 一直到 D 16 ' 的指示,根据各种集成块选择接 +12V 电源。

2 .基本测试原理集成逻辑门电路各个管脚输入电平高或低可以由开关 K 来选择,当输入为高电平时,将对应的开关合上;输入电平为低时对应的开关断开,当各组对应的逻辑输出电平为高电平时.对应的发光二极管点亮:输出电平为低时,发光二极管不发光。通过不同输入电平作用使输出电平变化和实际逻辑运算电平关系相对比,可以判定和分析其好坏。制作本测试器,有两点要引起注意: (1) 必须考虑集成电路的管脚第⑦脚与第⑧脚的接地转换。 (2) 集成电路的最后脚⑩脚不一定接电源正端,需要增加开关 K14 隔离。如: CD1413 的 16 脚就不接电源正端。

二、测试举例将各型号的集成电路制作成卡片

根据卡片的对应脚接通相应的开关 K ,合上电源开关 K0 。

1 .测 CC4011 时.卡片如图 2 测量时先将 K14 合上 ( 加电源 ) , K7 置在接地位置。此被测集成电路为 2 输入四与非门,将 K1 、 K2 开关接通,③脚输出低电平。

D3 不亮, D1 、 D2 亮。如果 Kl 、 K2 断开,则对应的输出端③脚输出高电平, D3 亮, D1 ,。 D2 不亮。只接通 K1 、 K2 一个时, D1 、 D2 有一个亮,③脚也输出低电平,发光二极管 D3 也不亮。其他门测量也如此.不再叙述。 。

2 .测 CC 4001 .卡片如图 3 测量时先将 K14 合上加电源, K7 置接地位置。当 K12 、 K13 都未接通时,对应的输出端⑩脚输出高电平, D11 亮,只要 K12 、 K13 一个合上,则 11 脚输出低电平, D11 不亮, K12 、 K13 都合上,则 11 脚输出低电平, D11 不亮。其他门测量也如此。

3 .测量 CC4071 卡片如图 4 测量时先将 K14 合上 ( 加电源 ) . K7 置接地位置。当 K12 、 K13 都未接通时,对应的输出端 11 脚输出低电平, D11 不亮,只要 K12 、 K13 合上一个, D13 , D12 有一个对应发光二极管亮,则 11 脚输出高电平, D11 亮, K12 、 K13 都合上. D13 、 D12 都亮,则⑩脚输出高电平, D 1l 亮。其他门测量也如此。

4 .测量 CC4069 卡片如图 5 测量时先将 K14 合上 ( 加电源 ) , K7 置接地位置。当合上 K1 时. Dl 发光二极管亮,②脚输出低电平, D2 不亮。当断开 K1 时,②脚输出高电平, D2 亮。其他门测量也如此。

5 .测 CC4081 .卡片如图 6 此集成电路为 2 输入四与门。

测量时先将 K14 合上加电源. K7 置接地位置。将 K1 、 K2 开关接通, Dl 、 D2 发光二管亮,输出端③脚输出高电平,发光二极管 D3 亮。

如果 Kl 、 K2 断开,则③脚输出低电平, D1 不亮,只接通 Kl 、 K2 一个时, Dl 、 D2 有一个发光二极管亮,⑧脚也输出低电平, Dl 也不亮。其他门测量也如此。

6 .测 CC4072 .卡片如图 7 .此集成电路为 4 输入双或门。

测量时先将 K14 合上 ( 加电源 ) . K7 置接地位置。只要输入端②、③、④、‘⑤有一脚是高电平 (K2 、 K3 、 K4 、 K5 脚有一个接通或全接通, D2 、 D3 、 D4 、 D5 有一个发光二极管亮或全亮 ) ,①脚输出高电平。

发光二极管 Dl 亮, K2 、 K3 、 K4 、 K5 全断开,①脚输出低电平. Dl 不亮。注:另一个或 I-] 测试也如此。

7 .测 CDl413 ,卡片如图 8CDl413 为 16 脚集成电路,测量时先将 K 9 ' 合上给集成块供电 (D9 亮 ) , Kl 置于 +12V 电源位置 (Dl 亮 ) ,说明此路非门工作正常.用此方法可以依次测量其他 6 路非门是否正常。 NEC 公司生产的斗 PC2002 系列同 CDl413 功能作用和管脚排列完全一样。

8 .测/ VICl4043 卡片如图 9MCl4043 为 16 脚集成电路 ( 其第⑧脚直接接地 ) ,将 K7 由接地转换为接高电平。将 E ⑤接高电平 (D5 亮 ) ,④脚输入低电平 (K4 断开 ) ,③脚输入高电平 (K3 接通, D3 亮 ) ,则②脚输出低电平, D2 不亮,④脚输入高电平 (K4 接通, D4 亮 ) ,③脚输入低电平 (K3 断开 ) ,则②脚输出高电平, D2 亮,④脚输入高电平 (K4 接通, D4 亮 ) ,③脚输入高电平 (K3 接通, D3 亮 ) ,则②脚输出高电平, D2 亮,其他门测量也如此。 9 .测量 MC14066 ,卡片如图 10 测量时先将 K14 合上 ( 加电源 ) , K7 置接地位置。

将控制端⑤接高电平 (K5 接通 ) , D5 发光二极管亮,④脚接高电平 (K4 接通 ) , D4 亮,则③脚输出高电平 (D3 亮 ) 。

K4 不接通, D4 不亮, D3 也不亮。将 K3 接通 (D3 亮 ) , K4 断开, D4 亮。③、④脚互为输入、输出端。控制端 K5 断开, D5 不亮,③、④脚不论哪一端加高电平,另一端都是低电平。

三、小结

本测试仪可测 MC 、 CD 、 CC 、 HEF 等系列集成电路。还有许多集成电路也可以在此测试仪上测试.如: CD4541 、 CD40175 、 CD4023 、 CD4025 、 CD4002 、 CD4012 、 CI)4073 、 CD4082 、 CD4013 、 4N25 、 2G03D 等等。 ( 注: CC 、 CD 、 MC 、 HEF 等系列通用,可直接代换 ) 。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:集成电路知识平台与山寨现象

下一篇:基于Simulink技术的噪声调幅干扰仿真

射频和天线工程师培训课程详情>>