- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于AD9852的基准源设计

录入:edatop.com 点击:

0 引 言

直接数字频率合成(DD6)是一种以固定的精确时钟源为基准,利用数字处理模块产生频率和相位均可调的输出信号的技术。随着超大规模集成电路和微电子技术的发展,现代高性能、高集成度和小体积的DDS产品正快速取代传统的模拟信号频率合成技术,成为了这类问题新的解决方案。本文利用FPGA计算出相应的频率控制字,并对DDS芯片AD9852进行编程,最终得到所要求的输出波形。

1 系统总体方案设计

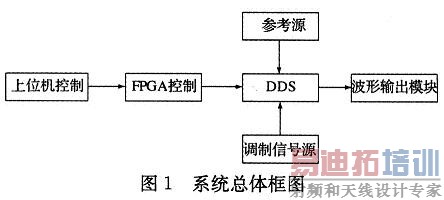

基准源主要由上位机控制、FPGA控制、DDS、参考源、调制信号源及波形输出模块组成,如图1所示。上位机控制单元是由计算机通过USB总线连接至电路板进行控制操作。FPGA控制单元实现与上位机控制单元交互信息,同时以并行方式向DDS芯片发送控制字,以管理其内部寄存器。参考源为DDS提供高精准的时钟晶振,确保DDS输出信号的频谱纯度。调制信号单元为DDS提供外部调制信息。波形输出模块由低通滤波器、运算放大器及电阻网络组成,主要完成DDS输出信号的滤波,放大等功能。

系统上电复位后,电路板上的绿色LED二极管闪烁提示整机处于正常状态。当有DDS波形输出时,电路板上的蓝色LED二极管闪烁提示工作正常。

2 系统模块设计

2.1 系统软件设计

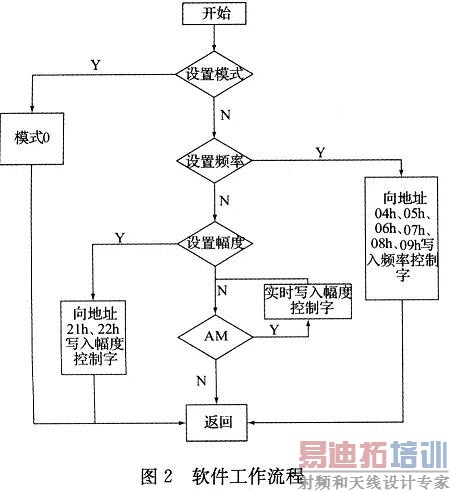

基准源的上位机控制采用C语言编程实现,主要完成对FPGA内部寄存器的读写操作,进而控制板上各种硬件资源的管理。另外,DDS的频率控制字的计算也由上位机软件计算得到。FPGA接收到上位机的命令,经解析后向DDS的内部寄存器写入控制字,完成相应功能。同时,FPGA负责电路板上的各种时钟管理。系统软件的总体工作流程如图2所示。

2.2 频率控制设计

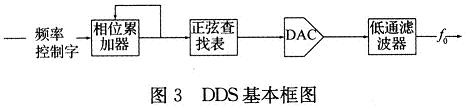

本文采用DDS技术产生频率可调的波形,具有频率分辨率高,相位连续等优点。DDS基本框图如图3所示。

DDS的基本结构包括:相位累加器,正弦查找表ROM,数模转换器DAC等。DDS有两个主要缺点:一是输出频率低,二是输出频谱中杂散多。输出频率低主要受DDS工作频率的限制,随着微电子技术的发展,这个缺陷会逐渐得到弥补。DDS输出频谱中的杂散是DDS所固有的,这是由DDS的工作方式决定的。

DDS的基本工作原理是:相位累加器在N位频率控制字FTW的控制下,以参考时钟频率fc为采样率,产生待合成信号的数字线性相位序列,将其高M位作为地址码通过正弦查询表ROM变换,产生L位对应信号波形的数字序列S(n),再由数模转换器将其转换为阶梯模拟电压波形S(t),最后由具有内插作用的低通滤波器LPF将其平滑为连续的正弦波形作为输出。FTW和fc时钟频率共同决定了DDS输出信号的频率fo,它们之间关系满足:

[p]

由上可知,DDS技术可以理解为数字信号处理中信号综合的硬件实现问题,即给定信号幅度、频率、相位参数,产生所需要的信号波形。从系统的角度可以认为是给定输入时钟fc和频率控制字FTW,输出某一对应的正弦信号。另外,也可以认为DDS是一个可变的程序小数分频器。

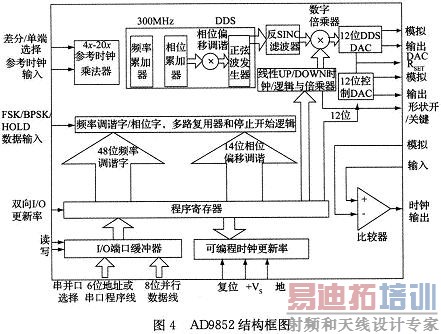

本文中的DDS芯片采用的是Analog Device公司生产的AD9852芯片,时钟频率最高可以达到300MHz,内部集成了12位DAC,相位累加器的位数为48位,并且具有FSK,PSK等数字调制功能。AD9852是具有高集成度的DDS芯片,内部结合有高速性能的DAC和一个比较器,构成了一个数字可编程的合成器。当给定一个精确的参考时钟源时,AD9852就会产生一个高稳定度,频率、相位及幅度均可编程的正弦波输出。AD9852的频率控制字达到48位,使其频率分辨率可达1μHz。其相位截断到17位,使得AD9852具有极好的自由杂散动态范围SFDR。AD9852还提供14位的数字控制的相位调制。其结构框图如图4所示。

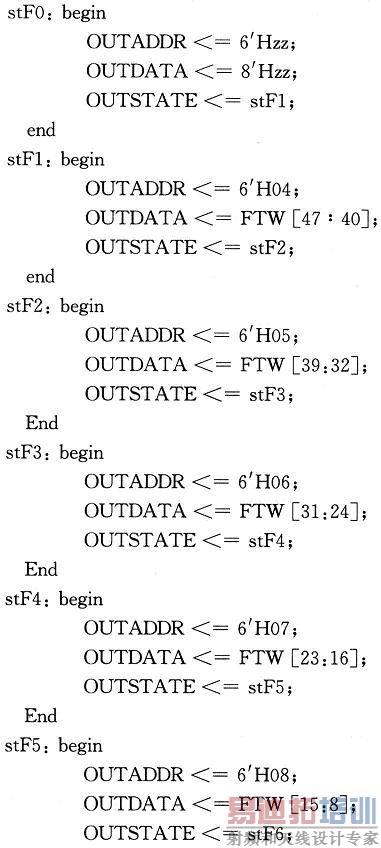

整机上电复位后,为设置某一频率值,需要将频率控制字从高位至低位依次以并行方式写入AD9852的地址04h至地址09h,VreilogHDL程序代码如下:

2.3 幅度控制设计

AD9852内嵌电流输出型DAC,改变其输出幅值有两种方法:1)AD9852的输出最大幅值由连接至56引脚的电阻Rset决定,最大满摆幅输出电流为20mA,电阻Rset与输出电流Iout的关系为:Iout=39.9/Rset;2)AD9852的地址21h、22h为幅度控制寄存器,更改其控制字即可改变输出信号幅值。

整机上电复位后,为设置某一幅值,需要将幅度控制字从高位至低位依次以并行方式写入AD9852的地址21h、22h,VreilogHDL程序代码如下:

2.4 AM设计

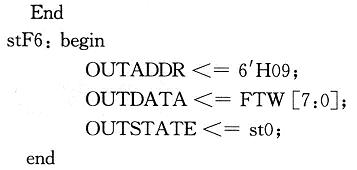

基于2.3讨论的幅度控制设计,加入外调制信号可进一步实现AM调制,其中,外部调制信号的产生框图如图5所示:

图5中,RAM存储外调制信号波形,本文中需要存储正弦波波形,由RAM和FPGA共同构建NCO。存储的数值由上位机计算得出,并通过FPGA写入RAM中。RAM中的数据被FPGA读出后,由数字乘法器对其进行放大,乘系数因子由AM的调幅深度决定。向AD9852的地址21h、22h(幅度控制寄存器)写入外部调制信号所对应的波形数据,即可实现调制速率、调制深度均可控的AM调制。

2.5 波形输出设计

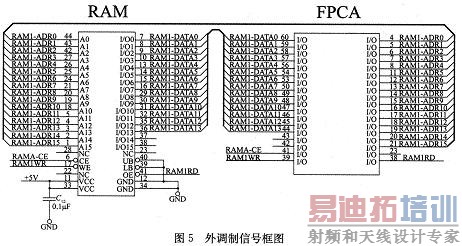

AD9852所产生的信号直接由器件内部的余弦DAC输出,内部不含低通滤波器,故要对其输出信号进行滤波处理。本文中,为了降低AD9852内部系统时钟的干扰,采用了具有下降速度更快、且较窄过渡带特性的7阶椭圆滤波器。如图6所示。

AD9852输出信号的幅度范围较小,需要根据实际应用情况进行放大处理,本文采用运算放大器LM7171搭建负反馈放大电路。

3 结束语

本文介绍了基准源的设计方法,采用DDS技术,具有频率分辨率高、相位连续、低相噪低杂散等优点。基准源的频率、幅度均可控。同时,论述了AM的实现方法,相对于传统模拟方式的设计方法,更加轻便、小巧,且线性度良好,便于校准和批生产。该DDS已使用于便携式信号源中,经实测整机系统运行稳定,在总参某项目中得到实际应用,达到了预期的目标,具有推广价值。

发布者:博子

直接数字频率合成(DD6)是一种以固定的精确时钟源为基准,利用数字处理模块产生频率和相位均可调的输出信号的技术。随着超大规模集成电路和微电子技术的发展,现代高性能、高集成度和小体积的DDS产品正快速取代传统的模拟信号频率合成技术,成为了这类问题新的解决方案。本文利用FPGA计算出相应的频率控制字,并对DDS芯片AD9852进行编程,最终得到所要求的输出波形。

1 系统总体方案设计

基准源主要由上位机控制、FPGA控制、DDS、参考源、调制信号源及波形输出模块组成,如图1所示。上位机控制单元是由计算机通过USB总线连接至电路板进行控制操作。FPGA控制单元实现与上位机控制单元交互信息,同时以并行方式向DDS芯片发送控制字,以管理其内部寄存器。参考源为DDS提供高精准的时钟晶振,确保DDS输出信号的频谱纯度。调制信号单元为DDS提供外部调制信息。波形输出模块由低通滤波器、运算放大器及电阻网络组成,主要完成DDS输出信号的滤波,放大等功能。

|

系统上电复位后,电路板上的绿色LED二极管闪烁提示整机处于正常状态。当有DDS波形输出时,电路板上的蓝色LED二极管闪烁提示工作正常。

2 系统模块设计

2.1 系统软件设计

基准源的上位机控制采用C语言编程实现,主要完成对FPGA内部寄存器的读写操作,进而控制板上各种硬件资源的管理。另外,DDS的频率控制字的计算也由上位机软件计算得到。FPGA接收到上位机的命令,经解析后向DDS的内部寄存器写入控制字,完成相应功能。同时,FPGA负责电路板上的各种时钟管理。系统软件的总体工作流程如图2所示。

|

2.2 频率控制设计

本文采用DDS技术产生频率可调的波形,具有频率分辨率高,相位连续等优点。DDS基本框图如图3所示。

|

DDS的基本结构包括:相位累加器,正弦查找表ROM,数模转换器DAC等。DDS有两个主要缺点:一是输出频率低,二是输出频谱中杂散多。输出频率低主要受DDS工作频率的限制,随着微电子技术的发展,这个缺陷会逐渐得到弥补。DDS输出频谱中的杂散是DDS所固有的,这是由DDS的工作方式决定的。

DDS的基本工作原理是:相位累加器在N位频率控制字FTW的控制下,以参考时钟频率fc为采样率,产生待合成信号的数字线性相位序列,将其高M位作为地址码通过正弦查询表ROM变换,产生L位对应信号波形的数字序列S(n),再由数模转换器将其转换为阶梯模拟电压波形S(t),最后由具有内插作用的低通滤波器LPF将其平滑为连续的正弦波形作为输出。FTW和fc时钟频率共同决定了DDS输出信号的频率fo,它们之间关系满足:

|

由上可知,DDS技术可以理解为数字信号处理中信号综合的硬件实现问题,即给定信号幅度、频率、相位参数,产生所需要的信号波形。从系统的角度可以认为是给定输入时钟fc和频率控制字FTW,输出某一对应的正弦信号。另外,也可以认为DDS是一个可变的程序小数分频器。

本文中的DDS芯片采用的是Analog Device公司生产的AD9852芯片,时钟频率最高可以达到300MHz,内部集成了12位DAC,相位累加器的位数为48位,并且具有FSK,PSK等数字调制功能。AD9852是具有高集成度的DDS芯片,内部结合有高速性能的DAC和一个比较器,构成了一个数字可编程的合成器。当给定一个精确的参考时钟源时,AD9852就会产生一个高稳定度,频率、相位及幅度均可编程的正弦波输出。AD9852的频率控制字达到48位,使其频率分辨率可达1μHz。其相位截断到17位,使得AD9852具有极好的自由杂散动态范围SFDR。AD9852还提供14位的数字控制的相位调制。其结构框图如图4所示。

|

整机上电复位后,为设置某一频率值,需要将频率控制字从高位至低位依次以并行方式写入AD9852的地址04h至地址09h,VreilogHDL程序代码如下:

|

AD9852内嵌电流输出型DAC,改变其输出幅值有两种方法:1)AD9852的输出最大幅值由连接至56引脚的电阻Rset决定,最大满摆幅输出电流为20mA,电阻Rset与输出电流Iout的关系为:Iout=39.9/Rset;2)AD9852的地址21h、22h为幅度控制寄存器,更改其控制字即可改变输出信号幅值。

整机上电复位后,为设置某一幅值,需要将幅度控制字从高位至低位依次以并行方式写入AD9852的地址21h、22h,VreilogHDL程序代码如下:

|

2.4 AM设计

基于2.3讨论的幅度控制设计,加入外调制信号可进一步实现AM调制,其中,外部调制信号的产生框图如图5所示:

|

图5中,RAM存储外调制信号波形,本文中需要存储正弦波波形,由RAM和FPGA共同构建NCO。存储的数值由上位机计算得出,并通过FPGA写入RAM中。RAM中的数据被FPGA读出后,由数字乘法器对其进行放大,乘系数因子由AM的调幅深度决定。向AD9852的地址21h、22h(幅度控制寄存器)写入外部调制信号所对应的波形数据,即可实现调制速率、调制深度均可控的AM调制。

2.5 波形输出设计

AD9852所产生的信号直接由器件内部的余弦DAC输出,内部不含低通滤波器,故要对其输出信号进行滤波处理。本文中,为了降低AD9852内部系统时钟的干扰,采用了具有下降速度更快、且较窄过渡带特性的7阶椭圆滤波器。如图6所示。

|

AD9852输出信号的幅度范围较小,需要根据实际应用情况进行放大处理,本文采用运算放大器LM7171搭建负反馈放大电路。

3 结束语

本文介绍了基准源的设计方法,采用DDS技术,具有频率分辨率高、相位连续、低相噪低杂散等优点。基准源的频率、幅度均可控。同时,论述了AM的实现方法,相对于传统模拟方式的设计方法,更加轻便、小巧,且线性度良好,便于校准和批生产。该DDS已使用于便携式信号源中,经实测整机系统运行稳定,在总参某项目中得到实际应用,达到了预期的目标,具有推广价值。

发布者:博子

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>