- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

NexFETTM:新一代功率MOSFET

录入:edatop.com 点击:

对于理想开关的需求

功率 MOSFET 可作为高频率脉冲宽度调变 (PWM) 应用中的电气开关,例如稳压器及/或控制电源应用之中负载电流的开关。作为负载开关使用时,由于切换时间通常较长,因此装置的成本、尺寸及导通电阻 (on-resistance) 是设计时考虑的重点。用于 PWM 应用时,晶体管必须在切换期间达到最低的功率损耗,对于促使 MOSFET 设计更为挑战且时间成本更高的小型内部电容而言,这已成为另一项必要的需求。设计人员需要特别注意闸极对汲极 (Cgd) 电容,因为这类电容决定了切换期间的电压瞬时时间,这是影响切换功率损耗最重要的参数。

同步降压转换器的"理想"开关,即计算机应用中最常用的转换器拓朴,必须具备下列需求:

低传导损耗 (低 Rds,on)

低切换损耗 (低 Cgd)

低驱动器损耗 (低 Ciss)

无横流 (cross-current) 损耗 (低 Cgd/Ciss 比率,避免击穿 (shoot-through) 效应)

低体二极管 (body diode) 损耗 (低 Qrr 及硬式切换,缩短先断后合(break-before-make) 的延迟时间)

当然,作为开关用的装置必须具备稳定的结构,才能消耗大量的累增崩溃电量 (avalanche energy),以确保整个安全操作范围 (SOA)的运作都正常可靠。

装置概念及技术

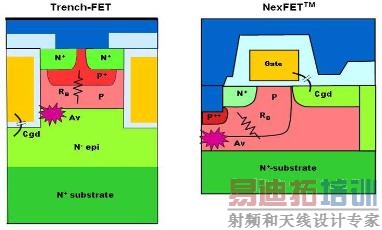

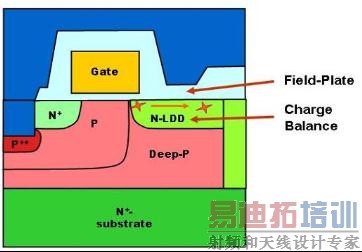

NexFETTM 技术是电源应用的新一代 MOSFET,其中采用能够成功放大无线射频 (RF) 信号的横向扩散金属氧化物半导体 (LDMOS) 装置;见图 1剖面示意图。电流会从最上层金属化源极端流经平面闸极下方的侧边通道,并流至轻掺杂汲极 (LDD) 延伸区域,然后借由低阻抗的垂直沉片 (vertical sinker) 转向基板。无线射频可提供最低的内部电容,而垂直电流可提供高电流密度,完全没有 LDMOS 晶体管平面配置常出现的解偏压问题。

功率 MOSFET 可作为高频率脉冲宽度调变 (PWM) 应用中的电气开关,例如稳压器及/或控制电源应用之中负载电流的开关。作为负载开关使用时,由于切换时间通常较长,因此装置的成本、尺寸及导通电阻 (on-resistance) 是设计时考虑的重点。用于 PWM 应用时,晶体管必须在切换期间达到最低的功率损耗,对于促使 MOSFET 设计更为挑战且时间成本更高的小型内部电容而言,这已成为另一项必要的需求。设计人员需要特别注意闸极对汲极 (Cgd) 电容,因为这类电容决定了切换期间的电压瞬时时间,这是影响切换功率损耗最重要的参数。

同步降压转换器的"理想"开关,即计算机应用中最常用的转换器拓朴,必须具备下列需求:

低传导损耗 (低 Rds,on)

低切换损耗 (低 Cgd)

低驱动器损耗 (低 Ciss)

无横流 (cross-current) 损耗 (低 Cgd/Ciss 比率,避免击穿 (shoot-through) 效应)

低体二极管 (body diode) 损耗 (低 Qrr 及硬式切换,缩短先断后合(break-before-make) 的延迟时间)

当然,作为开关用的装置必须具备稳定的结构,才能消耗大量的累增崩溃电量 (avalanche energy),以确保整个安全操作范围 (SOA)的运作都正常可靠。

装置概念及技术

NexFETTM 技术是电源应用的新一代 MOSFET,其中采用能够成功放大无线射频 (RF) 信号的横向扩散金属氧化物半导体 (LDMOS) 装置;见图 1剖面示意图。电流会从最上层金属化源极端流经平面闸极下方的侧边通道,并流至轻掺杂汲极 (LDD) 延伸区域,然后借由低阻抗的垂直沉片 (vertical sinker) 转向基板。无线射频可提供最低的内部电容,而垂直电流可提供高电流密度,完全没有 LDMOS 晶体管平面配置常出现的解偏压问题。

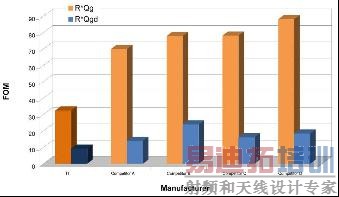

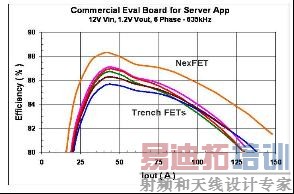

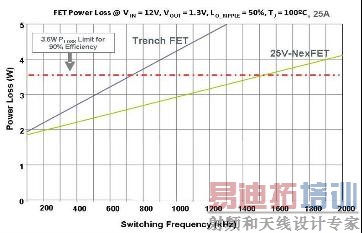

图 1. NexFET 装置的剖面示意图 NexFET 装置的源极金属化具有独特的拓朴,可在闸极的汲极隅点达到场效电板 (field-plate) 效应。场效电板能够沿着 LDD 区域进行电场散布,因此能够降低闸极隅点的高电场峰值,最终能够有效抑制热载子 (hot carrier effect) 效应,此效应会造成一般常用 LDMOS 晶体管内闸极氧化物质量的恶化。 利用 LDD、场效电板及下方深 P 区域的电荷平衡,LDD 区域会提升到高度载子集中的程度。这有助于将装置的阻抗 (RDS(on)) 降至最低。深 P 掺杂也可用来提供信道区域下方的一个大型电荷,以抑制短通道效应 (short channel effect)。如此的做法可设计出较短的通道,而不会产生任何与贯穿效应 (punch-through effect) 相关的问题。在连接至源极植入区域的浅沟槽中,会执行源极接触。掺杂分布 (doping profile) 工程技术可用来找出高汲极电压的电气故障位置。进而找出远离闸极氧化物的累增崩溃产生热载子,并且确保内部双极晶体管结构不会达到极高的累增崩溃电流密度而被触发。 最近二十年来,沟槽 MOSFET 已成为低电压 (小于 100V) 电源开关最成功的技术。图 2 为沟槽及 NexFET 技术的比较。沟槽技术的主要优点是主动式电池节距内具备高信道密度。然而,大区域的沟槽壁不利于缩小内部电容的体积。另外,沟槽下方外延层的中等掺杂程度使得晶体管的阻抗无法加以调整,并且会限制低汲极电压应用 (例如低于 20V VDS,max) 中FET设计所具有的优点。

|