- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

多通道模/数转换器AD7890与DSP的接口设计

录入:edatop.com 点击:

随着工业技术进步,对数字控制伺服系统中执行效率和集成化程度的要求越来越高。比如用单处理器控制多个伺服系统时,对多通道A/D转换的效率要求较高。以往较多地使用多路模拟开关与单通道A/D转换器来实现,效率较低,使用模拟开关带来的噪声也比较严重。在此,选用串行多通道A/D转换器AD7890与TMS320F2812处理器的SPI接口组成A/D转换模块,非常适合应用于多轴伺服系统。AD7890是一款8通道12位串行A/D转换器,具有高转换效率(转换时间仅为5.9μs)、高速灵活的串行接口、多通道等优点。其中,AD7890-10输入电压范围为-10~+10 V。TMS320F2812处理器上集成了多种先进的外设,为实现电机及其他运动控制领域的应用提供了良好的平台,它所提供的SPI接口通常用于DSP处理器和外部设备及其他处理器之间的通信。SPI分主、从两种工作方式,数据长度可编程(1~16 b),并能同时进行接收和发送操作,通常用于DSP处理器和外部外设以及其他处理器之间的通信,这使它能很方便地与AD7890采用主/从模式进行通信。

1 AD7890工作模式和原理

AD7890的SMODE引脚是工作模式控制输入端,它决定了器件是工作于外部时钟模式(作为从设备),还是内部时钟模式(作为主设备)。当SMODE置于高电平时,器件工作在外部时钟模式,由主设备提供时钟信号SCLK和接收帧同步信号RFS,AD7890可接收的最大串行时钟频率达10 MHz;当SMODE置于低电平时,器件工作在内部时钟模式,自身提供时钟信号SCLK和接收帧同步信号RFS,其时钟频率由CLK引脚输入时钟频率决定。本文以DSP作为主控制器,AD7890作为从设备,由DSP的SPI口提供串行时钟。

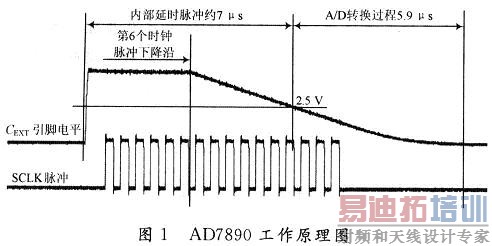

AD7890通过片内高速双向串行数据接口接收控制字和输出转换结果。通过向控制寄存器写数据可以确定转换通道、转换开始信号等信息。其控制寄存器包含5位数据,因此至少需要6个SCLK脉冲才能完成对寄存器的写操作。其中,A2,A1,A0分别为通道地址选择最高位、次高位、最低位。通道选择算法为:通道号=4A2+2A1+A2+1。发送数据的第5个SCLK脉冲下降沿过后的数据均为无效数据。控制字写入寄存器后,器件即启动内部延时脉冲,保证在转换开始前跟踪/保持器有足够的时间来完成转换通道的建立和切换。该延时脉冲宽度取决于引脚电容的CEXT值。一般引脚电容值取CEXT、120 pF或200 pF。据测试,此时延时脉冲宽度分别约为7.Oμs和9.6μs。向控制寄存器写数据时CEXT,引脚电平由低变高,电容在第6个时钟脉冲的下降沿开始放电,电压降低至2.5 V以下时内部延时脉冲结束,同时A/D转换开始,5.9μs后转换结束。若此时串行读操作已完成,且RFS已变高为高电平,则用新的转换结果更新输出寄存器。至此,一次A/D转换结束。图1为AD7890工作原理图,从示波器获取的图片显示了CEXT引脚电平、SCLK脉冲与A/D转换过程时间的关系。

2 AD7890工作时序与读写操作方法

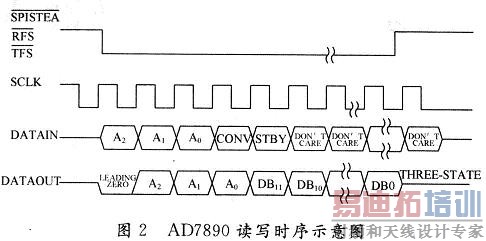

控制AD7890的转换开始有两种方法。一是,硬件控制,即将CONVST引脚置低,器件产生一个窄低电平脉冲,在脉冲的上升沿A/D转换开始,前提是须向CONV位写0;二是,软件控制,即向控制寄存器的cONV位写1,此时CONVST引脚不起作用。二者区别在于,采用硬件控制转换开始时,在CONVS丽上升沿启动转换,此时必须保证内部延时脉冲已经结束;对于软件控制,内部延时脉冲结束时转换立即开始。需要说明的是,在向控制寄存器写数据时,6个写操作时钟脉冲结束前,发送帧同步信号TFS必须保持低电平,否则写操作不能成功。而读取A/D转换结果期间,接收帧同步信号RFS必须保持低电平。RFS和TFS连在一起,使SPI口的读、写操作同时进行。以DSP作为主设备,AD7890作为从设备,即工作在外部时钟模式下,此时读、写操作时序分别如图2所示。DSP的SPISTE丽引脚具有从设备片选功能,该引脚为低时可向从设备发送数据,文中将该引脚作为通用收、发帧同步信号来控制RFS和TFS。

3 AD7890与TMS320F2812的SPI接口硬件实现

TMS320F2812是TI公司推出的数字信号处理器,它在电机控制方面性能优越,使其在工业控制中得到了非常广泛的应用。它所提供的串行外设接口(SPI)是一个高速同步的串行输入/输出口,包含4个外部引脚:从输出/主输入引脚(SPISOMI)、从输入/主输出引脚(SPISIMO)、从发送使能引脚(SPISTE)、串行时钟引脚(SPICLK)。SPI主要特点是可以同时发送和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志。

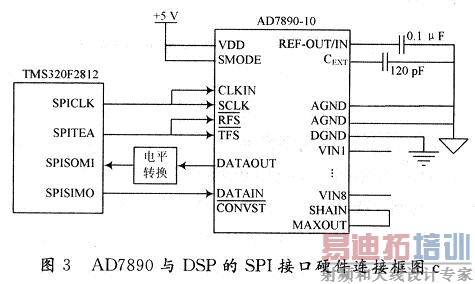

确定DSP的低速外设时钟LSPCLK后,通过波特率控制寄存器SPIBRR,确定波特率SCLK。波特率具体计算方法是:当SPIBRR=3~127时,SCLK=LSPCLK/(SPIBRR+1);当SPIBRR=0,1,2时,SCLK=LSPCLK/4,因此共具有125种可编程波特率。文中,DSP的工作频率为120 MHz,低速时钟LSPCLK为30 MHz,故可编程波特率范围为234.375 kb/s~7.5 Mb/s。通过提高系统低速时钟,可以提高可编程波特率范围;通过选较高的波特率,能提高数据传输速率,即提高A/D的转换效率。AD7890-10与TMS320一F2812的SPI接口硬件连接框图如图3所示。

[p]

由于AD7890-10数据电平为5 V,而TMS320F2812的I/O所能承受的电压最高为3.3 V,因此必须对A/D转换结果进行电平转换,将其转换为I/0口可承受的电压。把5 V电平转为3.3 V电平有多种方法。常用的有两种。一是选用专门的电平转换器件,如TI公司的SN74I.VTHl6245;二是把A/D转换结果通过系统中CPLD的I/O口再输出到DSP,前提是所选CPLD可承受输入电压为5 V,而输出为3.3 V。本文采用后一种方法,选用的是Altera公司的EPM7128ST1100-10,给CPLD的I/O口供3.3 V电源即可满足要求。将A/D数据通过一个CPLD的一个I/O口转接,经软件进行逻辑处理后输出至DSP即可。需要注意的是,为避免噪声干扰,AD7890的所有未用引脚不能悬空,必须接可承受范围内的固定电平。实验表明,特别是CLKIN引脚不能悬空,否则可能导致A/D转换不能成功。对于AD7890-10,当未使用的输入通道电压值低于-12 V时会对所选其他通道的转换造成严重干扰。文中采取的方法是将外部时钟输入引脚SCLK与内部时钟输入引脚CLKIN相连,可以有效去除干扰。

4 软件读写实现

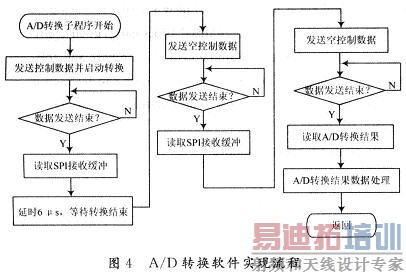

对于SPI接口而言,数据与串行时钟脉冲是同时产生的,即只有数据线上有数据传送时才产生时钟脉冲。所以发送控制数据结束后,DSP收到的数据并不是真实的A/D转换结果,但需要读取接收缓冲寄存器数据使SPI复位。多次实验表明,对于单次A/D转换,在转换结束后需要再向AD7890发送2次空控制数据0x0000,之后DSP的SPI接收缓冲寄存器中的数据才是正确的A/D转换结果,即每次A/D采样循环需要进行三次数据交换才能得到有效A/D转换数据。采用查询方式判断数据是否发送结束,即SPI状态寄存器SPIINT FLAG位为1时表示已完成数据发送。软件实现A/D转换的流程框图如图4所示。

对于AD7890-10,A/D转换结果数据为二进制补码格式,且包含通道数据,因此读取结果后应根据需要对数据进行适当处理,包括屏蔽通道选择数据和进行码制转换等,以便换算成系统所需要的数字量。为便于处理,将-10~+10 V电压对应的码值转换为0~4 096。文中处理方法为:将转换结果高四位通道数据屏蔽后,若A/D输入为正电压,则获取低12位结果与0x0800相加得到处理后的数据;若A/D输入为负电压,则将补码转换成原码后与0xF800作差获取处理结果。

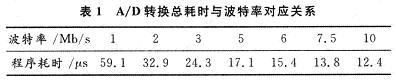

经多次测试,得到A/D转换子程序运行时间(即一次A/D转换总耗时)与波特率对应关系如表1所示。

从表1中可以看出,为提高转换效率,应在可承受范围内选择尽可能高的波特率,但不应超过AD7890-10的上限值10 Mb/s。对文中SPI接口的实际应用表明,A/D转换性能非常稳定,效率较高,转换精度高,误差仅为±1码,约4.88 mV。

5 结 语

用DSP的串行外设接口SPI与串行多通道A/D转换器AD7890组成数字伺服系统A/D转换功能实现模块,能完成8个通道模拟量到数字量的转换,效率较高,接口简单,性能稳定。通过选择较高的波特率可以缩短数据传输时间,提高A/D转换效率。当DSP提供的外部时钟SCLK为AD7890所能承受的最高值10 MHz时,单个通道彻底完成一次A/D转换仅需12.4μs。本文所做的接口设计为多轴数字控制系统的A/D转换模块提供了一种实用的选择与参考。

编辑:博子

1 AD7890工作模式和原理

AD7890的SMODE引脚是工作模式控制输入端,它决定了器件是工作于外部时钟模式(作为从设备),还是内部时钟模式(作为主设备)。当SMODE置于高电平时,器件工作在外部时钟模式,由主设备提供时钟信号SCLK和接收帧同步信号RFS,AD7890可接收的最大串行时钟频率达10 MHz;当SMODE置于低电平时,器件工作在内部时钟模式,自身提供时钟信号SCLK和接收帧同步信号RFS,其时钟频率由CLK引脚输入时钟频率决定。本文以DSP作为主控制器,AD7890作为从设备,由DSP的SPI口提供串行时钟。

AD7890通过片内高速双向串行数据接口接收控制字和输出转换结果。通过向控制寄存器写数据可以确定转换通道、转换开始信号等信息。其控制寄存器包含5位数据,因此至少需要6个SCLK脉冲才能完成对寄存器的写操作。其中,A2,A1,A0分别为通道地址选择最高位、次高位、最低位。通道选择算法为:通道号=4A2+2A1+A2+1。发送数据的第5个SCLK脉冲下降沿过后的数据均为无效数据。控制字写入寄存器后,器件即启动内部延时脉冲,保证在转换开始前跟踪/保持器有足够的时间来完成转换通道的建立和切换。该延时脉冲宽度取决于引脚电容的CEXT值。一般引脚电容值取CEXT、120 pF或200 pF。据测试,此时延时脉冲宽度分别约为7.Oμs和9.6μs。向控制寄存器写数据时CEXT,引脚电平由低变高,电容在第6个时钟脉冲的下降沿开始放电,电压降低至2.5 V以下时内部延时脉冲结束,同时A/D转换开始,5.9μs后转换结束。若此时串行读操作已完成,且RFS已变高为高电平,则用新的转换结果更新输出寄存器。至此,一次A/D转换结束。图1为AD7890工作原理图,从示波器获取的图片显示了CEXT引脚电平、SCLK脉冲与A/D转换过程时间的关系。

|

控制AD7890的转换开始有两种方法。一是,硬件控制,即将CONVST引脚置低,器件产生一个窄低电平脉冲,在脉冲的上升沿A/D转换开始,前提是须向CONV位写0;二是,软件控制,即向控制寄存器的cONV位写1,此时CONVST引脚不起作用。二者区别在于,采用硬件控制转换开始时,在CONVS丽上升沿启动转换,此时必须保证内部延时脉冲已经结束;对于软件控制,内部延时脉冲结束时转换立即开始。需要说明的是,在向控制寄存器写数据时,6个写操作时钟脉冲结束前,发送帧同步信号TFS必须保持低电平,否则写操作不能成功。而读取A/D转换结果期间,接收帧同步信号RFS必须保持低电平。RFS和TFS连在一起,使SPI口的读、写操作同时进行。以DSP作为主设备,AD7890作为从设备,即工作在外部时钟模式下,此时读、写操作时序分别如图2所示。DSP的SPISTE丽引脚具有从设备片选功能,该引脚为低时可向从设备发送数据,文中将该引脚作为通用收、发帧同步信号来控制RFS和TFS。

|

TMS320F2812是TI公司推出的数字信号处理器,它在电机控制方面性能优越,使其在工业控制中得到了非常广泛的应用。它所提供的串行外设接口(SPI)是一个高速同步的串行输入/输出口,包含4个外部引脚:从输出/主输入引脚(SPISOMI)、从输入/主输出引脚(SPISIMO)、从发送使能引脚(SPISTE)、串行时钟引脚(SPICLK)。SPI主要特点是可以同时发送和接收串行数据;可以当作主机或从机工作;提供频率可编程时钟;发送结束中断标志。

确定DSP的低速外设时钟LSPCLK后,通过波特率控制寄存器SPIBRR,确定波特率SCLK。波特率具体计算方法是:当SPIBRR=3~127时,SCLK=LSPCLK/(SPIBRR+1);当SPIBRR=0,1,2时,SCLK=LSPCLK/4,因此共具有125种可编程波特率。文中,DSP的工作频率为120 MHz,低速时钟LSPCLK为30 MHz,故可编程波特率范围为234.375 kb/s~7.5 Mb/s。通过提高系统低速时钟,可以提高可编程波特率范围;通过选较高的波特率,能提高数据传输速率,即提高A/D的转换效率。AD7890-10与TMS320一F2812的SPI接口硬件连接框图如图3所示。

|

4 软件读写实现

对于SPI接口而言,数据与串行时钟脉冲是同时产生的,即只有数据线上有数据传送时才产生时钟脉冲。所以发送控制数据结束后,DSP收到的数据并不是真实的A/D转换结果,但需要读取接收缓冲寄存器数据使SPI复位。多次实验表明,对于单次A/D转换,在转换结束后需要再向AD7890发送2次空控制数据0x0000,之后DSP的SPI接收缓冲寄存器中的数据才是正确的A/D转换结果,即每次A/D采样循环需要进行三次数据交换才能得到有效A/D转换数据。采用查询方式判断数据是否发送结束,即SPI状态寄存器SPIINT FLAG位为1时表示已完成数据发送。软件实现A/D转换的流程框图如图4所示。

|

经多次测试,得到A/D转换子程序运行时间(即一次A/D转换总耗时)与波特率对应关系如表1所示。

|

5 结 语

用DSP的串行外设接口SPI与串行多通道A/D转换器AD7890组成数字伺服系统A/D转换功能实现模块,能完成8个通道模拟量到数字量的转换,效率较高,接口简单,性能稳定。通过选择较高的波特率可以缩短数据传输时间,提高A/D转换效率。当DSP提供的外部时钟SCLK为AD7890所能承受的最高值10 MHz时,单个通道彻底完成一次A/D转换仅需12.4μs。本文所做的接口设计为多轴数字控制系统的A/D转换模块提供了一种实用的选择与参考。

编辑:博子

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>