- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高分辨率数字电位器的软件实现

录入:edatop.com 点击:

引言

与机械电位器相比,数字电位器有许多优点。但是在有些应用场合,数字电位器的分辨率往往达不到设计要求,通常最大抽头数为1 024。以X9241为例,内部包括一个I2C接口和4个64抽头的数字电位器,可独立使用,也可串联使用,如按常规方法使用,其分辨率较低,即使4个电位器串联,也只能达到256个抽头。本文提出了一种软件、硬件结合的方法,可使电位器的中间抽头数达到8 001个,分辨率达到O.008%。

1 设计原理

1.1 基本原理

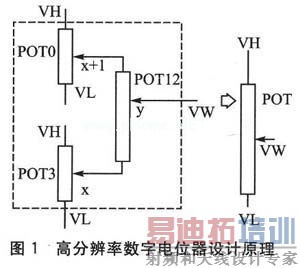

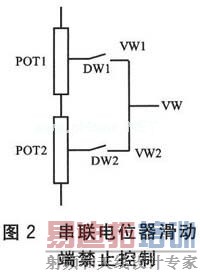

高分辨率数字电位器POT由4个电位器组成,如图1所示,4个数字电位器POT0、POT1、POT2、POT3均为64抽头数字电位器。 POTO、 POT3的固定端并联,滑动端分别接POT12的固定端。POT12由POT1、POT2串联,组成一个127抽头的电位器。4个独立电位器阻值相等,可根据需要选取。高分辨率数字电位器的固定端为VH、VL,滑动端为VW,VW由POT1、POT2的2个滑动端并连。

假设POT0、POT1、POT2、POT3、POT12的滑动端位置分别为x0、x1、x2、x3、y,POT的滑动端位置为z。

现采取以下控制策略:

①若POT3的滑动端位置为x,则POTO的滑动端位置同步调节到x+1,即两电位器始终保持1的间隔,相当于粗调节;

②调节POTl2滑动端位置y,相当于把间隔为1的区间再细分若干等分,即细调节。

采用等校电路法,可得到z与x、y的关系。

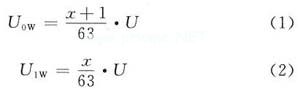

设VL、VH端电位分别为0、U,滑动端电位为UW,根据电学公式可得:

其中,U0W、U1W分别为POT1、POT1滑动端输出电位,并加到POT12的两个固定端。

由式(1)、式(2)推出式(3),得VW端输出电位。

即电位器POT的滑动端相对于VL的电阻阻值为:

若规定z的步进增量为1,则有:

其中,R为电位器固定端的阻值,x的取值范围为0~62,y的取值范围为0~127。z的取值范围为0~8 001。分辨率为O.008%,中间抽头数为8 001个。

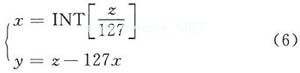

因为x、y、z均为整数,所以有:

即x为z/127的取整,y为z/127的取余。

1.2 控制算法

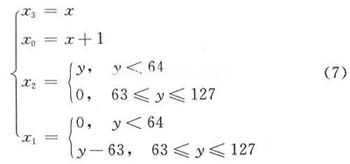

式(5)、(6)即为实现高分辨率数字电位器的基本公式。为了软件设计,还必须建立POT的中间抽头位置z与POT0、POT1、POT2、POT3的中间抽头位置的关系。

根据图1可知:

2 硬件电路

2.1 X9241数字电位器

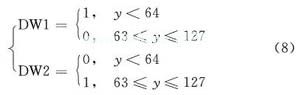

X9241是Xicor公司生产的数字电位器,内部包括1个I2C接口和4个64位数字电位器POTO、POT1、POT2、POT3。每个数字电位器由电阻阵列及与之对应的滑动端计数寄存器WCR、4个位数据寄存器R0~R3等部分构成。其引脚配置如图3所示。

[p]

每个电位器由63个电阻段组成,每个电阻阵列的物理终端等效于机械电位器的固定端(VH、VL)。每个阵列的VH和VL以及每个电阻段之间的接点(即抽头)通过FET开关连接滑动输出端,而滑动端在电阻阵列中的位置由从WCR控制。其中,VW、VW1、VW2、VW3分别为4个电位器的滑动端,VL0、 VL1、VL2、VL3分别为4个电位器的低端、VH0、VH1、VH2、VH3分别为4个电位器的高端。如果将4个电阻阵列中的2个、3个或4个串联,可构成127、190或253抽头的数字电位器。芯片采用I2C总线接口,SDA、SCL分别为串行数据和串行时钟。A0~A3为芯片地址设置位。

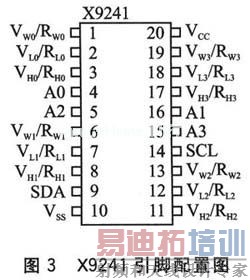

X9241提供了把阵列串联起来的方法,可以把1个阵列的63个电阻元件与1个相邻阵列的电阻元件串联起来。其控制位在3字节的指令中,其数据字节包括用来定义滑动端位置的6位(LSB)加上高2位:CM(串联方式)和DW(禁止滑动端)。数据字节如下所示:

2.2 电路设计

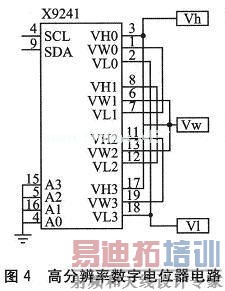

根据图1的设计原理和图3的引脚配置图,可实现高分辨率数字电位器的电路设计,如图4所示。

①SDA、SCL是I2C总线的串行数据和串行时钟,与单片机的I/O线相连,单片机是主器件,X9241是从器件,器件地址为:

0 1 0 1 A3 A2 A1 A0

高4位固定,低4位由A3~A0的接线方式所决定,按照图4电路的接线方式,X9241的从地址为50H。

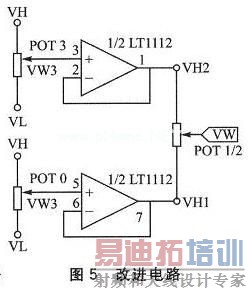

②为了提高线性度,可在VW0与VL1之间加入1级运算放大器组成的跟随器,VW3与VH2之间也加入1级。其改进电路如图5所示。

[p]

3 程序设计

3.1 读写单个数字电位器函数设计

根据X9241的指令结构和控制时序,可以编写读写单个数字电位器的程序。

(1)改变电位器中间抽头命令(写WCR)时序以写电位器POT0为例,把电位器0的中间抽头WCR设置为20H(X9241每个电位器的最大抽头数是 64,即有效值小于63)。命令控制字为101000000B,即AOH;若在电路中AOA1A2A3均接低电平,则器件地址为01010000B,即 50H。其命令序列如下:

Start→发送地址50H→Ack→发送命令字A0H→ACK→发送20H→ACK→Stop。

(2)读电位器中间抽头位置命令(读WCR)时序以读电位器POT1为例,把电位器1的中间抽头WCR位置值读回。命令控制字为100100000B,即90H;若在电路中AOA1A2A3均接低电平,则器件地址为01010000B,即50H。其命令序列如下:

Start→发送地址50H→Ack→发送命令字90H→ACK→接收1个字节→ACK→Stop。

3.2 主函数设计

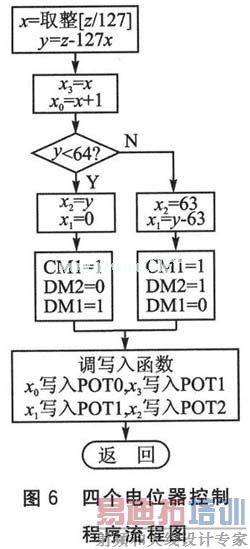

本函数的功能是把设计的数字电位器POT的中间抽头位置z转换为4个独立数字电位器POT0~POT3的中间抽头位置寄存器WCR的值x0~x3,同时控制POT1、POT2的控制位CM和DW,如图6所示。

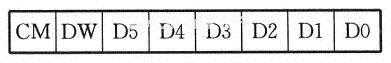

在流程图中,当y<64时,POT12(由POT1和POT2串联)的中间抽头位置在POT2范围内,所以POT1的中间抽头失效,即置DM1=1;当y≥64时,POT12的中间抽头位置在POT1范围内,所以POT2的中间抽头失效,即置DM2=1。

结语

采用软硬件协同的方法,能以较低的成本实现高分辩率数字电位器的设计。同一芯片中4个数字电位器的良好匹配和电压跟随器的应用,使设计的数字电位器具有更好的线性度。在实际应用中,为了提高带负载能力,需要在滑动输出端接一输出缓冲器。

发布者:博子

与机械电位器相比,数字电位器有许多优点。但是在有些应用场合,数字电位器的分辨率往往达不到设计要求,通常最大抽头数为1 024。以X9241为例,内部包括一个I2C接口和4个64抽头的数字电位器,可独立使用,也可串联使用,如按常规方法使用,其分辨率较低,即使4个电位器串联,也只能达到256个抽头。本文提出了一种软件、硬件结合的方法,可使电位器的中间抽头数达到8 001个,分辨率达到O.008%。

1 设计原理

1.1 基本原理

高分辨率数字电位器POT由4个电位器组成,如图1所示,4个数字电位器POT0、POT1、POT2、POT3均为64抽头数字电位器。 POTO、 POT3的固定端并联,滑动端分别接POT12的固定端。POT12由POT1、POT2串联,组成一个127抽头的电位器。4个独立电位器阻值相等,可根据需要选取。高分辨率数字电位器的固定端为VH、VL,滑动端为VW,VW由POT1、POT2的2个滑动端并连。

|

假设POT0、POT1、POT2、POT3、POT12的滑动端位置分别为x0、x1、x2、x3、y,POT的滑动端位置为z。

现采取以下控制策略:

①若POT3的滑动端位置为x,则POTO的滑动端位置同步调节到x+1,即两电位器始终保持1的间隔,相当于粗调节;

②调节POTl2滑动端位置y,相当于把间隔为1的区间再细分若干等分,即细调节。

采用等校电路法,可得到z与x、y的关系。

设VL、VH端电位分别为0、U,滑动端电位为UW,根据电学公式可得:

|

其中,U0W、U1W分别为POT1、POT1滑动端输出电位,并加到POT12的两个固定端。

由式(1)、式(2)推出式(3),得VW端输出电位。

即电位器POT的滑动端相对于VL的电阻阻值为:

其中,R为电位器固定端的阻值,x的取值范围为0~62,y的取值范围为0~127。z的取值范围为0~8 001。分辨率为O.008%,中间抽头数为8 001个。

因为x、y、z均为整数,所以有:

|

即x为z/127的取整,y为z/127的取余。

1.2 控制算法

式(5)、(6)即为实现高分辨率数字电位器的基本公式。为了软件设计,还必须建立POT的中间抽头位置z与POT0、POT1、POT2、POT3的中间抽头位置的关系。

根据图1可知:

|

|

|

2 硬件电路

2.1 X9241数字电位器

X9241是Xicor公司生产的数字电位器,内部包括1个I2C接口和4个64位数字电位器POTO、POT1、POT2、POT3。每个数字电位器由电阻阵列及与之对应的滑动端计数寄存器WCR、4个位数据寄存器R0~R3等部分构成。其引脚配置如图3所示。

|

X9241提供了把阵列串联起来的方法,可以把1个阵列的63个电阻元件与1个相邻阵列的电阻元件串联起来。其控制位在3字节的指令中,其数据字节包括用来定义滑动端位置的6位(LSB)加上高2位:CM(串联方式)和DW(禁止滑动端)。数据字节如下所示:

|

根据图1的设计原理和图3的引脚配置图,可实现高分辨率数字电位器的电路设计,如图4所示。

|

①SDA、SCL是I2C总线的串行数据和串行时钟,与单片机的I/O线相连,单片机是主器件,X9241是从器件,器件地址为:

0 1 0 1 A3 A2 A1 A0

高4位固定,低4位由A3~A0的接线方式所决定,按照图4电路的接线方式,X9241的从地址为50H。

②为了提高线性度,可在VW0与VL1之间加入1级运算放大器组成的跟随器,VW3与VH2之间也加入1级。其改进电路如图5所示。

|

3.1 读写单个数字电位器函数设计

根据X9241的指令结构和控制时序,可以编写读写单个数字电位器的程序。

(1)改变电位器中间抽头命令(写WCR)时序以写电位器POT0为例,把电位器0的中间抽头WCR设置为20H(X9241每个电位器的最大抽头数是 64,即有效值小于63)。命令控制字为101000000B,即AOH;若在电路中AOA1A2A3均接低电平,则器件地址为01010000B,即 50H。其命令序列如下:

Start→发送地址50H→Ack→发送命令字A0H→ACK→发送20H→ACK→Stop。

(2)读电位器中间抽头位置命令(读WCR)时序以读电位器POT1为例,把电位器1的中间抽头WCR位置值读回。命令控制字为100100000B,即90H;若在电路中AOA1A2A3均接低电平,则器件地址为01010000B,即50H。其命令序列如下:

Start→发送地址50H→Ack→发送命令字90H→ACK→接收1个字节→ACK→Stop。

3.2 主函数设计

本函数的功能是把设计的数字电位器POT的中间抽头位置z转换为4个独立数字电位器POT0~POT3的中间抽头位置寄存器WCR的值x0~x3,同时控制POT1、POT2的控制位CM和DW,如图6所示。

|

在流程图中,当y<64时,POT12(由POT1和POT2串联)的中间抽头位置在POT2范围内,所以POT1的中间抽头失效,即置DM1=1;当y≥64时,POT12的中间抽头位置在POT1范围内,所以POT2的中间抽头失效,即置DM2=1。

结语

采用软硬件协同的方法,能以较低的成本实现高分辩率数字电位器的设计。同一芯片中4个数字电位器的良好匹配和电压跟随器的应用,使设计的数字电位器具有更好的线性度。在实际应用中,为了提高带负载能力,需要在滑动输出端接一输出缓冲器。

发布者:博子

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>