- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

峰值检测器

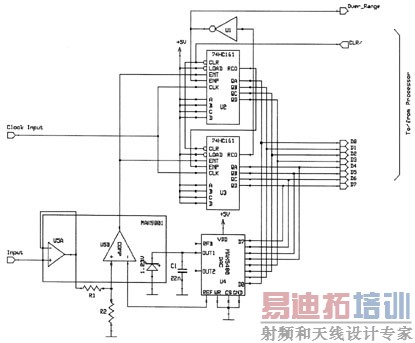

图1电路用于检测模拟信号峰值,该电路避免了以往峰值检测电路的弊端:有限的保持时间、检测性能对保持电容参数极为敏感、需要输入电阻极大的高速缓冲器等。另外,该电路在无需专用模/数转换器的前提下实现了模拟到数字的转换。

图中MAX9001比较器内部包括:放大器、1.25V电压基准和比较器,放大器用于信号缓冲或滤波(如抗混叠滤波),电阻R1、R2将输入信号的最大值限制在1.23V,峰值检测器的信号检测范围由基准电压确定,比较器U5B将衰减后的输入信号与前期存储的峰值电压进行比较,如果输入信号高于以前存储的峰值电压,则比较器输出高电平,允许U2、U3构成的8位同步计数器以输入时钟确定的速率累计计数,随着计数器数值的增加,模/数转换器(DAC)输出增大,当输入信号低于计数器内锁存的峰值电压时,比较器U5B输出为低电平,终止计数。模/数转换由MAX5480(U4)完成,MAX5480为并行接口、8位R-2R DAC,本电路中将其配置为单电源模式:OUT1引脚为基准电压输入、REF引脚为DAC输出,DAC的WR、CS引脚置为低电平使其处于"全通"状态,数据总线的任何变化均可迅速反应到DAC的输出端。

该电路所允许的最大时钟频率由计数器、DAC和比较器延迟时间的总和确定,本电路中总计延迟时间为:48ns + 500ns + 370ns = 918ns,允许选用任何频率低于1MHz的时钟。时钟频率的选择主要取决于输入信号的最大压摆率。反相器U1保证计数器数值达到FFH时停止计数,U1输出可用于输入信号超量程指示,微处理器也可以直接读取计数器数值FFH检测模拟输入是否超出满量程范围。来自微处理器的CLR信号用于峰值检测器的控制,当CLR为低电平时计数器被复位,CLR为高电平时峰值检测器处于正常工作状态。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...