- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

实现小巧可靠的低噪声电源解决方案

基于现代高性能处理器和FPGA的系统需要越来越多的专用电源轨来为内核、IO、存储器和精密模拟电路供电。当今典型的处理器系统通常使用独立开关稳压器和LDO供电,但随着电路板面积越来越小,设计更高效率电源管理系统变得日益困难。将多个开关稳压器和LDO合并到单个封装中,可以实现超小型、灵活、高效率电源管理解决方案,为微处理器/FPGA和精密模拟器件供电,且系统可靠性最高。这种新型全集成式多路输出稳压器为FPGA和处理器系统的电源设计人员带来四大好处:

1: 解决方案尺寸

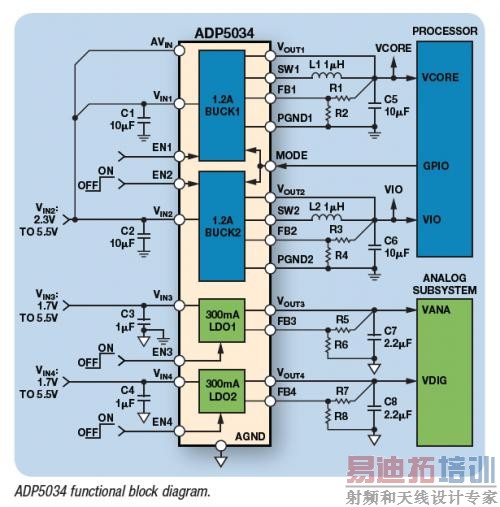

将多个开关降压稳压器、LDO、电源监控器和看门狗功能集成到单芯片解决方案中,可以大幅缩小多轨电源解决方案的PCB面积。ADP5034就是一个很好的范例,它是一款集成两个300mA LDO的双通道1.2A降压稳压器,采用24引脚LFCSP封装。

ADP5034在单个封装中集成多个开关稳压器和LDO,实现新一代高集成度多路输出稳压器,只需非常小的电路板空间。集成开关稳压器以3MHz开关频率工作,允许使用非常小的片式电感。当两个开关稳压器同时使能并以PWM模式工作时,二者配置为异相运行,以便降低所需输入电容的大小和成本,进一步缩小外部元件的尺寸,同时将所产生的电磁干扰(EMI)降至最低。

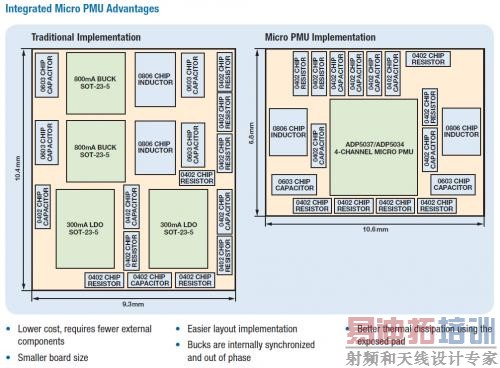

下图显示分立与集成两种解决方案的对比:左图是由两个1.2A降压稳压器和两个300mA LDO组成的示例布局,右图是单芯片ADP5034多路输出稳压器。分立电源解决方案需要将22个器件贴装在97mm2 PCB面积上,而ADP5034解决方案只需将19个器件贴装在72mm2 PCB面积上。ADP5034解决方案所需的PCB面积减少35%,并且节省了贴装3个器件的成本。

2: 易于使用

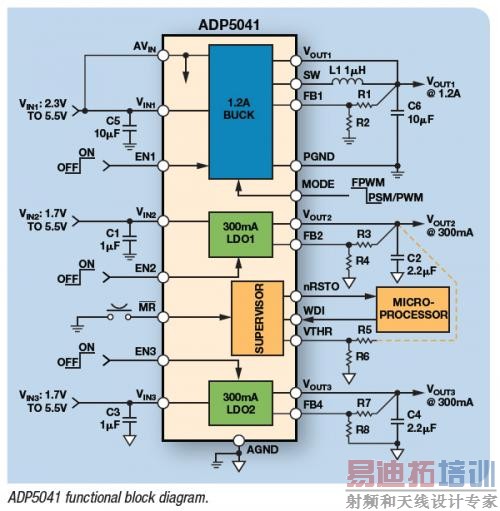

新产品的设计周期越来越短,初始阶段易于设计、未来又能根据设计要求轻松修改的新型电源解决方案对于保证新产品发布日期日益重要。ADP5041多路输出稳压器提供一个1.2A降压稳压器和两个300mA LDO,并集成上电复位功能和看门狗定时器以支持基于高可靠性处理器的系统。ADP5041的所有集成稳压器都有专用使能引脚,为电源设计工程师提供极大的灵活性,可以通过硬件使能或禁用各稳压器,无需任何软件工作,并且可以轻松控制三个电源轨的上电时序。各稳压器的输出电压利用外部电阻分压器设置,电源设计工程师同样可以利用这一点来轻松快捷地更改输出电压,从而满足原型开发和需要不同输出电压组合的新设计。多路输出稳压器的各集成稳压器都有独立的使能引脚和电阻可编程的输出电压,有助于降低电源设计的复杂度,缩短设计时间,加快新产品上市。ADI uPMU内置针对各种输入/输出电压和输出电容的补偿功能,此外还集成软启动和保护电路(UVLO、TSD、过流等)。所有这些特性极大地减少了工程师的设计和故障排除时间。每种器件的引脚排列都考虑到了简化电路板布局和器件贴放的需求,无源器件可以尽可能靠近各稳压器放置,使布线距离最短,这对于尽量降低电路板寄生效应和噪声非常重要。对电源电路设计知之甚少甚至一无所知的工程师再也无须害怕使用复杂的多路输出稳压器,只需按照数据手册所述的简单电路板布局布线和元件选择指南操作即可。

3: 系统可靠性更高

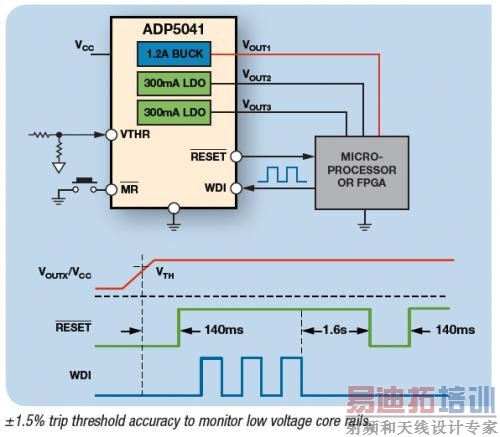

与基于分立稳压器的设计相比,多路输出单芯片稳压器设计所需的器件数量更少,因而PCB上需要贴放和检查的器件更少,制造成本更低,制造可靠性更高。将电源监控器和看门狗定时器与多个稳压器集成为单芯片解决方案,可以实现更高的系统可靠性。ADP5041多路输出稳压器集成了一个高精度上电复位电路,它可以监控ADP5041的输入电压或任一输出电压轨。在基于处理器的典型系统中,上电复位电路(电源监控器)用来确保内核电压轨处于正确的电平,然后才会让处理器离开复位状态。随着新型处理器和FPGA的内核电压轨越来越低,高精度上电复位电路变得更加重要。ADP5041提供外部电阻可编程的上电复位,整个温度范围内的精度为±1.5%。利用这种集成式高精度上电复位电路,可以精准可靠地监控最新一代处理器、ASIC和FPGA的低压内核电源轨,从而提高最终产品的可靠性。该上电复位电路的电阻可编程能力还意味着,新设计可以轻松快捷地设置给定内核电压的跳变阈值电压。

利用集成的看门狗定时器可以监控微处理器代码执行活动,保证处理器安全可靠地工作。看门狗定输入引脚(WDI)上的每次低到高或高到低逻辑跃迁都会使定时器电路清零,它能检测最短50 ns的脉冲。如果定时器在预设的看门狗超时期间(tWD)计时,复位就会置位。微处理器需要使WDI引脚发生跳变以避免复位。因此,如果在超时时间内微处理器未能使WDI跳变,则说明发生代码执行错误,由此产生的复位脉冲将重新启动微处理器并使其进入已知状态。

除了WDI上的逻辑跃迁外,VCC欠压或/MR变为低电平所导致的复位置位也会将看门狗定时器清零。复位置位时,看门狗定时器清零,直到复位解除置位后才重新开始计时。ADP5041具有一个特殊电路,它能检测WDI引脚上的看门狗刷新输入端施加的三态条件,WDI引脚通常由处理器/DSP输出端口控制。当处理器将此端口设为三态模式时,看门狗刷新定时器禁用,防止看门狗复位处理器。当器件支持处理器/DSP休眠工作模式时,此特性非常重要,此时内核禁用,看门狗定时器无法刷新。此外它还提供丰富的订购选项,可以满足其它常见的复位和看门狗时序要求。

所有集成稳压器都有可选的工厂可编程有源下拉电阻,用于在稳压器被使能引脚、Vin欠压(UVLO)或热关断(TSD)禁用时将相应的输出电容放电。有源下拉电阻确保稳压器关断时,输出电压立即被拉至GND,从而提高系统可靠性,确保输出电容上无残余电压,避免周期供电期间发生闩锁事件。

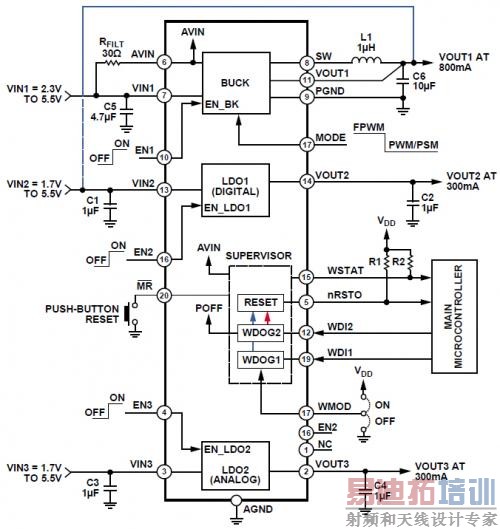

为提高电表等远程系统的可靠性和正常工作时间,该多路输出稳压器集成了另一个看门狗电路,如果系统不能正常工作或正确响应,远程系统可以自动"周期供电"。ADP5042是一款集成两个300mA LDO、上电复位和双通道看门狗定时器的800mA降压稳压器。

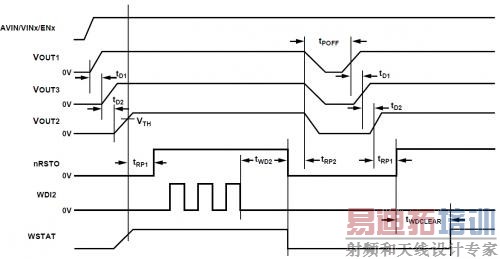

看门狗定时器1 (WDI1)监控处理器代码活动,如果因为代码执行错误,WDI1未在规定的时间(1.6s或102ms)内选通,ADP5042的/RESET引脚就会变为低电平并保持规定的时间(24ms或160ms),使处理器进入复位状态,并在处理器复位后离开复位状态。第二看门狗定时器(WDI2)同样监控处理器代码活动,但时间长得多(32分钟、64分钟或128分钟)。如果在规定的时间内WDI2未选通,则说明发生了WDI1(处理器复位)无法解决的故障,因而该多路输出稳压器需要进行完整的周期供电。如果多路输出稳压器发生WDI2超时,则三个输出电压进行周期供电,从而启动系统的完整硬件周期供电,而无需技术人员对系统执行周期供电。由于ADP5042能够对系统进行远程周期供电,因此系统可用性更高,并且可以节省让技术人员手动为系统周期供电的成本。利用WSTAT引脚可以确定系统复位的原因,看看到底是WDI1(处理器复位)还是WDI2(完整硬件周期供电)引起处理器复位。

4: 低噪声解决方案

开关降压稳压器上的专用MODE引脚可以通过微处理器GPIO端口方便地控制,迫使开关稳压器以恒定PWM模式工作。在轻负载下,开关稳压器以突发模式工作会产生宽带噪声,如果受电电路(收发器、ADC、音频)对宽带噪声敏感,那么这种控制就是必需的。集成到这些多路输出稳压器中的LDO具有1.7 V至5.5 V的输入电压范围,配合一个降压稳压器使用时,低输入电压使得LDO能够提供极高效率的低噪声输出。例如,降压稳压器可以用作前置稳压器,实现5V输入到1.8V输出的高效率压降,然后将此1.8V电压施加于LDO的输入端,以提供极低噪声的1.2V输出电压,从而以非常高的效率从5V初始输入为极敏感的模拟电路供电。集成LDO具有高PSRR(即便Vin-Vout裕量较低)和低内部噪声,稳压器之间的串扰已被降至最小。为噪声敏感型电路供电时,所有这些特性都很重要。

电源设计必杀技:TI公司最系统的电源设计培训资料

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于分立元件的电池自动恒流充电电路设计

下一篇:为多核处理器提升电源效率