- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

设计一款超低噪声的S频段放大器

工程师们一般都把RF低噪声放大器设计视为畏途。要在稳定高增益情况下获得低噪声系数可能极具挑战性,甚至使人畏惧。不过,采用最新的GaAs(砷化镓)异质结FET,可以设计出有高稳定增益和低于1dB噪声系数的放大器(参考文献1)。本设计就讲述了一个有0.77dB噪声系数的低噪声放大器。

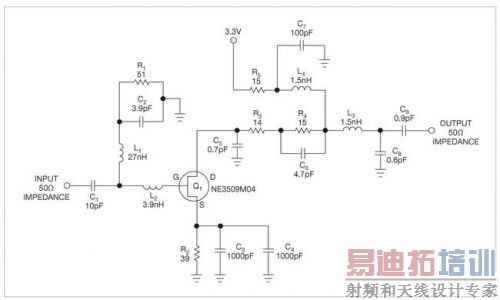

制造商们一般会给出低噪声放大器的输入/输出匹配、噪声系数、增益、稳定性、1dB压缩点、二阶和三阶互调分量、带外抑制,以及反向隔离等指标。这些参数中,很多是互相依赖的,因此在有限的时间内要满足所有这些设计标准,工作会很复杂(参考文献2和3)。图1给出了一种灵活的放大器结构,它能满足所有这些设计标准。

图1,可以用GaAs异质结FET设计一款低噪声S频段RF放大器。

设计用Microwave的Office AWR建立并仿真。NEC的NE3509M04 GaAsHJFET(异质结场效应管)用作低噪声高增益晶体管。电抗匹配的放大器输入采用了数据表给出的最佳反射系数值,可提供低噪声和高增益。FET设计常用的方法包括有源偏置与自举,可防止漏源电流随温度而变化。而这种设计的结果是一种高性价比的小型自偏置电路,没有给电路增加复杂性。晶体管的偏置点是2V的漏源电压,漏极电流为15mA,此时晶体管提供约16.5dB的可接受RF增益。

电路的另一个设计目标是低噪声放大器的无条件稳定性。晶体管的内部反馈与带外频率上的过高增益都是这种电路不稳定的主要原因。设计采用了制造商的S参数来分析稳定性问题。尽管L1、R1和C2支路保持了对HJFET的低频dc-视频频率稳定性,但它们的组合对S频段下的工作表现为开路,有助于实现晶体管的噪声匹配。C5、C8、C9和L3主要实现了输出的电抗匹配以及更高的频率稳定性。电容C6 主要用于短接漏极线路中的偏置电阻,而不会限制最大稳定增益。偏置线路上的R3 维持了放大器的稳定性。并联电容C5 也将漏极的高频分量和谐波引入大地。栅极端的接地过孔产生了一个小的电感,用于放大器的电感再生,从而获得良好的噪声匹配。

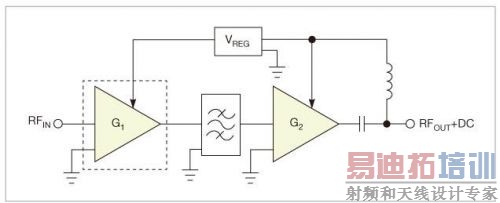

图2,两级放大器之间的带通滤波器用于抑制带外频率。

图2显示了一个两级放大器,两级之间有一个带通滤波器。开发人员将设计做在一个标准的四层62mil FR4基板上。与高性价比的双层设计不同,这个设计采用附加层做直流走线,以及将无源天线与高增益放大器级隔离开来,以防任何可能的信号泄漏和反馈造成放大器的不稳定。最后的结果实现了在室温下的0.77dB噪声系数、28.5dB增益、1dB压缩时的-16dBm输入功率,以及-5.8dBm的三阶互调点。输出电压驻波比为1.3:1。增加漏极偏置电流就可以提高三阶互调水平,但代价是增加噪声系数。

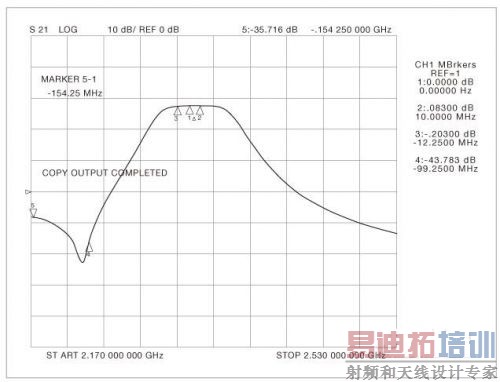

图3,测得的放大器响应曲线中心频率为2.332GHz。

[p]图3 是测量结果, 是相对于2.332GHz中心频率,-40dBm输入功率和-11.5dB输出功率的增益性能。因有两级放大器之间的带通滤波器协助,因此实现了带外抑制。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于分类算法的双三相感应电机SVPWM

下一篇:采用X2Y技术的DC-DC转换器