- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

安森美半导体电路保护及滤波技术透视暨智能手机典型应用示例-消费电子

录入:edatop.com 点击:

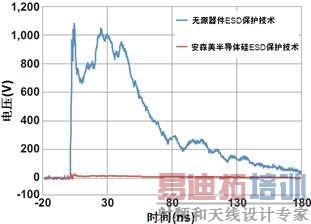

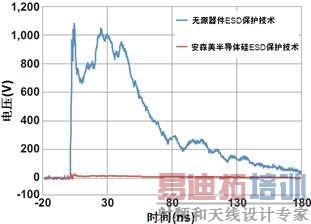

静电放电(ESD)保护及电磁干扰(EMI)正在成为所有电气设备越来越重要的考虑因素。消费者要求智能手机等便携/无线设备具有更多功能特性及采用纤薄型工业设计,这就要求设计人员要求更加注重小外形封装之中的ESD及EMI性能。本文将分析电路保护要求,比较不同的电路保护技术及滤波技术,介绍安森美半导体应用于典型电路保护及滤波应用的产品,帮助设计工程师设计出更可靠的便携及消费类产品。 关键芯片组外部ESD保护要求业界正在采用最先进的技术制造先进的系统级芯片(SoC)。设计人员为了优化功能及芯片尺寸,正在持续不断地减小其芯片设计的最小特征尺寸。但相应的代价是:随着特征尺寸减小,器件更易于遭受ESD损伤。当今的集成电路(IC)给保护功能所留下的设计窗口已经减小。ESD保护必须在安全过压及过流区工作。随着业界趋向以更小几何尺寸和更低电压制造更先进IC,IC的安全工作区也在缩小。 有效ESD保护的关键是限制ESD事件期间的电压,令其处于给定芯片组的安全电压窗口内。ESD保护产品实现有效ESD保护的方式,是在ESD事件期间提供接地的低阻抗电流路径;用于新集成电路的保护产品需要更低的动态阻抗(Rdyn),从而避免可能导致损伤的电压。 由于给保护功能所留的设计窗口减小,选择具有低动态阻抗的ESD保护产品变得更加重要,以此确保钳位电压不超过新芯片组的安全保护窗口。因此,ESD保护产品供应商必须提供保护产品有效性的信息,而非仅是保护产品自身的存续等级。 硅ESD保护技术与无源ESD保护技术比较安森美半导体的保护及滤波方案基于先进的硅工艺。相比较而言,其它几种低成本无源方案结合使用了陶瓷、铁氧体及多层压敏电阻(MLV)材料。这些类型器件传统上ESD钳位性能较弱。在某些无源方案中,下游器件会遭受的电压比安森美半导体硅方案高出一个或多个数量级,下图中的ESD屏幕截图所示,其中比较了安森美半导体硅方案与竞争技术在8 kV ESD应力条件下的表现。竞争技术的导通电压如此之高,以致于它根本不会激活,所测的电压只不过是在50 Ω测量电路上的电压降。其它一些更老技术甚至在经历较少几次ESD冲击后性能就会下降。由于材料成分原因,某些无源器件往往在不同温度条件下的性能表现不一致,因此在恶劣环境下的可靠性更低。  图1:安森美半导体硅器件与无源竞争器件以50 Ω系统在8 kV测得的ESD钳位性能比较 消除信号完整性问题的PicoGuard XS ESD保护技术传统ESD保护产品贴装在信号走线与地之间,在信号路径上不会产生中断。为了将高速数据线路的信号完整性下降问题减至最轻,电容必须最小化,如图2所示。

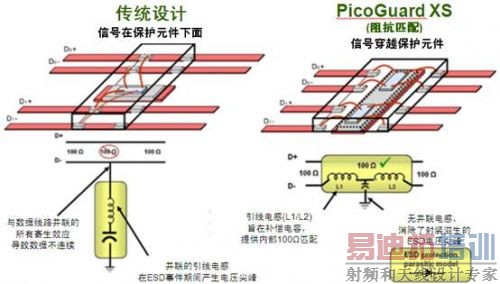

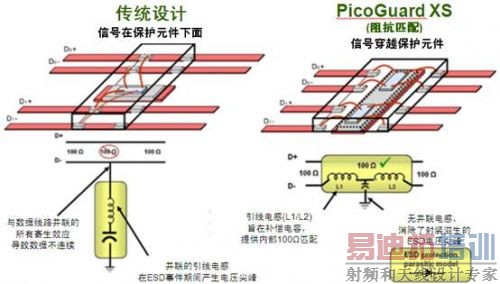

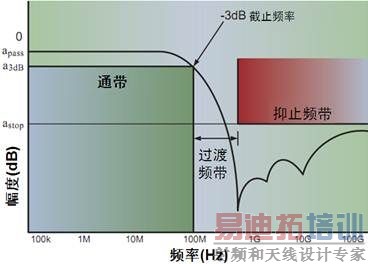

图1:安森美半导体硅器件与无源竞争器件以50 Ω系统在8 kV测得的ESD钳位性能比较 消除信号完整性问题的PicoGuard XS ESD保护技术传统ESD保护产品贴装在信号走线与地之间,在信号路径上不会产生中断。为了将高速数据线路的信号完整性下降问题减至最轻,电容必须最小化,如图2所示。  图2:传统ESD保护设计方法与PicoGuard XS比较。 安森美半导体优异的PicoGuard XS技术通过使信号路径穿越保护产品,提供阻抗匹配的信号路径,故而消除了信号完整性问题。PicoGuard XS技术平衡了封装串联电感与保护二极管电容,提供极佳的100 Ω信号路径,与PCB上走线的阻抗匹配。此外,这种设计事实上省下了与保护二极管串联的电感,因而将ESD事件起始阶段的封装引致电压尖峰减至最小。 电磁干扰(EMI)滤波:单端滤波器与共模滤波器(CMF)安森美半导体提供两种类型的EMI滤波器,分别是单端滤波器及共模滤波器。单端滤波器采用不同阵列配置来制造,用于并行接口。这些滤波器包括用于音频等低速信号的通用电阻-电容(RC)型滤波器和用于较高速度及功率敏感型接口的电感-电容(LC)型滤波器。低通滤波器提供700 MHz至最高6 GHz范围的截止频率。截止频率如图8所示的S21图所示。单端滤波器无法满足高速差分接口的需求。差分接口拥有固有的噪声抑制,但它们不能完全免受可能存在

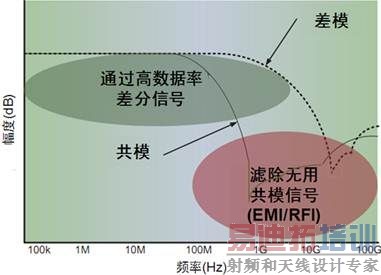

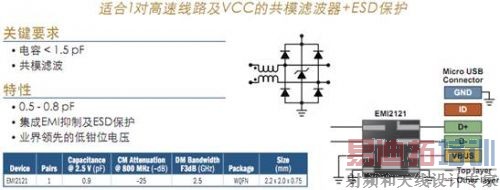

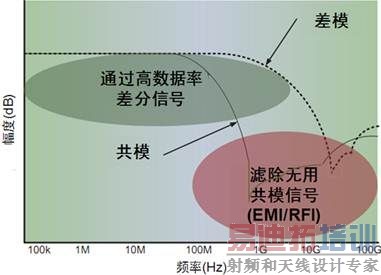

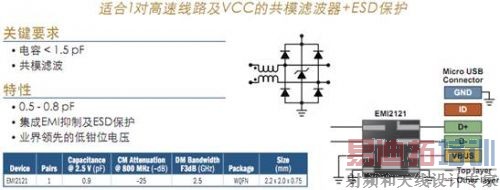

图2:传统ESD保护设计方法与PicoGuard XS比较。 安森美半导体优异的PicoGuard XS技术通过使信号路径穿越保护产品,提供阻抗匹配的信号路径,故而消除了信号完整性问题。PicoGuard XS技术平衡了封装串联电感与保护二极管电容,提供极佳的100 Ω信号路径,与PCB上走线的阻抗匹配。此外,这种设计事实上省下了与保护二极管串联的电感,因而将ESD事件起始阶段的封装引致电压尖峰减至最小。 电磁干扰(EMI)滤波:单端滤波器与共模滤波器(CMF)安森美半导体提供两种类型的EMI滤波器,分别是单端滤波器及共模滤波器。单端滤波器采用不同阵列配置来制造,用于并行接口。这些滤波器包括用于音频等低速信号的通用电阻-电容(RC)型滤波器和用于较高速度及功率敏感型接口的电感-电容(LC)型滤波器。低通滤波器提供700 MHz至最高6 GHz范围的截止频率。截止频率如图8所示的S21图所示。单端滤波器无法满足高速差分接口的需求。差分接口拥有固有的噪声抑制,但它们不能完全免受可能存在于来自外部源的共模噪声的影响,亦不能防止接口信号辐射至系统其它元件。 图4:共模滤波器特性 智能手机等便携及消费产品电路保护及滤波应用示例1) USB 2.0接口滤波及保护安森美半导体为USB 2.0接口提供适合1对高速线路及VCC的低电容ESD保护方案(如NUP4114UPX、NUP4114UCL、NUP4114H、ESD7L5.0及ESD9L5.0),还提供适合1对高速线路及VCC的共模滤波器及ESD保护方案(EMI2121),用于智能手机、数码相机等便携/无线产品中的USB 2.0接口。

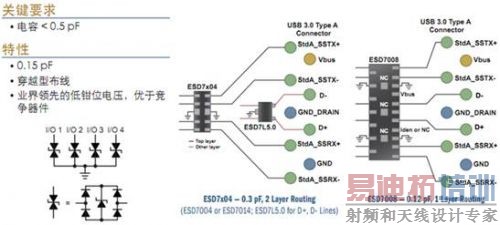

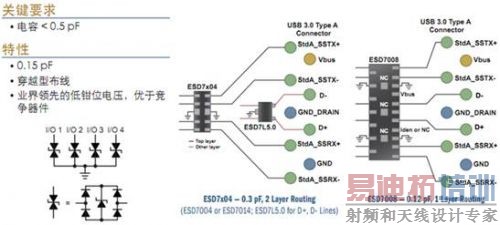

图4:共模滤波器特性 智能手机等便携及消费产品电路保护及滤波应用示例1) USB 2.0接口滤波及保护安森美半导体为USB 2.0接口提供适合1对高速线路及VCC的低电容ESD保护方案(如NUP4114UPX、NUP4114UCL、NUP4114H、ESD7L5.0及ESD9L5.0),还提供适合1对高速线路及VCC的共模滤波器及ESD保护方案(EMI2121),用于智能手机、数码相机等便携/无线产品中的USB 2.0接口。  2) USB 3.0接口ESD保护智能手机、平板电脑等便携/无线设备的功能越来越多、性能越来越强、存储容量越来越大,与外界的数据通信需求也越来越高。USB标准制定组织宣布,速度是USB 2.0十倍的USB 3.0端口有望在2012年度或2013年初支持智能手机和平板电脑设备。 安森美半导体为USB 3.0接口提供一系列方案,用于为2对超高速线路、1对高速线路及VCC提供低电容ESD保护。这些方案包括ESD7008(保护8条线路、0.12 pF电容、5.5 x 1.5 mm UDFN-18封装)、ESD7104(保护4条线路、0.3 pF电容、2.5 x 1.0 mm UDFN-10封装)、ESD7004(保护4条线路、0.4 pF电容、2.5 x 1.0 mm UDFN-10封装)及ESD7L(保护2条线路、0.5 pF电容、1.2 x 1.2 mm SOT-723封装)。

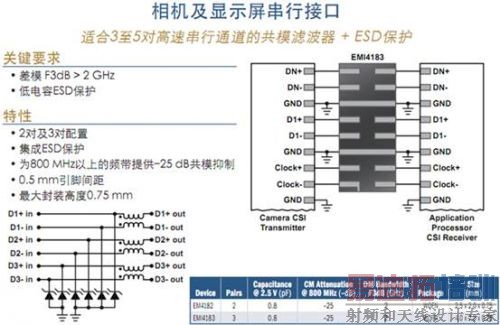

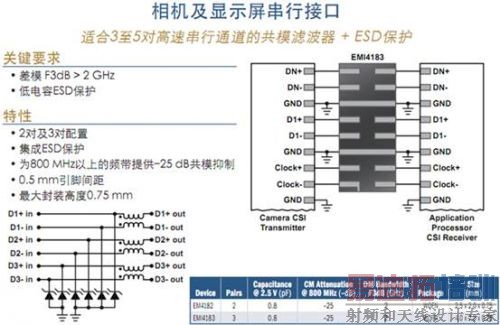

2) USB 3.0接口ESD保护智能手机、平板电脑等便携/无线设备的功能越来越多、性能越来越强、存储容量越来越大,与外界的数据通信需求也越来越高。USB标准制定组织宣布,速度是USB 2.0十倍的USB 3.0端口有望在2012年度或2013年初支持智能手机和平板电脑设备。 安森美半导体为USB 3.0接口提供一系列方案,用于为2对超高速线路、1对高速线路及VCC提供低电容ESD保护。这些方案包括ESD7008(保护8条线路、0.12 pF电容、5.5 x 1.5 mm UDFN-18封装)、ESD7104(保护4条线路、0.3 pF电容、2.5 x 1.0 mm UDFN-10封装)、ESD7004(保护4条线路、0.4 pF电容、2.5 x 1.0 mm UDFN-10封装)及ESD7L(保护2条线路、0.5 pF电容、1.2 x 1.2 mm SOT-723封装)。  3) 相机及显示屏并行接口及串行接口保护安森美半导体为相机及显示屏并行接口和串行接口提供保护方案。其中,适合4至12条线路并行接口的低通滤波器及ESD保护方案包括EMI720x系列、EMI940x系列、CM1693系列及CM1457系列;适合3至5对高速串行通道的共模滤波器及ESD保护方案包括EMI4182及EMI4183等。这些产品可用于智能手机和数码相机等应用。

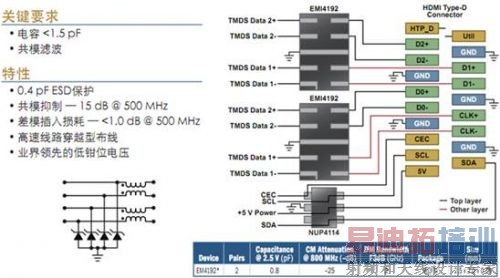

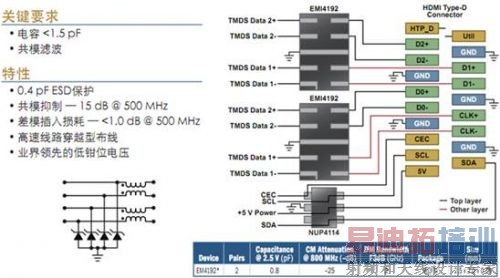

3) 相机及显示屏并行接口及串行接口保护安森美半导体为相机及显示屏并行接口和串行接口提供保护方案。其中,适合4至12条线路并行接口的低通滤波器及ESD保护方案包括EMI720x系列、EMI940x系列、CM1693系列及CM1457系列;适合3至5对高速串行通道的共模滤波器及ESD保护方案包括EMI4182及EMI4183等。这些产品可用于智能手机和数码相机等应用。  4) 便携产品HDMI端口滤波及保护一些智能手机及平板电脑设计已经开始支持HDMI端口,配合用户以更高速率传输音视频数据的需求。安森美半导体提供适合于便携产品HDMI端口滤波及保护的低阻抗共模滤波器(CMF),适合为4对高速线路及最多6条额外接口线路提供低电容ESD保护及共模滤波。

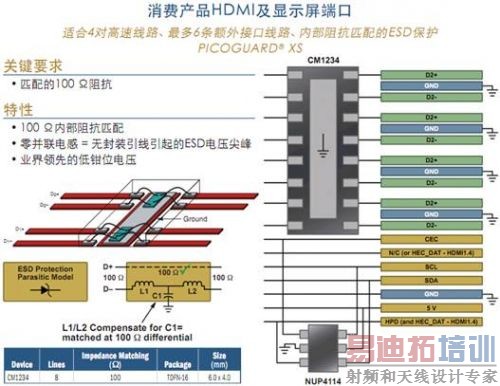

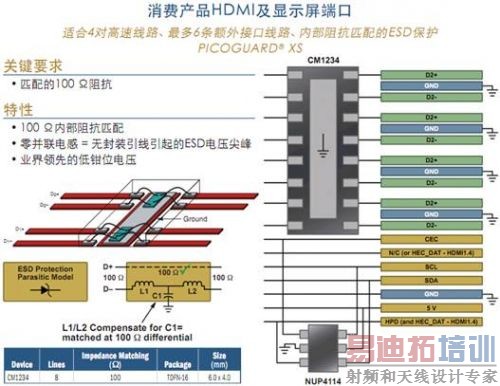

4) 便携产品HDMI端口滤波及保护一些智能手机及平板电脑设计已经开始支持HDMI端口,配合用户以更高速率传输音视频数据的需求。安森美半导体提供适合于便携产品HDMI端口滤波及保护的低阻抗共模滤波器(CMF),适合为4对高速线路及最多6条额外接口线路提供低电容ESD保护及共模滤波。  5) 消费类产品HDMI及显示屏端口保护安森美半导体为消费类产品HDMI及显示屏端口提供不同类型的滤波及保护方案,包括适合4对高速线路、最多6条额外线路的低电容ESD保护及共模滤波方案(EMI4182),适合4对高速线路、最多6条额外线路的低电容ESD保护方案(ESD7004, MG2040),以及适合4对高速线路、最多6条额外线路、内部阻抗匹配的ESD保护PicoGuard XS。

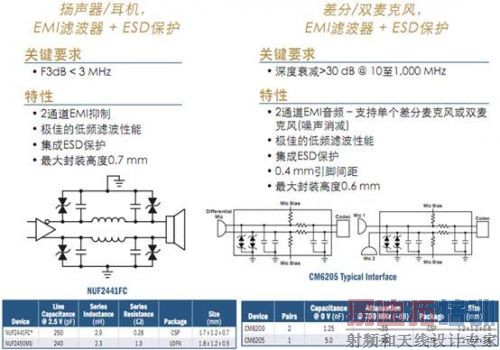

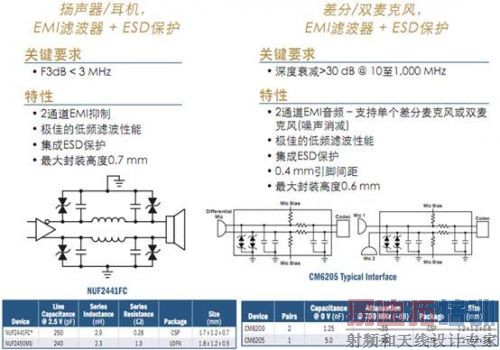

5) 消费类产品HDMI及显示屏端口保护安森美半导体为消费类产品HDMI及显示屏端口提供不同类型的滤波及保护方案,包括适合4对高速线路、最多6条额外线路的低电容ESD保护及共模滤波方案(EMI4182),适合4对高速线路、最多6条额外线路的低电容ESD保护方案(ESD7004, MG2040),以及适合4对高速线路、最多6条额外线路、内部阻抗匹配的ESD保护PicoGuard XS。  6) 智能手机等应用的音频滤波及保护安森美半导体为扬声器/耳机、差分麦克风、双麦克风等应用提供相应的EMI滤波器及ESD保护方案,包括应用于扬声器/耳机滤波及保护的NUF2441FC和NUF2450MU,以及用于差分/双麦克风滤波及保护的CM6200和CM6205等。

6) 智能手机等应用的音频滤波及保护安森美半导体为扬声器/耳机、差分麦克风、双麦克风等应用提供相应的EMI滤波器及ESD保护方案,包括应用于扬声器/耳机滤波及保护的NUF2441FC和NUF2450MU,以及用于差分/双麦克风滤波及保护的CM6200和CM6205等。  总结:设计人员需要为智能手机、平板电脑、数码相机等便携及无线、消费等应用选择适合的电路保护及滤波方案。安森美半导体身为应用于高能效电子产品的首要高性能硅方案供应商,致力提供对目标应用具有最佳技术和经济价值的保护及滤波方案。本文分析了电路保护的技术趋势及EMI滤技术比较,并结合具体应用示例,介绍安森美半导体相应产品,帮助设计人员选择恰当的电路保护及滤波方案。 供稿:安森美半导体 参考资料:1、安森美半导体电路保护应用网页,www.onsemi.cn/PowerSolutions/content.do

id=160072、《电路保护方案》小册子,www.onsemi.cn/pub/Collateral/BRD8080CN.rev1.pdf3、"Circuit Protection Solutions Brochure", www.onsemi.cn/pub/Collateral/BRD8080-D.PDF

总结:设计人员需要为智能手机、平板电脑、数码相机等便携及无线、消费等应用选择适合的电路保护及滤波方案。安森美半导体身为应用于高能效电子产品的首要高性能硅方案供应商,致力提供对目标应用具有最佳技术和经济价值的保护及滤波方案。本文分析了电路保护的技术趋势及EMI滤技术比较,并结合具体应用示例,介绍安森美半导体相应产品,帮助设计人员选择恰当的电路保护及滤波方案。 供稿:安森美半导体 参考资料:1、安森美半导体电路保护应用网页,www.onsemi.cn/PowerSolutions/content.do

id=160072、《电路保护方案》小册子,www.onsemi.cn/pub/Collateral/BRD8080CN.rev1.pdf3、"Circuit Protection Solutions Brochure", www.onsemi.cn/pub/Collateral/BRD8080-D.PDF

图1:安森美半导体硅器件与无源竞争器件以50 Ω系统在8 kV测得的ESD钳位性能比较 消除信号完整性问题的PicoGuard XS ESD保护技术传统ESD保护产品贴装在信号走线与地之间,在信号路径上不会产生中断。为了将高速数据线路的信号完整性下降问题减至最轻,电容必须最小化,如图2所示。

图1:安森美半导体硅器件与无源竞争器件以50 Ω系统在8 kV测得的ESD钳位性能比较 消除信号完整性问题的PicoGuard XS ESD保护技术传统ESD保护产品贴装在信号走线与地之间,在信号路径上不会产生中断。为了将高速数据线路的信号完整性下降问题减至最轻,电容必须最小化,如图2所示。  图2:传统ESD保护设计方法与PicoGuard XS比较。 安森美半导体优异的PicoGuard XS技术通过使信号路径穿越保护产品,提供阻抗匹配的信号路径,故而消除了信号完整性问题。PicoGuard XS技术平衡了封装串联电感与保护二极管电容,提供极佳的100 Ω信号路径,与PCB上走线的阻抗匹配。此外,这种设计事实上省下了与保护二极管串联的电感,因而将ESD事件起始阶段的封装引致电压尖峰减至最小。 电磁干扰(EMI)滤波:单端滤波器与共模滤波器(CMF)安森美半导体提供两种类型的EMI滤波器,分别是单端滤波器及共模滤波器。单端滤波器采用不同阵列配置来制造,用于并行接口。这些滤波器包括用于音频等低速信号的通用电阻-电容(RC)型滤波器和用于较高速度及功率敏感型接口的电感-电容(LC)型滤波器。低通滤波器提供700 MHz至最高6 GHz范围的截止频率。截止频率如图8所示的S21图所示。单端滤波器无法满足高速差分接口的需求。差分接口拥有固有的噪声抑制,但它们不能完全免受可能存在

图2:传统ESD保护设计方法与PicoGuard XS比较。 安森美半导体优异的PicoGuard XS技术通过使信号路径穿越保护产品,提供阻抗匹配的信号路径,故而消除了信号完整性问题。PicoGuard XS技术平衡了封装串联电感与保护二极管电容,提供极佳的100 Ω信号路径,与PCB上走线的阻抗匹配。此外,这种设计事实上省下了与保护二极管串联的电感,因而将ESD事件起始阶段的封装引致电压尖峰减至最小。 电磁干扰(EMI)滤波:单端滤波器与共模滤波器(CMF)安森美半导体提供两种类型的EMI滤波器,分别是单端滤波器及共模滤波器。单端滤波器采用不同阵列配置来制造,用于并行接口。这些滤波器包括用于音频等低速信号的通用电阻-电容(RC)型滤波器和用于较高速度及功率敏感型接口的电感-电容(LC)型滤波器。低通滤波器提供700 MHz至最高6 GHz范围的截止频率。截止频率如图8所示的S21图所示。单端滤波器无法满足高速差分接口的需求。差分接口拥有固有的噪声抑制,但它们不能完全免受可能存在

图3:单端低通滤波器特性

图4:共模滤波器特性 智能手机等便携及消费产品电路保护及滤波应用示例1) USB 2.0接口滤波及保护安森美半导体为USB 2.0接口提供适合1对高速线路及VCC的低电容ESD保护方案(如NUP4114UPX、NUP4114UCL、NUP4114H、ESD7L5.0及ESD9L5.0),还提供适合1对高速线路及VCC的共模滤波器及ESD保护方案(EMI2121),用于智能手机、数码相机等便携/无线产品中的USB 2.0接口。

图4:共模滤波器特性 智能手机等便携及消费产品电路保护及滤波应用示例1) USB 2.0接口滤波及保护安森美半导体为USB 2.0接口提供适合1对高速线路及VCC的低电容ESD保护方案(如NUP4114UPX、NUP4114UCL、NUP4114H、ESD7L5.0及ESD9L5.0),还提供适合1对高速线路及VCC的共模滤波器及ESD保护方案(EMI2121),用于智能手机、数码相机等便携/无线产品中的USB 2.0接口。  2) USB 3.0接口ESD保护智能手机、平板电脑等便携/无线设备的功能越来越多、性能越来越强、存储容量越来越大,与外界的数据通信需求也越来越高。USB标准制定组织宣布,速度是USB 2.0十倍的USB 3.0端口有望在2012年度或2013年初支持智能手机和平板电脑设备。 安森美半导体为USB 3.0接口提供一系列方案,用于为2对超高速线路、1对高速线路及VCC提供低电容ESD保护。这些方案包括ESD7008(保护8条线路、0.12 pF电容、5.5 x 1.5 mm UDFN-18封装)、ESD7104(保护4条线路、0.3 pF电容、2.5 x 1.0 mm UDFN-10封装)、ESD7004(保护4条线路、0.4 pF电容、2.5 x 1.0 mm UDFN-10封装)及ESD7L(保护2条线路、0.5 pF电容、1.2 x 1.2 mm SOT-723封装)。

2) USB 3.0接口ESD保护智能手机、平板电脑等便携/无线设备的功能越来越多、性能越来越强、存储容量越来越大,与外界的数据通信需求也越来越高。USB标准制定组织宣布,速度是USB 2.0十倍的USB 3.0端口有望在2012年度或2013年初支持智能手机和平板电脑设备。 安森美半导体为USB 3.0接口提供一系列方案,用于为2对超高速线路、1对高速线路及VCC提供低电容ESD保护。这些方案包括ESD7008(保护8条线路、0.12 pF电容、5.5 x 1.5 mm UDFN-18封装)、ESD7104(保护4条线路、0.3 pF电容、2.5 x 1.0 mm UDFN-10封装)、ESD7004(保护4条线路、0.4 pF电容、2.5 x 1.0 mm UDFN-10封装)及ESD7L(保护2条线路、0.5 pF电容、1.2 x 1.2 mm SOT-723封装)。  3) 相机及显示屏并行接口及串行接口保护安森美半导体为相机及显示屏并行接口和串行接口提供保护方案。其中,适合4至12条线路并行接口的低通滤波器及ESD保护方案包括EMI720x系列、EMI940x系列、CM1693系列及CM1457系列;适合3至5对高速串行通道的共模滤波器及ESD保护方案包括EMI4182及EMI4183等。这些产品可用于智能手机和数码相机等应用。

3) 相机及显示屏并行接口及串行接口保护安森美半导体为相机及显示屏并行接口和串行接口提供保护方案。其中,适合4至12条线路并行接口的低通滤波器及ESD保护方案包括EMI720x系列、EMI940x系列、CM1693系列及CM1457系列;适合3至5对高速串行通道的共模滤波器及ESD保护方案包括EMI4182及EMI4183等。这些产品可用于智能手机和数码相机等应用。  4) 便携产品HDMI端口滤波及保护一些智能手机及平板电脑设计已经开始支持HDMI端口,配合用户以更高速率传输音视频数据的需求。安森美半导体提供适合于便携产品HDMI端口滤波及保护的低阻抗共模滤波器(CMF),适合为4对高速线路及最多6条额外接口线路提供低电容ESD保护及共模滤波。

4) 便携产品HDMI端口滤波及保护一些智能手机及平板电脑设计已经开始支持HDMI端口,配合用户以更高速率传输音视频数据的需求。安森美半导体提供适合于便携产品HDMI端口滤波及保护的低阻抗共模滤波器(CMF),适合为4对高速线路及最多6条额外接口线路提供低电容ESD保护及共模滤波。  5) 消费类产品HDMI及显示屏端口保护安森美半导体为消费类产品HDMI及显示屏端口提供不同类型的滤波及保护方案,包括适合4对高速线路、最多6条额外线路的低电容ESD保护及共模滤波方案(EMI4182),适合4对高速线路、最多6条额外线路的低电容ESD保护方案(ESD7004, MG2040),以及适合4对高速线路、最多6条额外线路、内部阻抗匹配的ESD保护PicoGuard XS。

5) 消费类产品HDMI及显示屏端口保护安森美半导体为消费类产品HDMI及显示屏端口提供不同类型的滤波及保护方案,包括适合4对高速线路、最多6条额外线路的低电容ESD保护及共模滤波方案(EMI4182),适合4对高速线路、最多6条额外线路的低电容ESD保护方案(ESD7004, MG2040),以及适合4对高速线路、最多6条额外线路、内部阻抗匹配的ESD保护PicoGuard XS。  6) 智能手机等应用的音频滤波及保护安森美半导体为扬声器/耳机、差分麦克风、双麦克风等应用提供相应的EMI滤波器及ESD保护方案,包括应用于扬声器/耳机滤波及保护的NUF2441FC和NUF2450MU,以及用于差分/双麦克风滤波及保护的CM6200和CM6205等。

6) 智能手机等应用的音频滤波及保护安森美半导体为扬声器/耳机、差分麦克风、双麦克风等应用提供相应的EMI滤波器及ESD保护方案,包括应用于扬声器/耳机滤波及保护的NUF2441FC和NUF2450MU,以及用于差分/双麦克风滤波及保护的CM6200和CM6205等。  总结:设计人员需要为智能手机、平板电脑、数码相机等便携及无线、消费等应用选择适合的电路保护及滤波方案。安森美半导体身为应用于高能效电子产品的首要高性能硅方案供应商,致力提供对目标应用具有最佳技术和经济价值的保护及滤波方案。本文分析了电路保护的技术趋势及EMI滤技术比较,并结合具体应用示例,介绍安森美半导体相应产品,帮助设计人员选择恰当的电路保护及滤波方案。 供稿:安森美半导体 参考资料:1、安森美半导体电路保护应用网页,www.onsemi.cn/PowerSolutions/content.do

id=160072、《电路保护方案》小册子,www.onsemi.cn/pub/Collateral/BRD8080CN.rev1.pdf3、"Circuit Protection Solutions Brochure", www.onsemi.cn/pub/Collateral/BRD8080-D.PDF

总结:设计人员需要为智能手机、平板电脑、数码相机等便携及无线、消费等应用选择适合的电路保护及滤波方案。安森美半导体身为应用于高能效电子产品的首要高性能硅方案供应商,致力提供对目标应用具有最佳技术和经济价值的保护及滤波方案。本文分析了电路保护的技术趋势及EMI滤技术比较,并结合具体应用示例,介绍安森美半导体相应产品,帮助设计人员选择恰当的电路保护及滤波方案。 供稿:安森美半导体 参考资料:1、安森美半导体电路保护应用网页,www.onsemi.cn/PowerSolutions/content.do

id=160072、《电路保护方案》小册子,www.onsemi.cn/pub/Collateral/BRD8080CN.rev1.pdf3、"Circuit Protection Solutions Brochure", www.onsemi.cn/pub/Collateral/BRD8080-D.PDF立即加入模拟与电源技术社区

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:新兴电池技术正成为能源行业焦点

下一篇:纳米线技术使光伏电池吸收光波长范围增大

射频和天线工程师培训课程详情>>