- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

LTC4366高压浪涌抑制器应用深入讲解(独家收录)

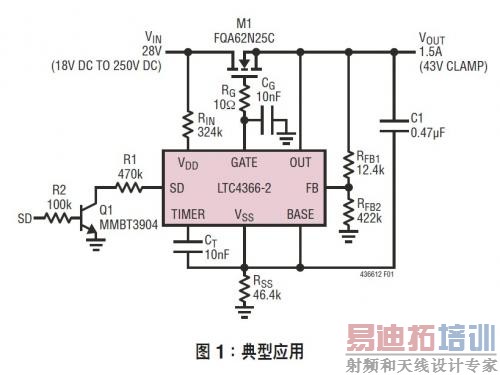

LTC4366浪涌抑制器可保护负载免遭高压瞬变的损坏。通过控制一个外部N沟道MOSFET的栅极,LTC4366可在过压瞬变过程中调节输出。在MOSFET两端承载过压的情况下,负载可以保持运作状态。在返回线路中布设一个电阻器可隔离LTC4366,并允许其随电源向上浮动;因此,输出电压的上限仅取决于高值电阻器的可用性和MOSFET的额定规格。

一个可调的过压定时器能在浪涌期间避免损坏MOSFET,而一个附加的9s定时器则为MOSFET提供了冷却周期。停机引脚负责在停机期间将静态电流减小至14A以下。在一个故障发生之后,LTC4366-1将锁断,而LTC4366-2则将执行自动重试操作。

应用信息

LTC4366的典型应用是一种需要过压保护的系统,该系统可在过压瞬变期间安全地向负载分配功率。下面讨论外部组件的选择。

双并联稳压器

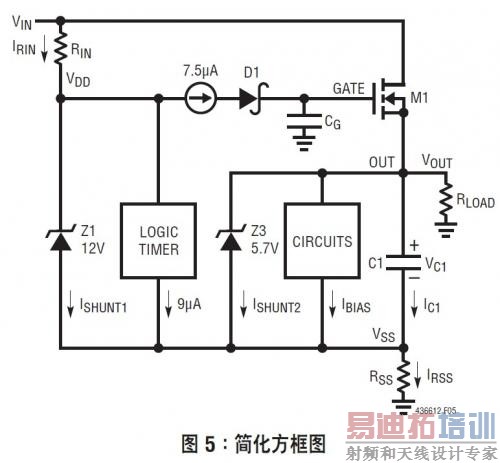

LTC4366将两个并联稳压器与外部降压电阻器RSS和RIN配合使用,以在VDD和OUT引脚上产生内部电源轨。这些并联调节电源轨可提供针对电路输入电压无限度的高电压瞬变之过压保护,而与LTC4366内部电路的额定电压无关。

在启动的起点、停机期间或过压故障之后,GATE引脚电压被箝位至OUT引脚,由此关断MOSFET。这允许利用输出负载和RSS将VSS和OUT引脚拉至地电位。在这种情况下,VDD引脚电压利用一个12V并联稳压器箝位至VSS。然后,把(完整电源电压–12V)施加至负责设定分路电流RIN电阻器上。分路电流可以高达10mA,这比VDD引9A的典型静态电流高出了几个数量级。

在正常操作模式中,OUT电压等于输入电源电压。当C1满充电时,IC1在这一点上为零。在这种情况下,利用一个5.7V并联稳压器对OUT和VSS引脚之间的电压进行箝位。(输入电源电压–5.7V)被加至RSS上。RSS电流被分为三块:5.7V分路电流、OUT和VSS之间的偏置电流以及最终的RIN电流。5.7V分路电流可高达10mA,大大超过了典型的OUT(160A)偏置电流。

开机时序

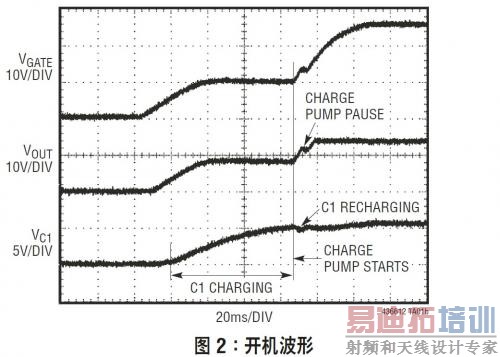

在输入电源上升之后,VDD和VSS引脚之间的电压并联将调节至12V。接着,在内部生成的电源VCC产生一个30s的上电复位脉冲,该脉冲将进行故障锁存器的清零以及内部锁存器的初始化。然后,停机比较器确定SD引脚是否被外部拉至低电平,如果"是"则请求进入一种低偏置电流停机状态。否则将允许外部MOSFETM1开通。

从VDD引脚接入,通过7.5AGATE上拉电流源给MOSFET栅极上电,这种方法被称为"自举"的方法。当GATE电压达到VDD引脚电压(减去一个肖特基二极管压降)时,7.5A电流源将失去电压降并停止向GATE充电(图2中间的那个波形)。自举法依赖于在GATE引脚电压停止上升之后将C1充电至一个足够的电压。C1上的电压随后用作一个充电泵的电源,此充电泵负责把栅极充电至其终值(即:OUT+12V)。如果充电泵电流超过C1充电电流,则C1将放电。倘若C1电压低于4.35V以下,则充电泵将暂停操作,并让C1再充电。

如果电源开通并在大负载情况下不能把C1充起来,就有可能导致过热现像的发生,并随之造成器件受损。在栅极和输出斜坡上升时,MOSFET两端的压降为输入电源电压减去输出电压。如果电源电压低于C1充电所需的数值,则输出将无法斜坡上升超越(电源电压–MOSFET门限)。这种3V至5V的MOSFET压降以及高负载电流将导致没有任何保护或超时限值的功率耗散。

过压故障

LTC4366可避免输入电源上的过压到达负载。一般地,传输晶体管完全导通,并以非常小的电压降给负载供电。当输入电压增加时,OUT电压增加,直至其达到调节点(VREG)为止。从该点起,任何进一步的电压增加都将降落在MOSFET的两端。请注意,由于MOSFET仍然处于导通状态,因此LTC4366可在短时间过压过程中实现不间断的运作。

VREG调节点利用两个FB电阻器(RFB1和RFB2)来配置。调节放大器负责将FB引脚电压与(门限OUT引脚电压–1.23V)进行比较。在调节期间RFB1两端的压降为1.23V,而剩余的VREG电压则降落在RFB2的两端。当输出位于调节点时,起动一个定时器以避免MOSFET中产生过大的功率耗散。通常利用一个1.8A下拉电流将TIMER引脚保持于低电平。在调节期间,TIMER引脚以9A的电流进行充电。如果调节点的保持时间之长足以使TIMER引脚电压达到2.8V,则产生一个过压故障锁定。用于设定定时器电容器的公式为:

CT=3.5 t[nF/ms]

视版本的不同,该器件将冷却并自动起动(LTC4366-2),或者保持锁断状态直到SD引脚启动一个重起为止(LTC4366-1)。冷却时间通常为9秒,这提供了一个非常低的脉冲电源占空比。

在输入电源过压和满负载电流条件下启动确实会使MOSFET的功率耗散远远超过一般过压浪涌时的水平。在栅极和输出电压斜坡上升期间,部分电源电压(在满电流时)降落在MOSFET的两端。在启动之后,正常的过压浪涌发生在MOSFET关断之前。对于MOSFET的安全工作区(SOA)计算,"设计实例"部分仅考虑了正常的过压浪涌。在过压情况下启动将需要对SOA做更多的考虑。

停机

LTC4366具有一种低电流(<20A)停机状态,该状态可通过利用一个开关电阻把GATE和OUT引脚连接在一起以关断传输FET。在正常操作条件下,一个1.6A电流源将SD引脚上拉至VDD引脚电压。当不使用停机状态时,则SD引脚连接至VDD。SD引脚拉至低于(VDD引脚电压–1.5V)并持续超过700s的滤波器时间,将启动停机状态。该滤波器时间用于避免在瞬变期间发生不希望的停机启动。SD引脚通过二极管箝位在VSS–0.7V,这需要对下拉器件进行电流限(最大值为10mA)。限流的方法之一是连接一个与集电极开路下拉器件相串联的外部470k电阻器。启动外部下拉电流源将超过内部1.6A上拉电流源,并使得SD引脚电压越过停机门限。在一个过压故障之后,把器件置于停机状态可将清除故障,从而在LTC4366退出停机状态时立即恢复运作。

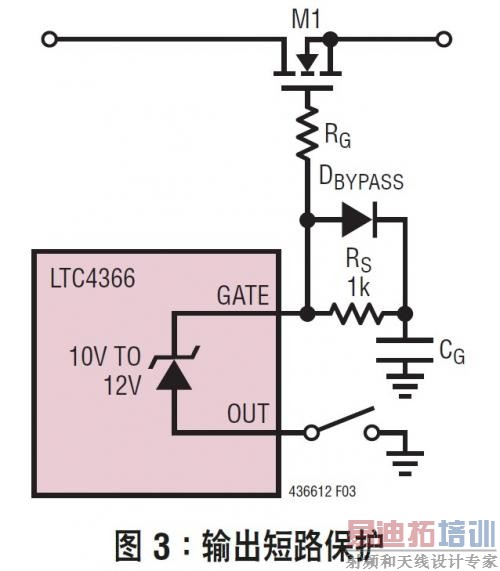

输出短路

输出的突然短路会导致栅极电容器CG过大的电流进入LTC4366GATE引脚。GATE引脚通过一个10V至12V的箝位电路连到OUT。如果OUT引脚电压被拉低而GATE引脚电压利用CG保持上拉,则箝位电路将由于在箝位电压被超过时试图对CG进行放电而受损。一种解决方案是增设一个与CG串联的1kRS电阻器和一个旁路二极管,如图3中所示。这个二极管使电容器能充当一条旁路,在电源过压期间吸收来自MOSFET漏极至栅极寄生电容器的能量。

电阻器额定功率

必须考虑图1中RSS电阻器的正确额定值。在过压期间,OUT引脚处于调节电压(VREG),因此RSS两端的电压为VREG–5.7V。一个小的最小电源电压要求RSS的阻值不能太大。于是,如果最小电源电压与调节电压之间的差异很大,则RSS可能需要使用一个大功率电阻器。在过压冷却周期中,(全电源电压–12V)会出现在RIN的两端。通常,RIN的阻值比RSS的阻值大几倍,因而降低了针对该电阻器的功率和尺寸要求。

推荐阅读:

1.LTC4366浪涌抑制器入门简介

摘要:一个可调的过压定时器能在浪涌期间避免损坏MOSFET,而一个附加的 9s 定时器则为MOSFET提供了冷却周期。停机引脚负责在停机期间将静态电流减小至14 A以下。在 一个故障发生之后,LTC4366-1将锁断,而LTC4366-2则将执行自动重试操作。

2.LTC4366浪涌抑制器工作原理详解

摘要:本 文描绘了三种操作状态:起动、运行和调节模式。先前的浪涌抑制器件由输入电源供电,因此所能承受 的浪涌电压被限制为器件输入引脚的击穿电压。如运行模 式和调节模式所示,该器件的大部分电路都由输出供电, 于是MOSFET将浪涌与器件的电源引脚隔离开来。这允许用于浪涌电压高至外MOSFET的击穿电压。

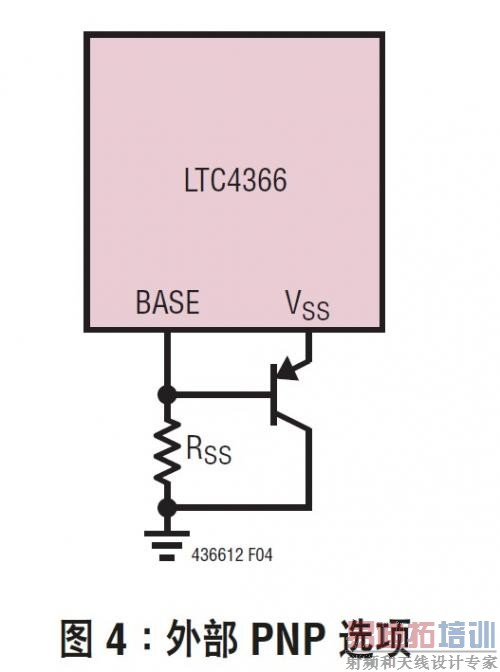

[p]外部PNP

在某些场合中,功率电阻器RSS的体积可能很庞大。可以用大阻值(具较低功率和尺寸)的RSS与一个PNP配合起来使用,如图4所示。除了由BASE引脚供应的0.8A电流之外,来自PNP的基极电流也必须流过RSS,这将限制最大RSS值。在有些场合,最小PNPβ低至35。当VSS电流为350A时,基极电流变为10A。可见,与未采用PNP的应用电路相比,这将允许使用一个大35(β)倍的RSS。

最小电源电压启动

当针对最小电源电压条件,行设计时,应选择合适的RSS和RIN以提供足够的电流,从而足以把C1充电至4.75V,这一点是很重要的。决定最小电源电压的参数包括:C1电压、MOSFET门限电压、一个串联肖特基二极管电压降、RSS和RIN的电阻、VDD引脚中的电流,最后还有来自VSS引脚的电流(见图5)。

VIN(MIN)=(IVDD•RIN)+VD+VTH+VC1+(IVSS•RSS)

以上参数使用"电特性"表获得:

VC1=VUVLO2=4.75V(UVLO2门限)

IVDD=IVDD(STHI)=9A(IVDD启动,栅极为高电平)IVSS=IVSS(AMP)=45A(采用调节放大器时的IVSS)

VD=0.58V

VIN(MIN)=(9A•RIN)+0.58V+VTH+4.75V+(45A•RSS)

当MOSFET栅极为高时,OUT引脚电压等于电源电压。这对最小电源电压施加了另一个限制条件,因为充电泵把VSS电流增加至160A。C1电压假定被箝位在5.7V。这些数值在"电特性"表中被规定为VZ(OUT)和IVSS(CP)(充电泵接通):

VIN(MIN)=VZ(OUT)+(IVSS(CP)•RSS) 或

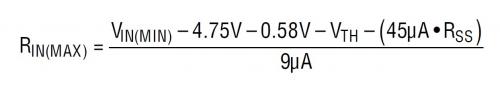

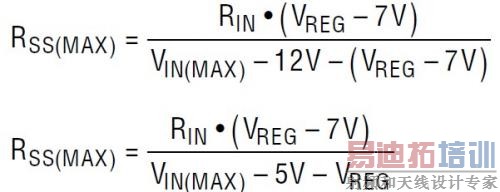

最后一个VIN(MIN)公式设定了RSS的最大值。在选择RSS之后,RIN的最大值(针对该特定的RSS)利用第一个

VIN(MIN)公式来计算:

![]()

这两个公式实现了RSS和RIN阻值的最大化(因而减少了功耗),同时仍然提供了接通充电泵所必需的VC1电压。把电源电压增加至超过最小电源电压将增加RSS中的电流和功率,并缩短C1充电所需的时间。至于那些有可能需要一个更小RSS(MAX)的情形,将在"最大电源电压启动"部分进行讨论。

最大电源电压起动

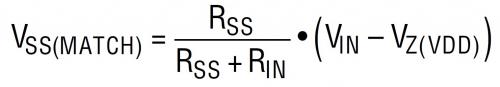

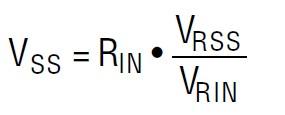

在启动期间,还有可能存在最大过压电源。过压保护电路必须在高电压被传送至负载之前唤醒。GATE引脚电压在C1充电的过程中动态地斜坡上升。电容器C1必须充电至2.55VUVLO1门限,以在OUT引脚电压超过过压调节点VREG之前接通调节放大器和基准。此类情况有可能把RSS的阻值减小至上述"最小电源电压启动"中所规定的最大值以下。RSS中的电流超过了由VSS引脚所供应的电流(本质上IRIN)时,电容器C1开始充电。IRIN=IRSS时VSS引脚上的电压现在被标记为VSS(MATCH)。VSS引脚电压是一个位于RIN和RSS之间分压器的中点电压(在把VDD至VSS的齐纳箝位电压从电源电压减去之后)。

当VIN增加时,VSS(MATCH)电压增加。如果匹配电压超过了过压调节点(VREG),则负载不受保护。情况的确如此,因为C1在VSS已经超过VREG时仍将需要充电至2.55V。由于OUT引脚电压至少比VSS高2.55V,因此它超过了规定的最大值。应选择充分低于VREG(至少要低2.55V)的匹配点(在电源电压处于最大值的情况下),从而允许C1及时充电以保护负载免遭过压的损坏。实际上,使VSS引脚电压比VREG低7V可为C1的充电提供所需的裕量。

VSS(MATCH)(MAX) = VREG–7V

增加RSS将提高匹配点,因此确定最大RSS同时仍然提供针对过压的保护是有益的。采用IRIN=IRSS:

采用:

RSS = VSS(MATCH)(MAX) = VREG – 7V

RIN = VIN – VZ(VDD) – VRSS

代入:

如果我们保证RSS<RSS(MAX),则下式成立:

VSS(MATCH) < VSS(MATCH)(MAX)

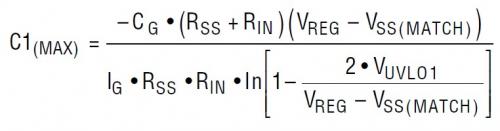

C1负责对充电泵进行旁路,且数值至少必需为0.22F。C1的尺寸也需要加以限制。栅极电容器(CG)决定了最大输出电容器C1(MAX),以将在OUT电压超过过压门限之前充电至2.55VUVLO1门限(VUVLO1)。

在大多数场合中:

C1(MAX)=10•CG至100•CG

GATE电容器,CG

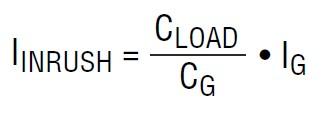

栅极电容器用于实现三项功能。第一:CG负责吸收过压瞬变期间来自MOSFET栅极至漏极电容的电荷。第二:该电容器还充当过压调节放大器的一个补偿组件。用于保证稳定性的CG最小值为2nF。最后,CG可设定GATE和OUT引脚的电压变化速率。GATE引脚电压的上升斜率等于20A/CG。该斜率决定了流入负载电容器的充电电流。

CG的额定电压必须大于调节电压(VREG)。

MOSFET的选择

LTC4366驱动一个N沟道MOSFET以传导负载电流。MOSFET的重要特性是接通电阻RDS(ON)、最大漏-源极电压V(BR)DSS、门限电压和SOA。可容许的最大漏-源极电压必须高于电源电压。如果输出短路到地或者在过压过程之中,则整个的电源电压将出现在MOSFET的两端。

MOSFET的门限电压在最小电源电压启动计算中使用。对于采用低于12V电源的应用,需要一个逻辑电平MOSFET。如果所用的电源高于12V,则使用一个标准门限N沟道MOSFET就足够了。

MOSFET的SOA必须包含所有的故障状况。在正常操作中,传输晶体管完全导通,因而耗散极少的功率。但在过压故障期间,GATE引脚电平被维持以通过MOSFET调节输出电压。大电流与MOSFET两端的高压降在这些场合中可以共存。必须将MOSFET的SOA曲线与故障定时器电容器的选择一道加以审慎的考虑。

布局考虑

由于SD、VDD和GATE引脚上具有高阻抗,因此这些引脚对于至地漏电流很敏感。例如:SD引脚上的至地漏电流若大于1.6A,则将启动停机状态。提供远离接地走线的足够间距并在裸露引脚上添加敷形涂层材料可降低漏电流中断系统操作的风险。应把旁路电容器C1布设在尽可能靠近OUT和VSS引脚的地方,这一点很重要。将10 电阻器安放在尽可能靠近MOSFET栅极引脚之处。这将减少导致MOSFET自激振荡的寄生走线电容。

FB引脚在调节环路闭合时对寄生电容很敏感。这种电容性负载引起的后果之一是在过压调节期间产生输出振荡。建议将电阻器RFB1和RFB2布设在靠近器件引脚的地方,并最大限度地减小FB走线本身的尺寸。

更多技术文章,欢迎访问凌力尔特社区!

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...