- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

集成式电源管理单元简化基于FPGA的系统

作者:Maurice O’ Brien ADI公司

医疗和仪器设备(如便携式超声设备和手持式仪器)的趋势也是尺寸越来越小,要求在更小的面积上以更有效的方式为FPGA、处理器和存储器供电。典型的FPGA和存储器设计需要密度非常高的电源,它能以快速瞬变响应输送大电流以便为内核和I/O电源轨供电,同时通过低噪声轨为锁相环(PLL)等片内模拟电路供电。电源时序至关重要,应确保FPGA在存储器使能之前上电并运行。带精密使能输入和专用电源良好输出的稳压器支持电源时序控制和故障监控。电源设计师通常希望将同一电源IC用在不同应用中,因此,必须能够改变电流限值。这种设计重用可大幅缩短产品上市时间——任何新产品开发流程中的关键要素之一。

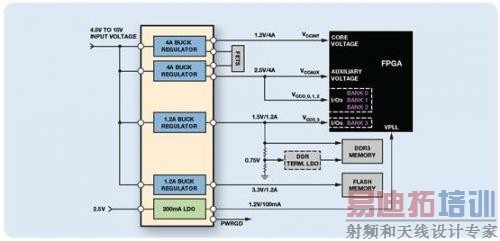

考虑具有1路12 V输入和5路输出的FPGA的多轨电源管理常见设计规格:

• 内核电轨: 1.2V (4 A)

• 辅助电轨: 1.8V (4 A)

• I/O电轨: 3.3V (1.2A)

• DDR存储器电轨: 1.5V (1.2A)

• 时钟电轨: 1.0V (200mA)

FPGA供电应用实例

典型的分立方案有4个开关稳压器连接到12 V输入轨。 一个开关稳压器的输出预调节LDO以降低功耗。 另一种方法是使用一个稳压器将12 V输入降压至5 V中间轨,然后再经调节以产生所需的各个电压。 该方案的成本较低,但由于采用两级电源转换,效率也较低。 在以上两种方案中,各稳压器都必须独立使能,因此,可能需要一个专用电源时序控制器来控制电源的时序。 噪声可能也是一个问题,除非所有开关稳压器都能同步以降低拍频。

将多个降压调节器和LDO集成到单个封装中,可显著缩小电源管理设计的总体尺寸。 此外,与传统分立方案相比,智能型集成解决方案具有许多优势。 减少分立元件数目可大幅降低设计的成本、复杂度和制造成本。 集成电源管理单元(PMU) ADP505x系列可在单个IC中实现所有这些电压和功能,所用PCB面积和元件大幅减少。

为了最大程度地提高效率,各降压调节器均可直接从12V电压供电,从而无需预调节器级。 降压调节器1和2具有可编程电流限值(4A、2.5A或1.2A),因此电源设计师可以快速轻松地为新设计改变电流,大大缩短开发时间。 LDO可由其中一个降压调节器供电,提供低噪声1 V电源轨用于噪声敏感的模拟电路。

某些设计中,两者都很重要: 对较高电流轨使用较低的开关频率以提供最高电源效率,对较低电流轨使用较高的开关频率以缩小电感尺寸和实现最小的PCB面积。 主开关频率提供一个2分频选项,允许ADP5050以两种频率工作。 降压调节器1和3的开关频率可通过I2C端口设置为主开关频率的一半。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...