- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SoC存储器的智能电源连接方法

简介

SoC设计也面临着一系列的难题和挑战,其中出现的最大挑战之一是硬核IP模块集成和验证。随着技术的扩展,设计并集成IP模块变得越来越难。在深亚微米技术设计中,IR压降往往会对功能性造成显著的影响。

本文介绍了一种新的IR压降方法,使用这种方法可以带来非常稳健的内部电网结构。凭借强大的设计技术,该IR压降方法能带来出色的硅结果,单端口高速RAM上的8Kx72切口最低电压可低至0.52V。

存储器基本架构

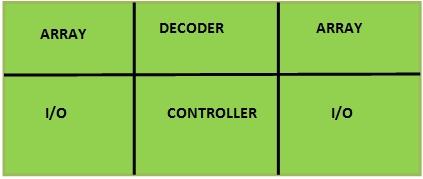

存储器通常包含四个基本模块——控制器、解码器、阵列比特单元和输入/输出端。大部分吸收较多电流的大型驱动器都被置于输入/输出端、解码器和控制模块中。因此,为使各模块正常运作,我们需要确保每个驱动器有足够的电压来保证正常运行。

存储器基本模块图图1:存储器基本模块图

图字:阵列;解码器;阵列;输入/输出端;控制器;输入/输出端

系统芯片存储器的连接指南

1.一般方法

一般地,存储器所有者会以电网的捆扎频率的形式向设计电源连接的SoC设计人员提供所有电源轨的指导大纲。捆扎频率定义了给定电源线上的两个连续金属带(一般在顶端金属)之间的距离。在建造电网时按照捆扎指导大纲操作,可确保几乎所有驱动器可获得足够的工作电压,实现良好的性能。

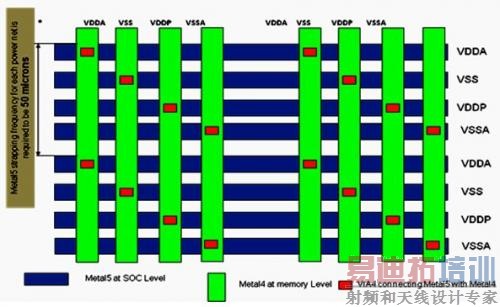

在图2中,M4的供电轨是垂直的,应与水平的M5相连接。目标存储器中存在着多个电源域,如VSSA、VDDP、VSS和VDDA等等。

图2:系统芯片的电源连接结构图

图字:要求每个电源网的金属5捆扎频率为50微米;系统芯片级金属5;存储器级金属4;VIA4将金属5与金属4相连接

将捆扎频率作为唯一决定因素会导致的问题

假设对于某项特定的技术,规定了一个50um的捆扎频率。也就是说,每隔50um就应当重复电源线以确保恰当的功能和输出。在这种情况下,只有一个电源线的驱动(VDD、VSS)是受IR压降影响最严重的,因此这些装置可能会出现异常行为。

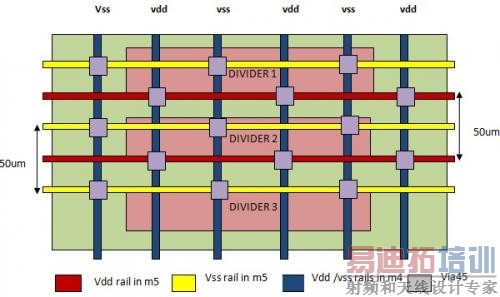

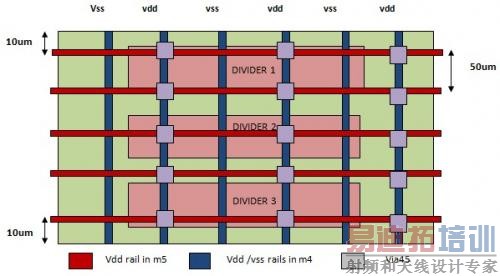

在图3中,分频器3和分频器1只分到一根VDD/VSS电源线,因此可能无法获得足够的电压来确保正常的运作。此处,分频器2有多个电源线,因而可以正常运行。

在单块存储器中,仅仅使用strapping技术也许足以确保正常的运行。然而,对于多组架构的储存器或较长、较宽的存储器而言,仅仅使用strapping技术是不足以实现IR压降要求的。因此,在这种情况下,除了strapping之外,我们还需要使用其他方法来帮助我们实现IR的压降目标。

图3:长型存储器的电源连接

图字:分频器1;分频器2;分频器3;M5上的Vdd导轨;M5上的VSS导轨;M4上的VDD/VSS

2.建议方法

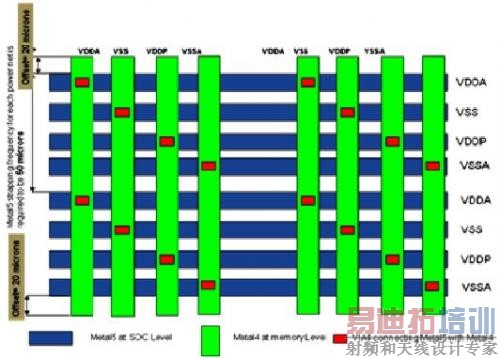

为了使这些器件(分频器)能够正常运作,应当引入偏移量的概念,并且应当在整个存储器编译器进行IR压降分析,包括所有可能的组合(如冗余、源偏置、DVFS和BIST等等)。下面将对以上概念进行详细说明。此处偏移量被定义为顶层金属的第一电源线和内存实例顶部之间的距离;或顶层金属的最后一跟电源线和内存实例底部之间的距离。因此,在制作存储器电网时,同时利用偏移量和strapping的概念可以改善IR的压降水平。

图4:20微米偏移量的电源连接

选择合适的偏移值

按照规定,偏移值应该总是比捆扎频率要少得多。这样的偏移值可以确保某个给定内存块中的所有分频器都能有一个以上的电源线,从而获得足够的正常运行所需的电压。

下面讨论的一种方法可以用来为某个给定的存储器选择正确的捆扎频率和偏移值。

如何确定捆扎频率

情况1:连续的控制电源/接地导轨。

第1步:对各种捆扎频率进行IR压降分析,直到IR压降在IO区停止。应将该频率作为SFIO.

第2步:继续分析IR压降直到IR压降在管制区内停止。应将该频率作为SFCO.

第3步:实际捆扎频率= SF =最小值(SFIO,SFCO)。

情况2:非连续的控制电源/接地导轨。

第1步:对各种捆扎频率进行IR压降分析,直到IR压降在IO区无法继续。应将该频率作为SFIO.

第2步:继续该分析直到IR压降在管制区内停止。其中,电源strapping线在控制区以外运行,到达不连续的存储器电源线的末端,以找到控制区捆扎频率的最大可能值。应将该频率作为SFCO.

第3步:实际捆扎频率= SF =最小值(SFIO,SFCO)。

找出偏移值

情况1:如果SFIO SFCO

SFIO/4被作为分析的初始偏移值,按照上面的第3步确定捆扎频率。再一次用该偏移值和上述步骤中计算出的捆扎频率分析IR压降。

a.如果IR压降过高,则通过少量增加偏移值重复进行IR分析。重复执行此过程直到IR压降停止(即IR压降超出目标限制)。选择此IR压降恰好达到目标上限时的偏移值。如果IR压降在SFIO/4过高,至少针对(SFIO/4-5)、(SFIO/4-10)和(SFIO/4-15)进行分析,以确保降低IR压降,并且不会再恶化。这样获得的值将是最后的偏移值。应将偏移值作为OS.

b.如果IR压降停止,则通过少量降低偏移量重复执行IR分析。重复此操作,直到IR压降达到目标值。应将该值作为OS.

如果SFIO/4 > SFCO/2,则必须确保在IR压降到达值SFCO/2之前,IR压降分析会持续进行。另外还必须确保IR压降在达到该值之前不会停止。如果IR压降在任何大于SFCO/2的偏移值上停止,那么最近的一个大于SFCO/2的偏移值应为最终偏移值。

例如,假设针对某项特定的技术,捆扎频率被定为50um,而偏移值则被定为10um.

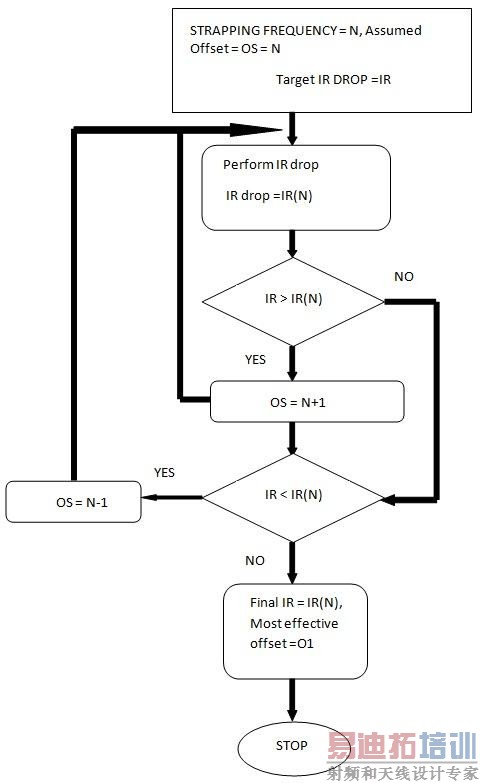

我们运用下面的演算法来确定给定捆扎频率的正确偏移量范围。

图5:使用演算法寻找最佳偏移值。

图字:捆扎频率= N,假设的偏移= OS = N;目标IR压降= IR;执行IR压降;IR压降= IR(N);最终IR = IR(N);最有效的偏移= O1;停止

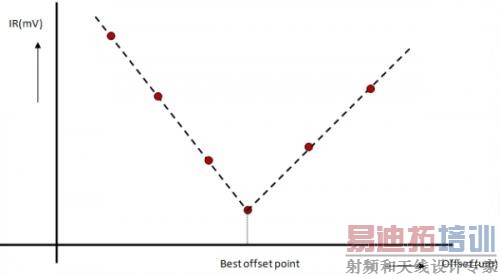

按照上述针对各种捆扎频率的算法,我们得到一张IR压降偏移值之间的关系图,类似于图6所示的内容。最小IR对应的偏移量即为最佳偏移值。

图6:给定捆扎频率上IR与偏移频率的关系图。

图字:最佳偏移量;偏移量(um)

图7:使用偏移量和捆扎频率的电源连接。

如图7所示,分频器1、分频器2和分频器3都会接收多个电源线,由此获得合适的工作电压。

最差IR压降的分析

让我们考虑两种情况的分析,具体条件如下:

功率IR压降的分析条件

Pbcs30V132V132T150

输出负载:400ff

输入转换:200ps

最大切换,所有输出切换

地址和数据输入的最大转换

寄生参数:Cmin(最大R,最小C)

供应网RC,只有信号RC网

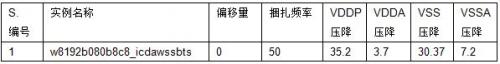

标签偏移量(从底部开始):10um、15um、20um

标签频率:50um

1.只限定捆扎频率-对于每个电源供应(VDDA/VDDP/VSSA/VSS),都必须严格遵守捆扎频率为50微米。

不带偏移量时MBLK CM8的IR结果

2.同时限定捆扎频率和偏移量-在这种情况下,我们会既考虑偏移量又考虑捆扎频率,而不是只考虑捆扎频率。偏移值必须小于捆扎频率。

我们通过改变M5带的偏移值做了几个实验,得到了以下结果。很明显,相对于没有偏移量的实验,IR压降下降了20-30%。偏移值应同时用于顶部线和底部线。

即使在仅使用捆扎频率就能满足IR压降指标的情况下,在使用捆扎频率的同时使用偏移量的概念作为补充,可以显著节省电网线路(针对同样的IR指标)的数量。

带偏移量时MBLK CM8的IR结果

注意事项

1.上述IR压降的数据适用有功电流

2. Vdd的通过标准为5%(下降+上升)

3.电压降值单位为毫伏。

本文小结

正如上述图表所示,相对于那些没有使用偏移值的实验,在使用偏差值的实验中IR得到了明显的改善,IR压降改善了大约20-30%。将偏移值概念用于系统芯片存储器的连接,能够极大地改进IR压降水平,同时也改善了硅结果。这项用于将存储器连接至系统芯片的方案(同时运用偏移值和strapping),也可以应用于其他硬宏,如闪存和其他模拟模块。

对于给定的IR压降目标,相对于仅仅使用strapping,偏移量与strapping的结合使用还能够节省大量的电网线路。上述概念已被用于各种实时设计,硅结果表明最小压降值(Vmin)有了明显的进步。

参考文献

1.《国际半导体技术蓝图》半导体产业协会,2005年。

2.《Gigascale系统级芯片(GSoC)的全球互联建模》,作者Zarkesh-Ha P.,提交给佐治亚理工学院学术学院的博士论文,2001年2月。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:了解模拟世界中的放大器

下一篇:一种新型的单相双Buck光伏逆变器的设计方案