- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

详解JESD204B串行接口时钟需求及其实现方法

随着数模转换器的转换速率越来越高,JESD204B串行接口已经越来越多地广泛用在数模转换器上,其对器件时钟和同步时钟之间的时序关系有着严格需求。本文就重点讲解了JESD204B数模转换器的时钟规范,以及利用TI公司的芯片实现其时序要求。

1. JESD204B介绍

1.1 JESD204B规范及其优势

JESD204是基于SerDes($174.9800)的串行接口标准,主要用于数模转换器和逻辑器件之间的数据传输,其最早的版本是JESD204A,现在是JESD204Bsubclass0,subclass1,subclass2.区别主要在于其对同步和链路间固定时差的测量。目前市场上比较多地数模转换器接口是JESD204B subclass1.其最大传输速率可达12.5Gbps,支持多链路和多器件的同步以及固定时差的测量。下表是各版本之间的差异:

Table 1

在JESD204接口出现以前,数模转换器的数字接口绝大多数是差分LVDS的接口,这就造成了布板的困难,当PCB的密度很大的时候就需要增加板层从而造成印制板的成本上升。而JESD204B接口是串行接口,能有效减少数据输出的差分对,能最大限度的简化Layout.因此JESD204B是高密度板不可或缺的接口。但因其需要进行严格的同步和以及时延的测量,与之接口的逻辑会比LVDS接口复杂很多,幸运的是现在逻辑厂商都集成了专用的JESD204IPCore在他们的软件里,从而简化了逻辑的设计。

1.2 JESD204B时钟的需求

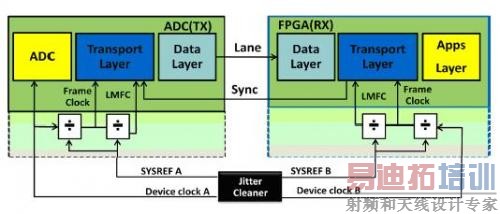

尽管JESD204B也有不同的版本,但越来越多的厂商选择Subclass1,因此市面上绝大多数的数模转换器都是基于这个版本设计的。本文就以JESD204B subclass1来讨论时钟的时序需要以及TI时钟芯片方案的实现。任何一个串行协议都离不开帧和同步,JESD204B也不例外,也需要收发双方有相同的帧结构,然后以一种方式来同步,即辨别起始。JESD204B是以时钟信号的沿来辨别同步的开始,以及通过一定的握手信号使得收发双方能够正确识别帧的长度和边界,因此时钟信号及其时序关系对于JESD204B就显得极其重要。下图是典型的JESD204B系统的系统连接,Device Clock是器件工作的主时钟,一般在数模转换器里为

图1

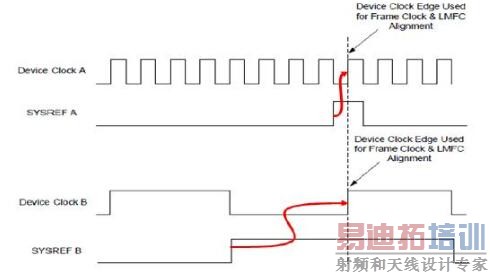

其采样时钟或者整数倍频的时钟,其协议本身的帧和多帧的时钟也是基于Device Clock.SYSREF是用于指示不同转换器或者逻辑的Device Clock的沿,或者不同器件间Deterministic latency的参考。如下图所示,Device Clock和SYSREF必须满足的时序关系。

图2

SYSREF的第一个上升沿要非常容易的能被Device Clock捕捉到,这样就需要SYSREF和Device Clock满足上图的时序关系。通常会因为PCB的线长以及时钟器件不同通道输出时的Skew,会带来一定的误差,Device Clock的上升沿不一定正好在SYSREF的脉冲的正中间,工程上只要在一定范围内就能保证JESD204收发正常工作。

[p] 2.JESD204B时钟的实现

2.1专用的JESD204B时钟芯片

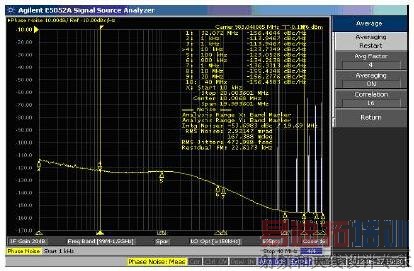

LMK04820系列的时钟芯片是一款专用的JESD204B时钟芯片,Device Clock和SYSREF是成对输出的,其输出的时序满足其时序要求,应用较为简单,但当用户需要连续模式的SYSREF时,会引起一定串扰如下图所示(983.04MDevclk and 7.68MSysREF),可能会造成数模转换器的性能下降。当然SYSREF工作在脉冲模式,LMK04820是一个完美选择。如果板上JESD204B时钟路数较多,LMK04820的输出不能满足要求,可以用LMK1802扩展得到更多的时钟输出。

图3

2.2通用的LVDS时钟芯片

在某些应用中客户的系统上既有JESD204B的数模转换器,也有LVDS接口的数模转换器,或者客户需要用到连续模式的SYSREF,这时LMK04800系列的时钟芯片是理想选择。LMK04800是带有输出延时调整的去抖芯片,我们调整其输出的延时,使得两路不同通道的输出的时序满足JESD204B时序的要求,分别作为Device Clock和SYSREF.因此延时调整是LVDS时钟芯片实现JESD204B时钟的核心。

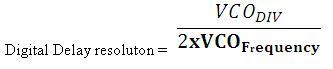

LMK04800的输出有数字延时和模拟延时,在多数应用时数字延时的调整精度已经能满足了,因此不推荐模拟延时调整,另外模拟延时会带来输出时钟噪底的恶化,一般会恶化3-5db.数字延时的精度取决于第二级集成VCO

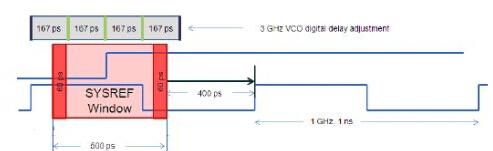

如果VCO_DIV没有用或者用外部的VCO,则分子必须等于1.当延时设置完成后,必须有同步事件才能使得设置生效,同步可以通过寄存器,硬件管脚去触发。当明白了数字延时的调整精度,再结合PCB传输延时就可以计算出最大的调整误差。如果Device Clock是1GHz,而此时VCO的频率是3GHz,则根据上面公式调整精度是167ps,另外我们需要考虑到器件不同输出通道的Skew,这里假设±30ps,另外还需要考虑到SYSREF和Device Clock的PCB长度不等长,这里假设0.5cm,约±30ps,则我们可以得到SYSREF可调整的窗口:

图4

图中400ps是LMK04800 LVDS的输出的上升沿和下降沿所用时间(上升沿和下降沿都是200ps)。图中我们可以根据以上的条件计算得到调整精度是167ps,Device Clock的周期是1000ps,则可调整的窗口为1000-400-120=480ps,即为红色的的影映区域,当SYSREF的上升沿在红色的区域调整时,Device clock可以容易的检测到SYSREF的上升沿,否则需要等到下一个Device clock周期才能检测到SYSREF上升沿。

3结论及其测试验证

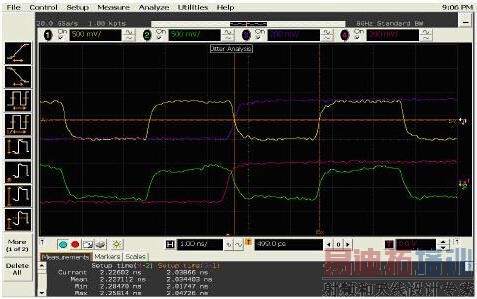

相比LMK04828($12.6000),我们用LMK04800和LMK01010($7.7512)产生JESD204B的时钟,既能满足

图5

全是JESD204B的器件的要求,也能很好的用在有LVDS接口需要的系统中。另外LMK04800是一款非常成熟的具有高延时精度的时钟芯片,其性能被用户广泛接受,同时在某些需要用延时调整去适应DPD算法的应用中也能很好提供完美时钟解决方案。如下图所示,这是通过调整LMK04800的输出延时,用示波器采集的JESD204B的时钟,其时序能很好的满足其标准。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:电能质量检测与监测分析终端设计汇总

下一篇:三相电供电常见故障解析及改善方案