- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

安森美半导体的高频准谐振反激式参考设计实现超高功率密度紧凑适配器

录入:edatop.com 点击:

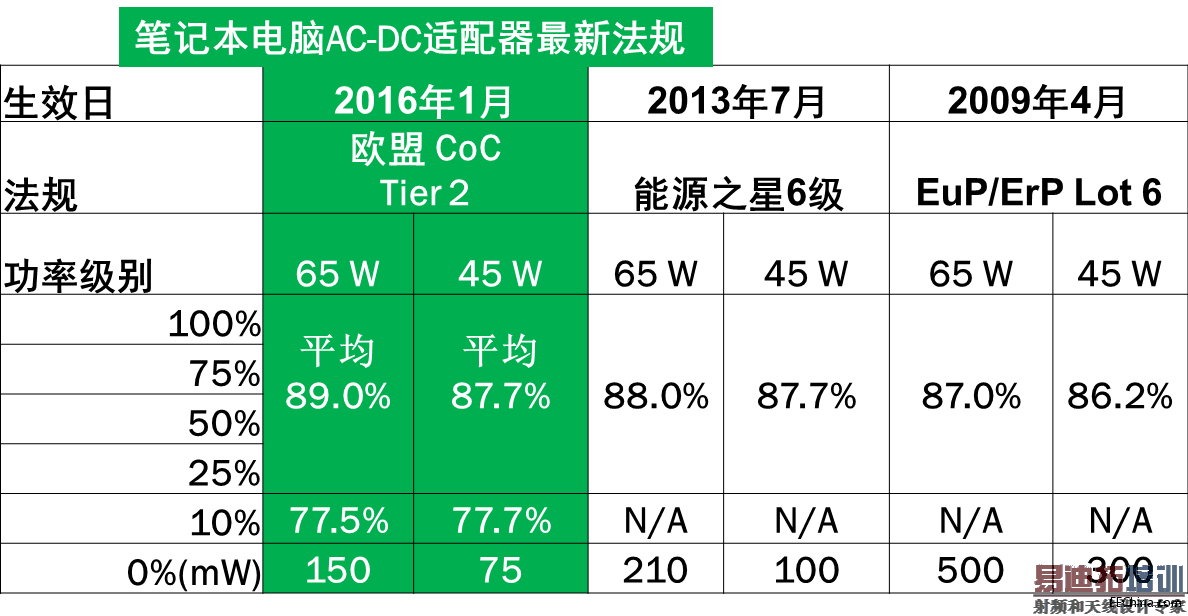

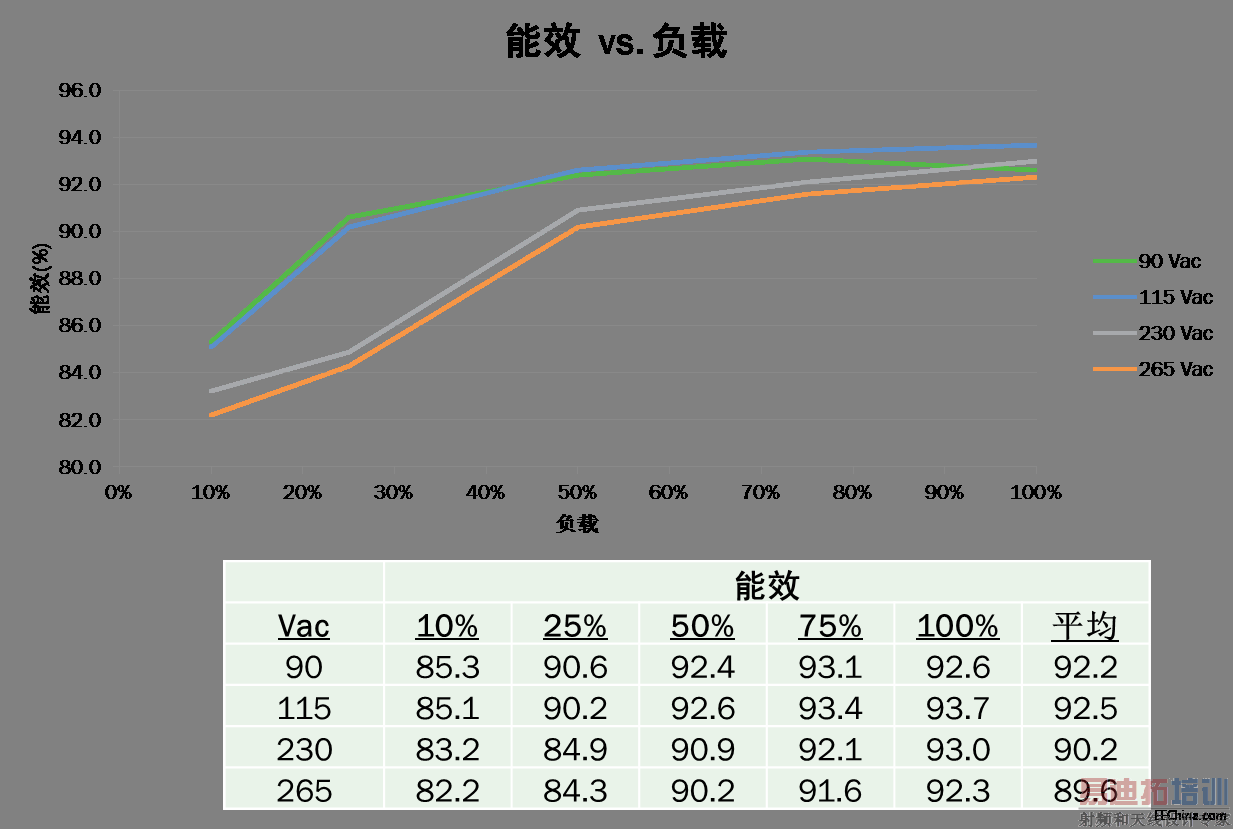

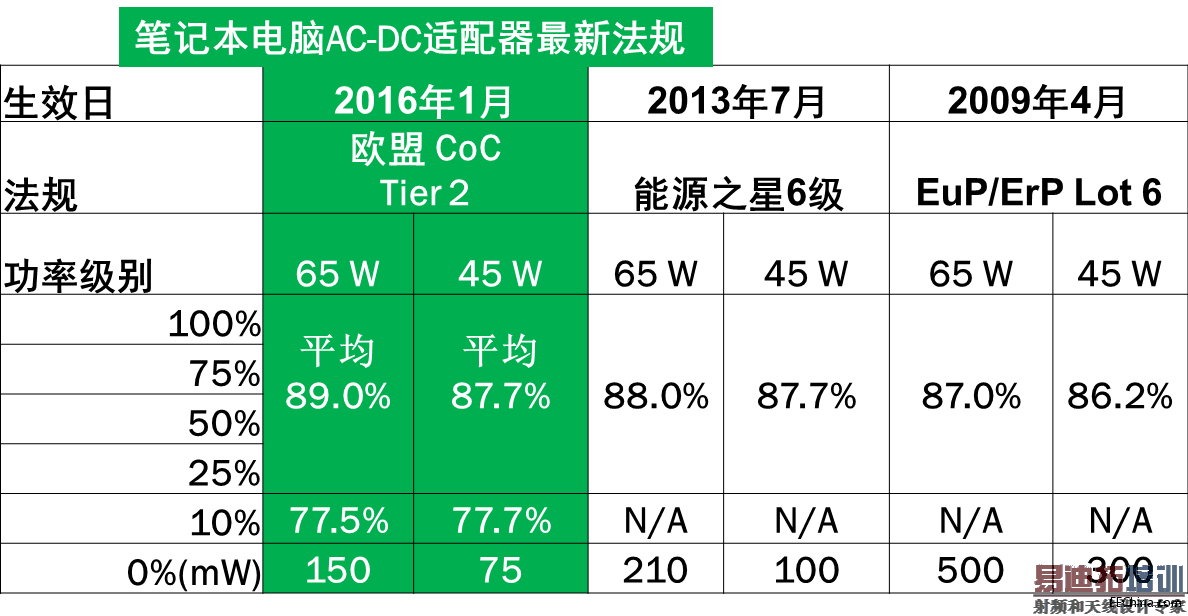

为提供更佳的用户体验,笔记本电脑及其适配器不断向小型化、高功率密度化方向发展,便于消费者外出时携带更方便,同时,还需具备高平均能效和极低待机功耗,以符合日趋严格的各种能效法规。如于2016年1月1日生效的欧盟CoC V5 Tier 2 规定,输出功率为45 W和65 W的AC-DC适配器平均能效需分别达到87.7%和89%,待机功耗分别低于75 mW和150 mW,并且还要求10%负载条件时的能效需分别达到77.7%和77.5%。电源设计工程师面临体积、能效和成本等多方面的设计挑战。

表1. AC-DC 适配器能效法规一览

开关频率直接决定开关电源的功率密度,提高开关频率可有效地减小无源功率器件如变压器、输出电容的尺寸,从而提高功率密度;高功率密度应用仅满足能效规范远远不够,因为体积减小时,散热面积也相应减少,需提高能效以减少发热,减小对内部元器件寿命的影响;此外,工程师需将成本控制在合理范围内,以在竞争激烈的市场处于有利地位。

准谐振反激 + 同步整流 = 高功率密度适配器

LLC拓扑结构可提供高频率和高能效,但其成本较高,且对输入电压范围有严格要求,不适用于笔记本电脑这一功率等级。采用准谐振反激式拓扑加上同步整流(SR)可轻松地设计出满足体积、能效、成本等要求的高功率密度适配器,如安森美半导体的高频准谐振反激式控制器NCP1340/1+SR控制IC NCP4305/80。

准谐振模式允许使用相对大的缓冲电容Clump,额外增加的Clump (10-22pF)可以减少MOS管关断损耗,减少电磁干扰(EMI)。准谐振反激有利于次极端加SR,可降低整流二极管导通损耗,减少次极端整流管尖峰电压,降低其耐压要求。

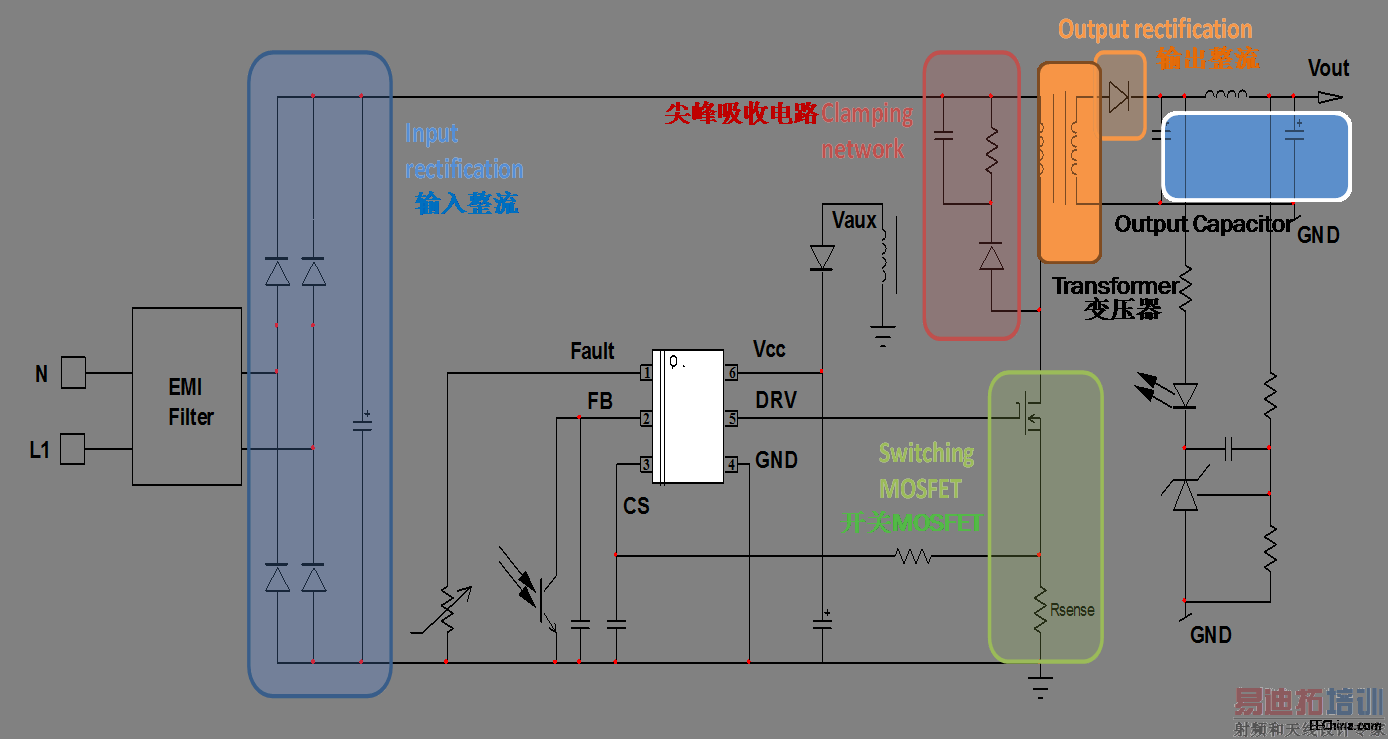

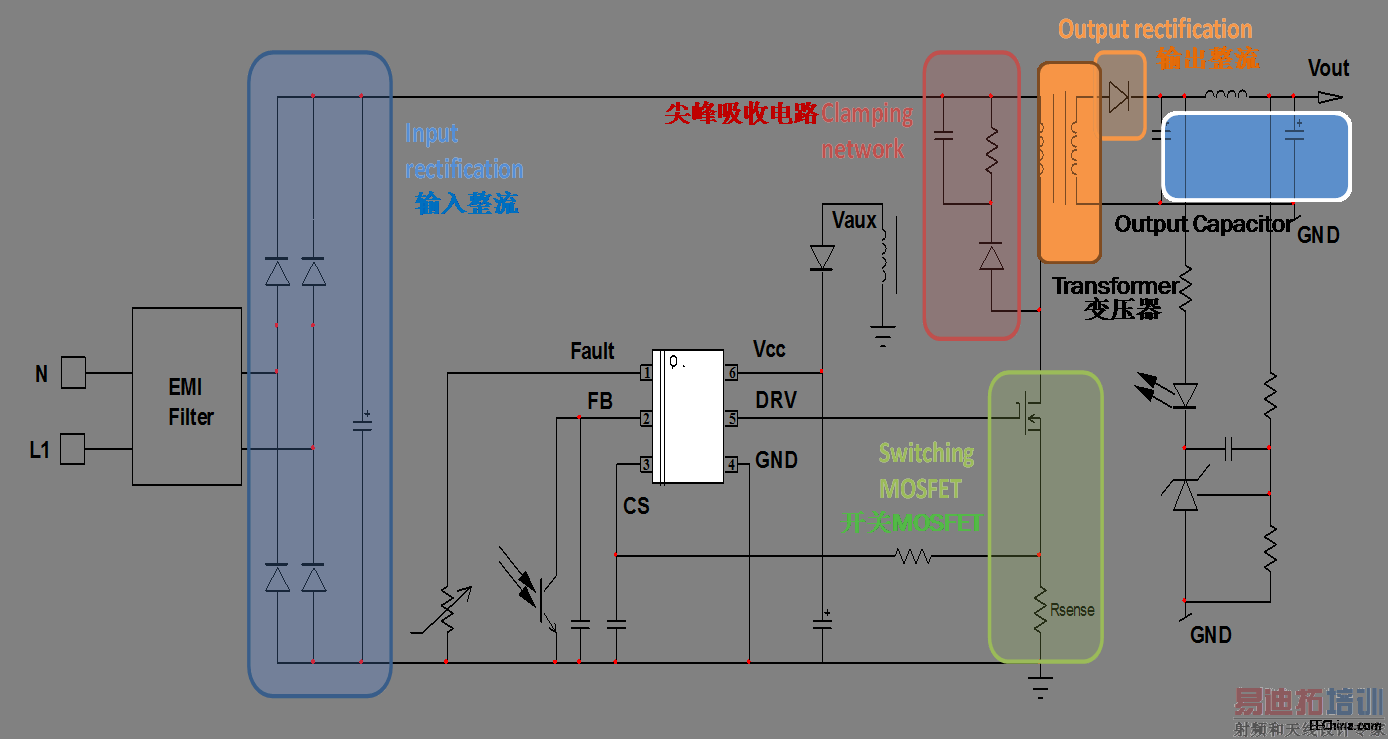

图1. 准谐振模式允许使用相对大的缓冲电容Clump

准谐振式反激电源损耗分析和设计要点

分析准谐振反激损耗旨在提高工作频率后再减少功率损耗。准谐振反激电源的损耗主要分布在初级MOSFET、尖峰吸收电路、变压器和输出整流。

图2. 准谐振反激电源的损耗分布

1.初级MOSFET损耗分析

初级MOSFET损耗主要包括导通损耗、开关损耗和驱动损耗。导通损耗由漏源导通阻抗Rds(on)和初级端均方根电流定义。对于开关损耗,由于MOSFET的结电容与其Vds电压成非线性比例,所以不能用简单的电容储能公式计算,需要将实际的结电容考虑进去,结电容可理解为MOSFET DS 网络间等效的除了MOSFET内部的结电容外的其它电容。驱动损耗在开关频率较低时可以不作考虑,但在高频应用中不能忽略,它在MOSFET导通和关断时产生,主要取决于MOSFET总门极电荷Qg、开关频率和IC工作电压Vcc,损耗大部分消耗在驱动电阻上。

因此,对于MOSFET的选取,在高频应用中,Rds (on) x Qg乘积数越低越有利于降低导通损耗和驱动损耗。应选择体积小、薄且散热性好的低热阻封装。由于氮化镓(GaN) MOSFET具有更优的Rds (on) x Qg参数,可额外增加约0.3%的满载效率,而在成本允许的情况下,GaN MOSFET是理想的选择。

2. 尖峰吸收电路损耗分析

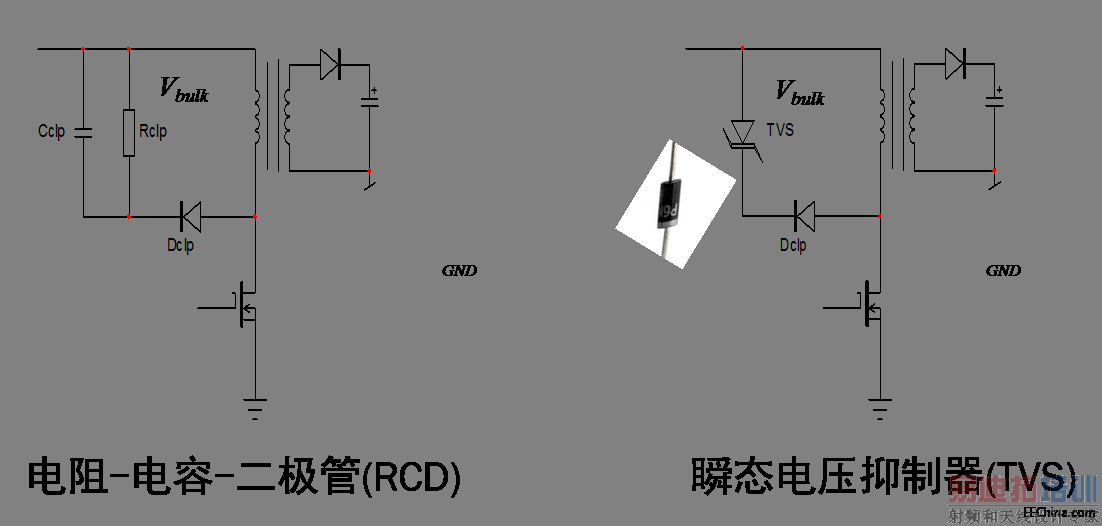

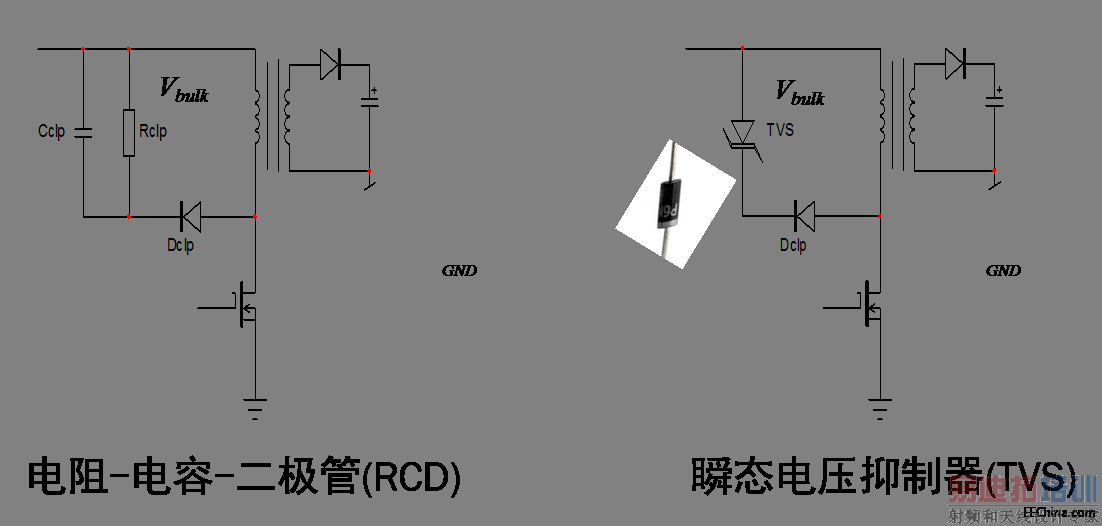

尖峰吸收电路主要用于钳制MOS管Vds电压,防止其过压击穿。电阻-电容-二极管(RCD)吸收和瞬态电压抑制器(TVS)吸收是两种常用的电路,其中RCD最为常用,可靠性较高。

图3. 两种常见的尖峰吸收电路

对于RCD电路中,较大的吸收电容C可减少钳位电压纹波,但会增加待机功耗,所以C的选取一般以满载时5%至10%钳位电压纹波为宜。如果吸收电阻R较热,可减小变压器漏电感,选用Trr一致性好的慢管,可降低钳位电压,减少R损耗。

钳位电压方面,选择高的钳位电压可降低RCD吸收损耗,但需选高耐压MOS管,这会导致成本增加,而且变压器初级电流衰减速度会变快,次级整流电流上升斜率变陡,不利于EMI和次级同步整流效率优化。选择低的钳位电压,有利于EMI,次级同步整流控制,但RCD吸收损耗会增加。整流二极管D选用慢管可减少钳位电压和改善EMI,但二极管温升会较高。所以需综合考虑各方面影响,权衡择取。

3. 变压器损耗分析

变压器损耗主要包括磁芯损耗、线圈损耗和高频附加的磁芯及线圈损耗。对于>300 KHz应用,相比TP4A, 3C90或3F3,3C95/P51磁芯材料具有更低损耗。高频应用时,临近效应和趋肤效应导致绕线交流电阻增大,铜损增加,多股绞线将是非常不错的选择。

提高开关频率,可以减少变压器初级电感量,从而减少磁芯损耗。采用多股胶合线,减少趋肤效应,分开初级绕组(三明治绕法)以降低邻近效应。如安森美半导体的45 W参考设计选用RM7变压器,采用多股线加三明治绕法,初级端为24转25x AWG#38 绞合线,次级端为4转150x AWG#44 绞合线,采用3C90材料。

4. 输出整流损耗分析

输出整流通常有二极管整流和SR两种方案。由于SR MOS导通压降远低于二极管导通压降Vd,所以可比传统的二极管整流实现更高能效。

和初级MOSFET一样,SR损耗分为开关损耗(低压时可忽略不计)、驱动损耗(取决于Qg、开关频率及Vcc)和导通损耗。其中导通损耗包括MOSFET导通时的内阻损耗和体二极管在MOSFET导通前的导通损耗,体二极管导通损耗和MOSFET导通延时密切相关。安森美半导体的NCP4305/80系列同步整流控制IC具有极短导通延时,可调至30 ns,同时具有强大的驱动能力,能快速通断SR MOSFET。如在45 W参考设计中,SR MOSFET选用NVMFS6B03NL,内阻仅4 mΩ,Qg 70.7nC,若选用GaN SR MOSFET将可获得额外约0.3%的满载能效提升。

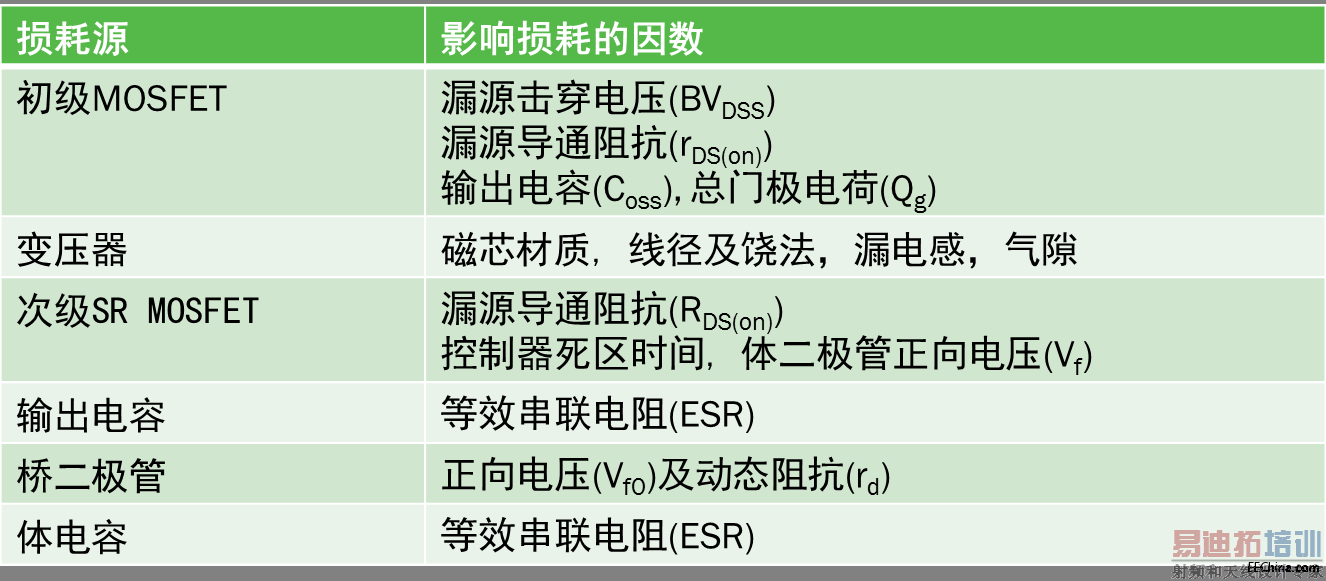

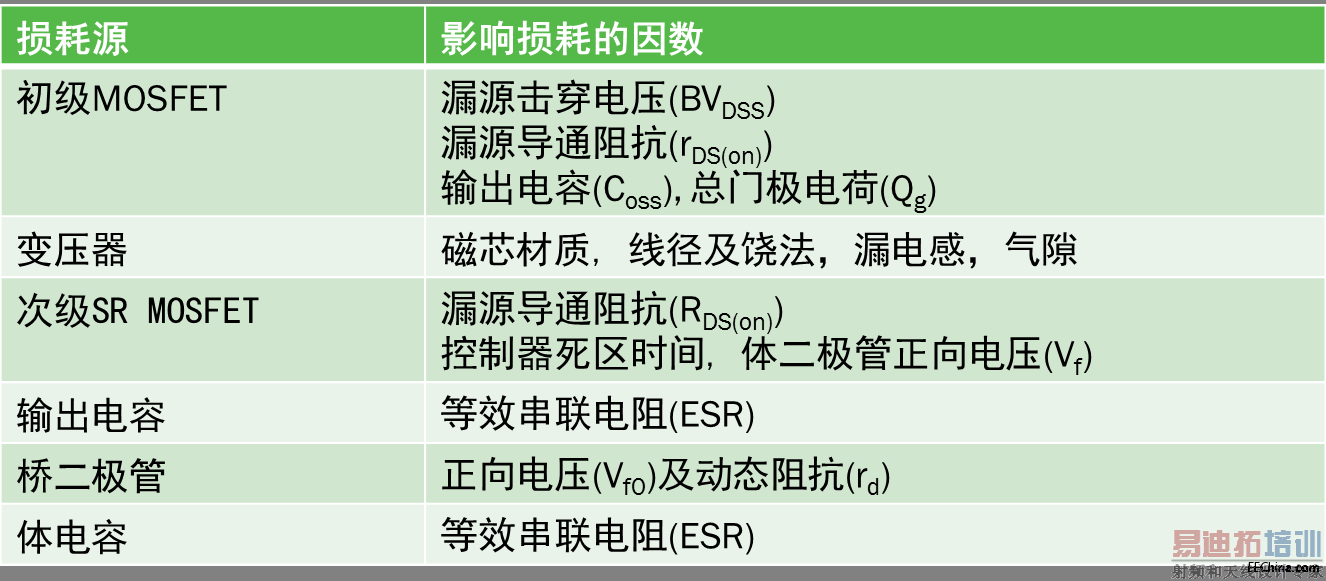

综上所述,损耗源及影响损耗的因素可归纳为:

表2. 损耗源及影响损耗的因素

45 W高功率密度适配器参考设计

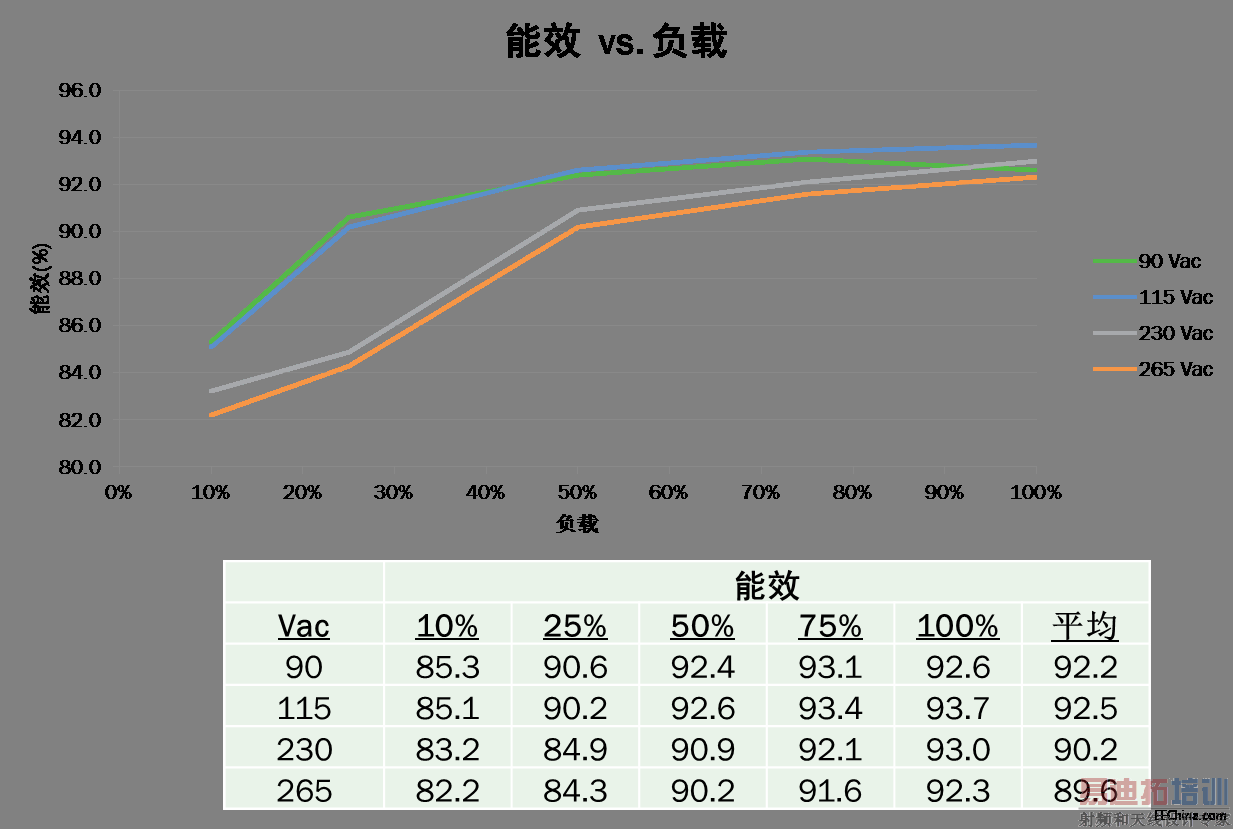

该参考设计采用安森美半导体的NCP1340高频准谐振反激+NCP43080 SR架构, 在能效和待机功耗方面彰显出色性能,提供19 V/2.4 A额定输出,90-264 V宽输入电压,体积仅50 mm x 33 mm x 22 mm,所需外围元件数少,满载能效超过92%,待机功耗低于30 mW,完全符合CoC V5 Tier 2能效要求。

图4. 45 W参考设计能效 vs. 负载曲线

其中NCP1340/1采用SO-8封装,高压启动,集成X2放电和欠压检测,运行达6个谷底锁定开关,可有效地解决因谷底数不稳定所产生的音频噪声问题,并通过最小频率钳位和Quiet-Skip运行消除噪声。人类能听到的频率范围是20Hz至20kHz,早期的跳周期控制IC将最低开关频率设置在25 kHz,但间隙工作频率通常会在2 kHz至4 kHz范围,所以一旦其进入跳周期模式,噪声还是很大的。Quiet-Skip将最大的间隙工作频率设置为800 Hz,虽然800 Hz仍在可听见的范围内,但其往往会与背景噪声很好的融合,所以不容易被察觉。NCP1340/1采用跳周期模式,电流消耗低,因而可实现低于30 mW的低待机功耗,具有频率抖动特性,可提升EMI性能,实测抖频功能可降低AV曲线低频段的峰值约5 dB。此外,NCP1341比NCP1340多了功率倍增模式,可提高瞬态带载能力,同时保持最小尺寸的变压器,实现1.5倍或2倍的额定功率输出,非常适合打印机、驱动电源等需要损失功率倍增的应用场合。

总结

设计高功率密度的适配器电源不但要满足更轻更薄的发展趋势以提升用户体验,还要符合日趋严格的能效要求,这对设计人员来说充满挑战。高频准谐振反激是适用于低于65 W的高功率密度电源适配器的拓扑结构之一。安森美半导体的45 W高功率密度参考设计采用准谐振反激NCP1340/1 + 同步整流NCP4305/80的架构,可轻松设计出小巧、低成本的高能效高功率密度适配器,满载能效超过92%,待机功耗低于30 mW,远远超越能效规范。

表1. AC-DC 适配器能效法规一览

开关频率直接决定开关电源的功率密度,提高开关频率可有效地减小无源功率器件如变压器、输出电容的尺寸,从而提高功率密度;高功率密度应用仅满足能效规范远远不够,因为体积减小时,散热面积也相应减少,需提高能效以减少发热,减小对内部元器件寿命的影响;此外,工程师需将成本控制在合理范围内,以在竞争激烈的市场处于有利地位。

准谐振反激 + 同步整流 = 高功率密度适配器

LLC拓扑结构可提供高频率和高能效,但其成本较高,且对输入电压范围有严格要求,不适用于笔记本电脑这一功率等级。采用准谐振反激式拓扑加上同步整流(SR)可轻松地设计出满足体积、能效、成本等要求的高功率密度适配器,如安森美半导体的高频准谐振反激式控制器NCP1340/1+SR控制IC NCP4305/80。

准谐振模式允许使用相对大的缓冲电容Clump,额外增加的Clump (10-22pF)可以减少MOS管关断损耗,减少电磁干扰(EMI)。准谐振反激有利于次极端加SR,可降低整流二极管导通损耗,减少次极端整流管尖峰电压,降低其耐压要求。

图1. 准谐振模式允许使用相对大的缓冲电容Clump

准谐振式反激电源损耗分析和设计要点

分析准谐振反激损耗旨在提高工作频率后再减少功率损耗。准谐振反激电源的损耗主要分布在初级MOSFET、尖峰吸收电路、变压器和输出整流。

图2. 准谐振反激电源的损耗分布

1.初级MOSFET损耗分析

初级MOSFET损耗主要包括导通损耗、开关损耗和驱动损耗。导通损耗由漏源导通阻抗Rds(on)和初级端均方根电流定义。对于开关损耗,由于MOSFET的结电容与其Vds电压成非线性比例,所以不能用简单的电容储能公式计算,需要将实际的结电容考虑进去,结电容可理解为MOSFET DS 网络间等效的除了MOSFET内部的结电容外的其它电容。驱动损耗在开关频率较低时可以不作考虑,但在高频应用中不能忽略,它在MOSFET导通和关断时产生,主要取决于MOSFET总门极电荷Qg、开关频率和IC工作电压Vcc,损耗大部分消耗在驱动电阻上。

因此,对于MOSFET的选取,在高频应用中,Rds (on) x Qg乘积数越低越有利于降低导通损耗和驱动损耗。应选择体积小、薄且散热性好的低热阻封装。由于氮化镓(GaN) MOSFET具有更优的Rds (on) x Qg参数,可额外增加约0.3%的满载效率,而在成本允许的情况下,GaN MOSFET是理想的选择。

2. 尖峰吸收电路损耗分析

尖峰吸收电路主要用于钳制MOS管Vds电压,防止其过压击穿。电阻-电容-二极管(RCD)吸收和瞬态电压抑制器(TVS)吸收是两种常用的电路,其中RCD最为常用,可靠性较高。

图3. 两种常见的尖峰吸收电路

对于RCD电路中,较大的吸收电容C可减少钳位电压纹波,但会增加待机功耗,所以C的选取一般以满载时5%至10%钳位电压纹波为宜。如果吸收电阻R较热,可减小变压器漏电感,选用Trr一致性好的慢管,可降低钳位电压,减少R损耗。

钳位电压方面,选择高的钳位电压可降低RCD吸收损耗,但需选高耐压MOS管,这会导致成本增加,而且变压器初级电流衰减速度会变快,次级整流电流上升斜率变陡,不利于EMI和次级同步整流效率优化。选择低的钳位电压,有利于EMI,次级同步整流控制,但RCD吸收损耗会增加。整流二极管D选用慢管可减少钳位电压和改善EMI,但二极管温升会较高。所以需综合考虑各方面影响,权衡择取。

3. 变压器损耗分析

变压器损耗主要包括磁芯损耗、线圈损耗和高频附加的磁芯及线圈损耗。对于>300 KHz应用,相比TP4A, 3C90或3F3,3C95/P51磁芯材料具有更低损耗。高频应用时,临近效应和趋肤效应导致绕线交流电阻增大,铜损增加,多股绞线将是非常不错的选择。

提高开关频率,可以减少变压器初级电感量,从而减少磁芯损耗。采用多股胶合线,减少趋肤效应,分开初级绕组(三明治绕法)以降低邻近效应。如安森美半导体的45 W参考设计选用RM7变压器,采用多股线加三明治绕法,初级端为24转25x AWG#38 绞合线,次级端为4转150x AWG#44 绞合线,采用3C90材料。

4. 输出整流损耗分析

输出整流通常有二极管整流和SR两种方案。由于SR MOS导通压降远低于二极管导通压降Vd,所以可比传统的二极管整流实现更高能效。

和初级MOSFET一样,SR损耗分为开关损耗(低压时可忽略不计)、驱动损耗(取决于Qg、开关频率及Vcc)和导通损耗。其中导通损耗包括MOSFET导通时的内阻损耗和体二极管在MOSFET导通前的导通损耗,体二极管导通损耗和MOSFET导通延时密切相关。安森美半导体的NCP4305/80系列同步整流控制IC具有极短导通延时,可调至30 ns,同时具有强大的驱动能力,能快速通断SR MOSFET。如在45 W参考设计中,SR MOSFET选用NVMFS6B03NL,内阻仅4 mΩ,Qg 70.7nC,若选用GaN SR MOSFET将可获得额外约0.3%的满载能效提升。

综上所述,损耗源及影响损耗的因素可归纳为:

表2. 损耗源及影响损耗的因素

45 W高功率密度适配器参考设计

该参考设计采用安森美半导体的NCP1340高频准谐振反激+NCP43080 SR架构, 在能效和待机功耗方面彰显出色性能,提供19 V/2.4 A额定输出,90-264 V宽输入电压,体积仅50 mm x 33 mm x 22 mm,所需外围元件数少,满载能效超过92%,待机功耗低于30 mW,完全符合CoC V5 Tier 2能效要求。

图4. 45 W参考设计能效 vs. 负载曲线

其中NCP1340/1采用SO-8封装,高压启动,集成X2放电和欠压检测,运行达6个谷底锁定开关,可有效地解决因谷底数不稳定所产生的音频噪声问题,并通过最小频率钳位和Quiet-Skip运行消除噪声。人类能听到的频率范围是20Hz至20kHz,早期的跳周期控制IC将最低开关频率设置在25 kHz,但间隙工作频率通常会在2 kHz至4 kHz范围,所以一旦其进入跳周期模式,噪声还是很大的。Quiet-Skip将最大的间隙工作频率设置为800 Hz,虽然800 Hz仍在可听见的范围内,但其往往会与背景噪声很好的融合,所以不容易被察觉。NCP1340/1采用跳周期模式,电流消耗低,因而可实现低于30 mW的低待机功耗,具有频率抖动特性,可提升EMI性能,实测抖频功能可降低AV曲线低频段的峰值约5 dB。此外,NCP1341比NCP1340多了功率倍增模式,可提高瞬态带载能力,同时保持最小尺寸的变压器,实现1.5倍或2倍的额定功率输出,非常适合打印机、驱动电源等需要损失功率倍增的应用场合。

总结

设计高功率密度的适配器电源不但要满足更轻更薄的发展趋势以提升用户体验,还要符合日趋严格的能效要求,这对设计人员来说充满挑战。高频准谐振反激是适用于低于65 W的高功率密度电源适配器的拓扑结构之一。安森美半导体的45 W高功率密度参考设计采用准谐振反激NCP1340/1 + 同步整流NCP4305/80的架构,可轻松设计出小巧、低成本的高能效高功率密度适配器,满载能效超过92%,待机功耗低于30 mW,远远超越能效规范。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>