- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

双向可控硅噪声抑制的基本原理和新的低成本的dV/dt性能改进解决方案

录入:edatop.com 点击:

作者: Muriel Nina和Laurent Gonthier

从上个世纪70年代开始,双向可控硅(又称三端双向晶闸管)一直用于控制交流负载,几乎在所有电器上都能看到双向可控硅。当终端设备上的电压上升速率过快时,双向可控硅将会自动触发,从那时起,设计人员就必须面对双向可控硅的这个特性。当设计对电压快速瞬变有要求的电器时,必须考虑这个问题。

半导体易受到dV/dt变化速率的影响

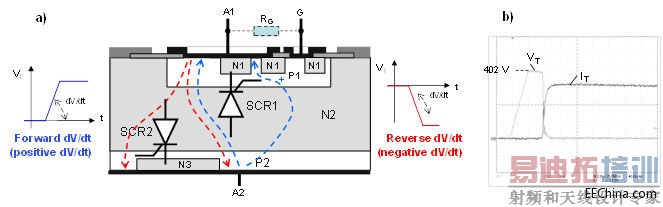

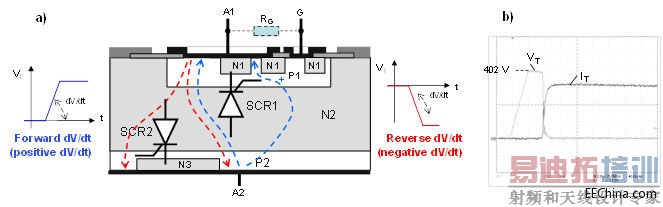

功率半导体器件由多个半导体层组成。例如,双向可控硅是四层结构交流开关元件,每层是半个祼片,每层通过交替掺杂方法控制空穴浓度(P区)或自由电子浓度(N区),形成两个单向可控硅。因此,双向可控硅相当于两个反极性并联的单向可控硅(图 1)。

每个PN结都会产生寄生电容,当施加斜坡电压时,就会产生电容电流(ICAP)。电容电流可能会向IGBT或功率MOSFET等电压控制型半导体的栅极电容充电。如果电容电压持续升高,超过阈压(VGS(th)或VGE(th)),器件可能会导通。即使不足以触发器件,器件也可能进入饱和模式(如果是MOSFET)或线性模式(如果是IGBT),导致功率损耗过大和器件失效。为避免这个问题,栅极必须通过低阻抗以源极或发射极为参考点。

图1:a)双向可控硅结构易受dV/dt上升率影响 b) dV/dt上升率引起导通示例图

如果dV/dt(以A1端为参考点)为正值,则电流ICAP经P1-N1结流至A1;如果dV/dt为负值,则电流ICAP经P2-N3结流至A2(如图1所示)。假如P1或P2层电压分别高于P1-N2或P2-N3结阈压(即0.6 V),该电容电流就可能导致双向可控硅导通。

在双向可控硅产品数据手册中,厂商给出相关器件在导通前能够承受的最小的dV/dt上升速率。如果电压上升速率高于这个数值,双向可控硅可能就会导通,如图1b所示。只要施加的电流小于器件最大输入电流,dV/dt引起的导通不会损坏双向可控硅。因为当双向可控硅导通时,电流会受到负载阻抗限制,所以大多数情况下不会损坏双向可控硅。

改进双向可控硅的dV/dt特性

为避免当双向可控硅输入端上电压变化速率过快而引起的导通问题,传统解决方案是给双向可控硅并联一个阻容缓冲电路,抑制市电的dV/dt变化速率。但是,这些电路需要一个大型电容,以耐受高达400V的峰压(连接220-240V市电)。

第二种解决方案是在栅极和阴极之间增加阻抗,即增加一个电阻器(图1中的RG )。如图1所示,这个解决方案只适用于正电压dV/dt变化的情况,寄生电容电流在P1-N1结分流(见蓝色虚线ICAP),防止开关被触发。对于负电压dV/dt情况,电容电流(图1a中的红色虚线)流向P2-N3结。外部器件无法分流这部分电流,因而无法改进反向dV/dt抑制功能。

用电容替代电阻(图1中的RG )也可以解决这个问题,虽然这个办法在SCR(可控硅整流管)中效果很好,但是不建议用于双向可控硅,因为双向可控硅导通时dI/dt速率很高,这个电容可能会在双向可控硅栅极上产生过流,导致器件损毁。

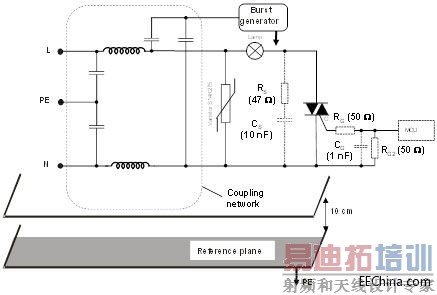

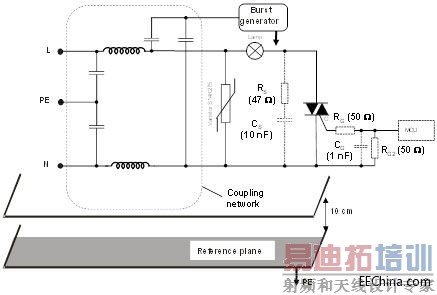

为防范这种风险,可以给该电容串联一个电阻(图2a中的RG 和CG),这样做的好处是使用一个低阻值的RG,同时避免了从控制电路分流过高的电流,因为只要充电,CG 相当于开路。

栅极阻容滤波器有益于提高应用抗干扰能力

家电电器必须达到电磁兼容性标准的最低要求。因为双向可控硅通过负载直接连接市电,这类电器对IEC61000-4-4标准中的电快速瞬变(EFT)实验所用瞬变事件特别敏感。

IEC61000-4-4实验条件包括耦合到市电网络的5 kHz或100 kHz电压脉冲串。因为该实验是在整个被测电器上进行,所以微控制器也可能受到电磁干扰。我们在实验中只评测双向可控硅的抗扰度,所以将其栅极直接连至其参考电极,使双向可控硅不受其它干扰的影响(图2)。

图2:IEC61000-4-4测试配置

输入变阻器用于钳制电压,防止击穿导致双向可控硅导通。假如没有输入变阻器,只要施加1 kV峰压,任何双向可控硅都会导通。我们使用一个白炽灯作为负载,以便于观察双向可控硅何时导通。例如,我们测试了几款意法半导体的T系列产品(T610T-8FP, T810T-8FP, T1210T-8FP, T1610T-8FP)。每款产品的栅电流都是10 mA,都对EFT(电快速瞬变)噪声敏感。通过图2中的RG-CG-RG2电路,每款产品都能承受3 kV 5 Khz脉冲或2 kV 100 Khz脉冲。如果没有这个栅极电路,连1 kV的脉冲都承受不住。RG2 对应微控制器输出引脚的内部RDS(ON)电阻,无需增加外部电阻。

与传统缓冲电路(图2中的RS和CS)相比,栅极电路所能承受的电压略高(3.6 kV 对 3.3 kV 典型值)。栅极电路只用一个16V 的小电容器就取得了400V大电容器的抗扰性能。栅极电路与缓冲电路配合,让只使用10 mA双向可控硅的电器取得高于6 kV的EFT抗扰性能。栅极电路能够让所有的双向可控硅受益,不过,意法半导体T系列产品本身的负电压dV/dt性能非常优异,同时再使用外部栅极电路提高正电压dV/dt性能。

总之,用栅极滤波器代替高压缓冲器也可以降低电路板尺寸和成本,此外,还可以滤除从市电网络进入到控制电路的噪声。

从上个世纪70年代开始,双向可控硅(又称三端双向晶闸管)一直用于控制交流负载,几乎在所有电器上都能看到双向可控硅。当终端设备上的电压上升速率过快时,双向可控硅将会自动触发,从那时起,设计人员就必须面对双向可控硅的这个特性。当设计对电压快速瞬变有要求的电器时,必须考虑这个问题。

半导体易受到dV/dt变化速率的影响

功率半导体器件由多个半导体层组成。例如,双向可控硅是四层结构交流开关元件,每层是半个祼片,每层通过交替掺杂方法控制空穴浓度(P区)或自由电子浓度(N区),形成两个单向可控硅。因此,双向可控硅相当于两个反极性并联的单向可控硅(图 1)。

每个PN结都会产生寄生电容,当施加斜坡电压时,就会产生电容电流(ICAP)。电容电流可能会向IGBT或功率MOSFET等电压控制型半导体的栅极电容充电。如果电容电压持续升高,超过阈压(VGS(th)或VGE(th)),器件可能会导通。即使不足以触发器件,器件也可能进入饱和模式(如果是MOSFET)或线性模式(如果是IGBT),导致功率损耗过大和器件失效。为避免这个问题,栅极必须通过低阻抗以源极或发射极为参考点。

图1:a)双向可控硅结构易受dV/dt上升率影响 b) dV/dt上升率引起导通示例图

如果dV/dt(以A1端为参考点)为正值,则电流ICAP经P1-N1结流至A1;如果dV/dt为负值,则电流ICAP经P2-N3结流至A2(如图1所示)。假如P1或P2层电压分别高于P1-N2或P2-N3结阈压(即0.6 V),该电容电流就可能导致双向可控硅导通。

在双向可控硅产品数据手册中,厂商给出相关器件在导通前能够承受的最小的dV/dt上升速率。如果电压上升速率高于这个数值,双向可控硅可能就会导通,如图1b所示。只要施加的电流小于器件最大输入电流,dV/dt引起的导通不会损坏双向可控硅。因为当双向可控硅导通时,电流会受到负载阻抗限制,所以大多数情况下不会损坏双向可控硅。

改进双向可控硅的dV/dt特性

为避免当双向可控硅输入端上电压变化速率过快而引起的导通问题,传统解决方案是给双向可控硅并联一个阻容缓冲电路,抑制市电的dV/dt变化速率。但是,这些电路需要一个大型电容,以耐受高达400V的峰压(连接220-240V市电)。

第二种解决方案是在栅极和阴极之间增加阻抗,即增加一个电阻器(图1中的RG )。如图1所示,这个解决方案只适用于正电压dV/dt变化的情况,寄生电容电流在P1-N1结分流(见蓝色虚线ICAP),防止开关被触发。对于负电压dV/dt情况,电容电流(图1a中的红色虚线)流向P2-N3结。外部器件无法分流这部分电流,因而无法改进反向dV/dt抑制功能。

用电容替代电阻(图1中的RG )也可以解决这个问题,虽然这个办法在SCR(可控硅整流管)中效果很好,但是不建议用于双向可控硅,因为双向可控硅导通时dI/dt速率很高,这个电容可能会在双向可控硅栅极上产生过流,导致器件损毁。

为防范这种风险,可以给该电容串联一个电阻(图2a中的RG 和CG),这样做的好处是使用一个低阻值的RG,同时避免了从控制电路分流过高的电流,因为只要充电,CG 相当于开路。

栅极阻容滤波器有益于提高应用抗干扰能力

家电电器必须达到电磁兼容性标准的最低要求。因为双向可控硅通过负载直接连接市电,这类电器对IEC61000-4-4标准中的电快速瞬变(EFT)实验所用瞬变事件特别敏感。

IEC61000-4-4实验条件包括耦合到市电网络的5 kHz或100 kHz电压脉冲串。因为该实验是在整个被测电器上进行,所以微控制器也可能受到电磁干扰。我们在实验中只评测双向可控硅的抗扰度,所以将其栅极直接连至其参考电极,使双向可控硅不受其它干扰的影响(图2)。

图2:IEC61000-4-4测试配置

输入变阻器用于钳制电压,防止击穿导致双向可控硅导通。假如没有输入变阻器,只要施加1 kV峰压,任何双向可控硅都会导通。我们使用一个白炽灯作为负载,以便于观察双向可控硅何时导通。例如,我们测试了几款意法半导体的T系列产品(T610T-8FP, T810T-8FP, T1210T-8FP, T1610T-8FP)。每款产品的栅电流都是10 mA,都对EFT(电快速瞬变)噪声敏感。通过图2中的RG-CG-RG2电路,每款产品都能承受3 kV 5 Khz脉冲或2 kV 100 Khz脉冲。如果没有这个栅极电路,连1 kV的脉冲都承受不住。RG2 对应微控制器输出引脚的内部RDS(ON)电阻,无需增加外部电阻。

与传统缓冲电路(图2中的RS和CS)相比,栅极电路所能承受的电压略高(3.6 kV 对 3.3 kV 典型值)。栅极电路只用一个16V 的小电容器就取得了400V大电容器的抗扰性能。栅极电路与缓冲电路配合,让只使用10 mA双向可控硅的电器取得高于6 kV的EFT抗扰性能。栅极电路能够让所有的双向可控硅受益,不过,意法半导体T系列产品本身的负电压dV/dt性能非常优异,同时再使用外部栅极电路提高正电压dV/dt性能。

总之,用栅极滤波器代替高压缓冲器也可以降低电路板尺寸和成本,此外,还可以滤除从市电网络进入到控制电路的噪声。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:联捷穿墙式接线端子内部和外部接线单元一般采用框式压线技术/也可采用弹簧连接技术

下一篇:正负电源基础知识以及如何符合双向可控硅触发要求

射频和天线工程师培训课程详情>>