- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

设计超低功耗的嵌入式应用:简化电源域

录入:edatop.com 点击:

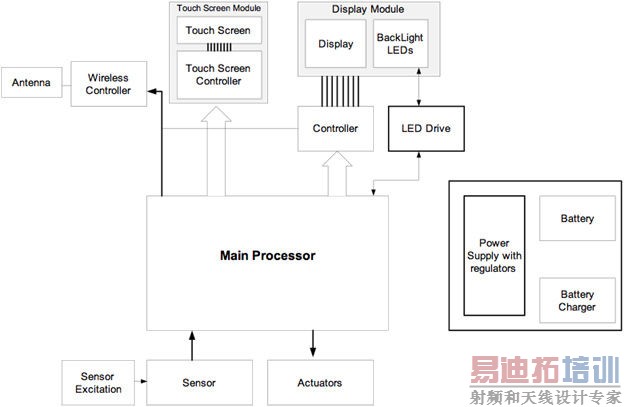

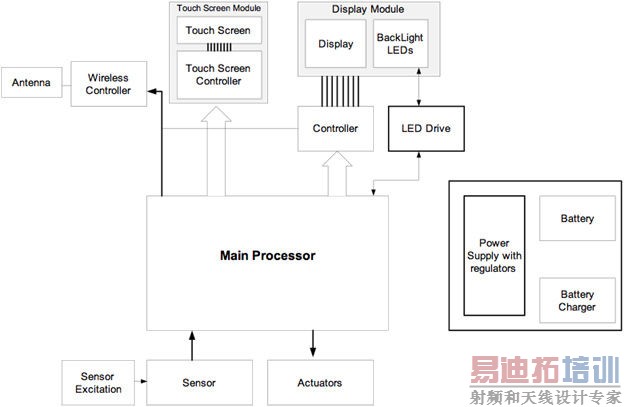

不是所有便携式系统都像图1(参见本系列文章的第二部分)所示的系统这么简单。图3给出了可穿戴电子设备的典型方框图。由于存在大量功能块和子系统,设计复杂性进一步提高。

图3:手表的高层次方框图

一个符合逻辑的办法是将整个系统拆分为不同的子系统,并分析各个子系统的功耗。这也有助于简化电源域的设计,从而实现低功耗功能。

显示和触摸控制器部分的功耗主要取决于背光驱动和显示屏本身。大多数设计都针对显示屏采用基于定时器的超时断电模式。一般说来,在固定时间T1后,背光会降至50%的占空比,又过了时间T2后,显示屏会完全关闭。这时即使是触摸控制器也可被关闭或进入断电模式,具体取决于使用情境。这样,设计人员就可绘制这个功能块的电流曲线,进而获得典型电流。

无线控制器(如面向蓝牙的控制器)通常是低功耗的。这种控制器能通过一定方式在高低功耗模式之间切换。无线控制器数据表中的典型数值是我们在不对系统性能分析情况下能获得的最贴近的功耗估算数据。不过我们要记住考虑到器件在不同电源模式之间的占空比。

传感器电流主要取决于激励电流和模拟前端(AFE)的功耗。赛普拉斯的PSoC 4等器件拥有ADC等内置模拟功能和其它AFE组件,这就使得设计人员能通过固件命令给不同的功能块动态断电。这种控制和精细粒度级别可进一步提高低功耗设计的效率。

对涉及多控制器和多工作模式的复杂设计而言,在电源电路设计时要注意适应不同的可控电源域。这样,一个待机电源域上的单个控制器就能有效控制其它域。这种架构或许成本会比较高,但却能保持非常低的功耗。

在明确各个子部分后,可采用以下几种方法对每个子部分进行功耗优化:

1. 关闭调节器以关闭整个子部分

2. 将不使用的外设进行断电

3. 使用微控制器的低功耗模式降低平均功耗

实现低功耗的最有效方法就是关闭用于向给定子部分供电的调节器。如果某个特殊的子部分不需要长期可用,其功能不具备时间关键性,那么其调节器自身可被主机控制器控制。传感器就是一个很好的子系统例子,当系统不运行时可将其关闭。唯一消耗的漏电流将会是调节器的电流。

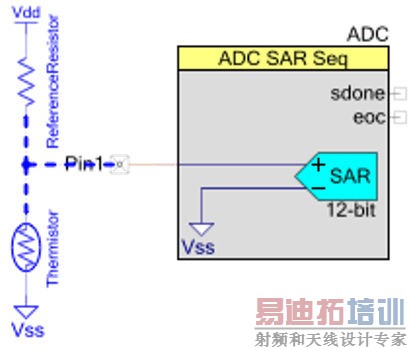

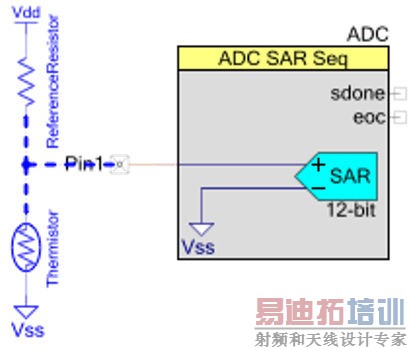

如果不能将整个子部分断电,那么可考虑子部分的各个外设和组件。举例来说,在传感器部分中,可能有些传感器需要继续测量,有些则不需要。假设有一个测量温度的热敏电阻、一个加速计和一个IR传感器。加速计需要频繁检查是否有活动情况,系统的其余部分需要据此实现唤醒。与此形成对比的是,温度传感器和 IR传感器大多数时间并不需要工作。下面让我们谈谈热敏电阻的激励(见图4)。在本例中,无论是否进行测量,电流都会通过热敏电阻和参考电阻。

图4:典型的热敏电阻激励电路

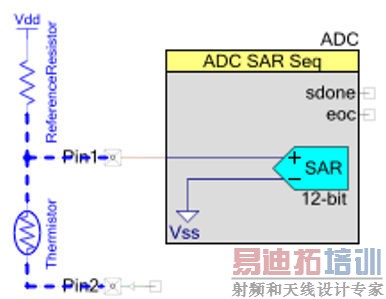

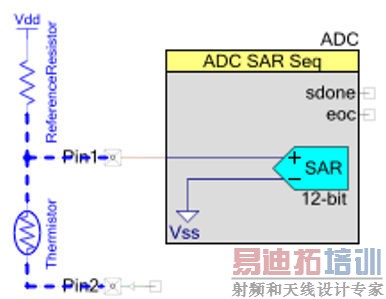

现在,如果如图5所示修改热敏电阻电路,那么当传感器不被采样时就能避免电流消耗。

图5:面向低功耗的热敏电阻激励

在本例中,引脚配置为强输出模式(CMOS逆变器)。要测量传感器输出时就将引脚驱动到低电平。这会使热敏电阻通过NMOS晶体管连接到Vss。唯一需要考虑的额外电阻就是NMOS晶体管的导通电阻,该电阻基本非常低。当不需要测量传感器输出时,则将引脚驱动到高电平。这会使热敏电阻连接到Vdd,从而实现传感器电路上的电流为零。

由于加速计也不需要随时被采样,因此ADC和其它模拟组件(如运算放大器或模拟信号链中的参考生成器)可在不需要检测信号时进行断电。

采用SoC实现此电路时,还有许多其它方法来降低功耗,我们下面将加以介绍。设想一下图3所示的系统,LCD控制器可进入冬眠模式而主机处理器在感应到I2C命令时可将其唤醒。在采用PSoC 4实现电路的情况下,功耗可低至20 nA。

同样,如果传感器子部分用低功耗模式实现且将关闭所有元件,则MCU可在有运动情况下用比较器中断唤醒。加速计输出可连接到比较器,确保只要一有运动就能唤醒器件,并触发主机处理器的事件。

就基于SoC构建的系统而言,还可采用其它技术来降低平均功耗。举例来说,所有外设的时钟都可设定为最慢的时钟频率,由于动态功耗与开关频率成正比,因此这么做就能节约耗电。再举例来说,SoC中的ADC的时钟频率通常应与所需的采样率成正比。如果ADC设置的采样率高于实际的系统需求,那就会造成不必要的电池负载。

还有其它一些系统级技巧可用来降低整体功耗。举例来说,器件输出可支持较低转换率以降低辐射。不过,较低转换率会导致FET的引脚驱动级消耗更多电流,因为PMOS和NMOS都会开启更长的时间。根据系统允许的辐射量,引脚的转换率高低可进行调节设置。

我们选择的器件如果能提供多种电源模式,而且能实现较高集成度,并对SoC的电源状态实现较好控制,这就能简化低功耗系统的实现过程。根据应用的不同,我们可有效利用不同的电源模式来确保较低的平均电流。虽然时钟频率较高会导致高功耗,但CPU暂时高频工作随后能更快地让器件返回休眠状态,这其实有助于实现更低的平均功耗。开发人员应考虑整体系统,尽可能避免出现漏电流路径。

图3:手表的高层次方框图

一个符合逻辑的办法是将整个系统拆分为不同的子系统,并分析各个子系统的功耗。这也有助于简化电源域的设计,从而实现低功耗功能。

显示和触摸控制器部分的功耗主要取决于背光驱动和显示屏本身。大多数设计都针对显示屏采用基于定时器的超时断电模式。一般说来,在固定时间T1后,背光会降至50%的占空比,又过了时间T2后,显示屏会完全关闭。这时即使是触摸控制器也可被关闭或进入断电模式,具体取决于使用情境。这样,设计人员就可绘制这个功能块的电流曲线,进而获得典型电流。

无线控制器(如面向蓝牙的控制器)通常是低功耗的。这种控制器能通过一定方式在高低功耗模式之间切换。无线控制器数据表中的典型数值是我们在不对系统性能分析情况下能获得的最贴近的功耗估算数据。不过我们要记住考虑到器件在不同电源模式之间的占空比。

传感器电流主要取决于激励电流和模拟前端(AFE)的功耗。赛普拉斯的PSoC 4等器件拥有ADC等内置模拟功能和其它AFE组件,这就使得设计人员能通过固件命令给不同的功能块动态断电。这种控制和精细粒度级别可进一步提高低功耗设计的效率。

对涉及多控制器和多工作模式的复杂设计而言,在电源电路设计时要注意适应不同的可控电源域。这样,一个待机电源域上的单个控制器就能有效控制其它域。这种架构或许成本会比较高,但却能保持非常低的功耗。

在明确各个子部分后,可采用以下几种方法对每个子部分进行功耗优化:

1. 关闭调节器以关闭整个子部分

2. 将不使用的外设进行断电

3. 使用微控制器的低功耗模式降低平均功耗

实现低功耗的最有效方法就是关闭用于向给定子部分供电的调节器。如果某个特殊的子部分不需要长期可用,其功能不具备时间关键性,那么其调节器自身可被主机控制器控制。传感器就是一个很好的子系统例子,当系统不运行时可将其关闭。唯一消耗的漏电流将会是调节器的电流。

如果不能将整个子部分断电,那么可考虑子部分的各个外设和组件。举例来说,在传感器部分中,可能有些传感器需要继续测量,有些则不需要。假设有一个测量温度的热敏电阻、一个加速计和一个IR传感器。加速计需要频繁检查是否有活动情况,系统的其余部分需要据此实现唤醒。与此形成对比的是,温度传感器和 IR传感器大多数时间并不需要工作。下面让我们谈谈热敏电阻的激励(见图4)。在本例中,无论是否进行测量,电流都会通过热敏电阻和参考电阻。

图4:典型的热敏电阻激励电路

现在,如果如图5所示修改热敏电阻电路,那么当传感器不被采样时就能避免电流消耗。

图5:面向低功耗的热敏电阻激励

在本例中,引脚配置为强输出模式(CMOS逆变器)。要测量传感器输出时就将引脚驱动到低电平。这会使热敏电阻通过NMOS晶体管连接到Vss。唯一需要考虑的额外电阻就是NMOS晶体管的导通电阻,该电阻基本非常低。当不需要测量传感器输出时,则将引脚驱动到高电平。这会使热敏电阻连接到Vdd,从而实现传感器电路上的电流为零。

由于加速计也不需要随时被采样,因此ADC和其它模拟组件(如运算放大器或模拟信号链中的参考生成器)可在不需要检测信号时进行断电。

采用SoC实现此电路时,还有许多其它方法来降低功耗,我们下面将加以介绍。设想一下图3所示的系统,LCD控制器可进入冬眠模式而主机处理器在感应到I2C命令时可将其唤醒。在采用PSoC 4实现电路的情况下,功耗可低至20 nA。

同样,如果传感器子部分用低功耗模式实现且将关闭所有元件,则MCU可在有运动情况下用比较器中断唤醒。加速计输出可连接到比较器,确保只要一有运动就能唤醒器件,并触发主机处理器的事件。

就基于SoC构建的系统而言,还可采用其它技术来降低平均功耗。举例来说,所有外设的时钟都可设定为最慢的时钟频率,由于动态功耗与开关频率成正比,因此这么做就能节约耗电。再举例来说,SoC中的ADC的时钟频率通常应与所需的采样率成正比。如果ADC设置的采样率高于实际的系统需求,那就会造成不必要的电池负载。

还有其它一些系统级技巧可用来降低整体功耗。举例来说,器件输出可支持较低转换率以降低辐射。不过,较低转换率会导致FET的引脚驱动级消耗更多电流,因为PMOS和NMOS都会开启更长的时间。根据系统允许的辐射量,引脚的转换率高低可进行调节设置。

我们选择的器件如果能提供多种电源模式,而且能实现较高集成度,并对SoC的电源状态实现较好控制,这就能简化低功耗系统的实现过程。根据应用的不同,我们可有效利用不同的电源模式来确保较低的平均电流。虽然时钟频率较高会导致高功耗,但CPU暂时高频工作随后能更快地让器件返回休眠状态,这其实有助于实现更低的平均功耗。开发人员应考虑整体系统,尽可能避免出现漏电流路径。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:详解开关电源拓扑结构优缺点

下一篇:设计超低功耗的嵌入式应用:五种电源模式详解

射频和天线工程师培训课程详情>>