- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

提高同步整流应用的系统效率和功率密度

录入:edatop.com 点击:

吉时利公司

随着功率电源技术和信息技术的发展,用户对高效率小体积产品的要求越来越高,对电源的性能也相应提出了更为苛刻的规范要求,电源市场迎来巨大的商机,同时也迎来了巨大的挑战。本次报告包括以下几项内容:系统效率和功率密度的重要性,行业发展的趋势以及相应的解决方案,电源设计中面临的挑战,需要更高系统效率和功率密度的一些典型应用,以及在选用飞兆半导体采用屏蔽技术的中等电压Power Trench MOSFET后可实现更高系统效率和功率密度。

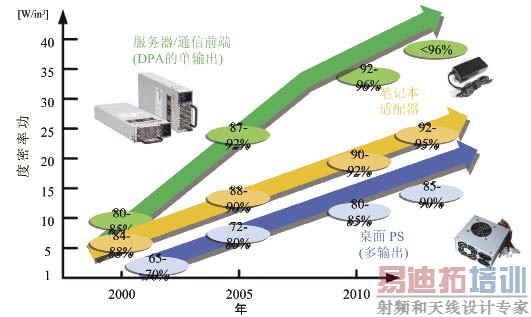

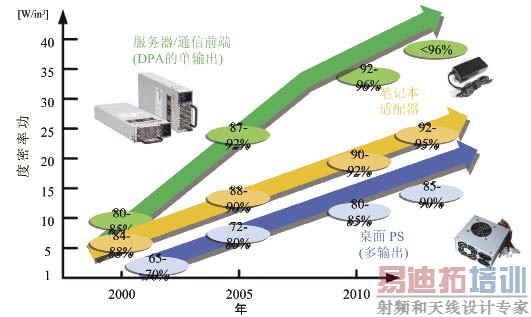

基于系统效率和功率密度发展趋势示意图,我们可以清晰的看出,在最近的十年间系统的效率和功率密度有了巨大的提升,尤其以服务器和通信电源为显著。这一巨大的提升是如何实现的呢?它主要是通过尝试新的拓扑结构,引进新技术高性能的功率器件,同时通过良好的系统设计来保证,以上几点我们会在接下来的内容中给出进一步的讨论。

系统效率和功率密度的重要性

为了说明系统效率和功率密度的重要性,我们以通信网络能耗增长为例做简要介绍。自2009年开始,通信网络每年的能耗百分比都以线性上升,到2016年这一数字将翻番,这彰显了系统的效率和功率密度对于工业应用是多么重要。

随着对电源系统效率和功率密度不断提高的行业发展趋势,各个国家和地区针对自己的具体情况开发并颁布了一系列新的标准以适应本国情况,例如美国的能源之星、欧盟的生态标准以及中国的CSC标准。电源行业针对这些新的要求,通过提高系统效率,增加功率密度及降低能源成本的方式来达到新标准的要求。

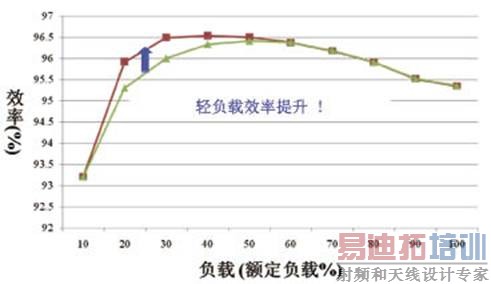

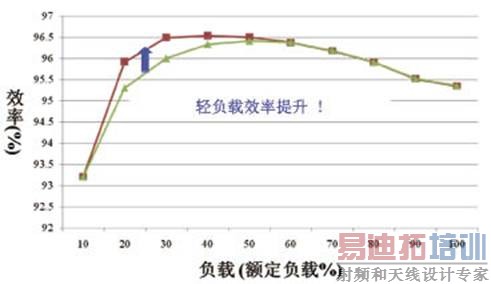

针对于服务器应用和通信应用的高性能电源,在设计过程中有以下三个指标尤为重要:一、如何提高系统的功率密度,二、如何提高系统轻载下的效率,三、如何实现长系统寿命下的高可靠性。图片所示是在原系统基础上改用飞兆半导体中等电压Power Trench MOSFET后在轻载25%状态下效率有明显的提高,大约1%左右。

系统效率和功率密度发展趋势示意图

飞兆半导体应用解决方案

针对目前高性能电源设计中的难点,飞兆半导体的解决方案可以帮助客户降低系统的RDS(ON),减少系统的传导损耗,减少系统的开关噪声,以及减少系统的热耗散,从而使得单位面积做到最小。除了通信电源以及服务器电源之外,需要更高效率和功率密度的应用还有很多,例如ATX电源以及专事转换器、VRM模块、D类音频放大器以及马达驱动等。

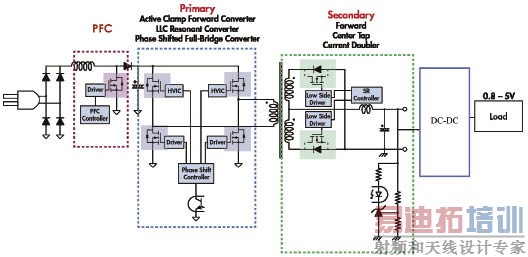

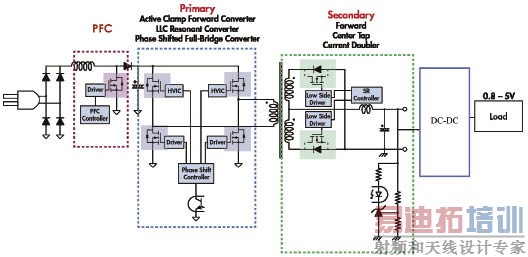

这里我们首先以AC-DC同步整流应用为例。在通讯电源的应用中它的主功率部分主要由功率校正电路、原边的电源转换电路、副边的整流电路组成,我们可以很清楚的看到,在图中有非常多的功率器件,系统的效率也就由这些功率器件的工作效率以及本身的性能优劣决定。

在服务器中隔离型或非隔离型DC-DC电路的应用,我们可以用方框图来描述。在下方蓝色图中是一典型的服务器电源的组成架构,它由原边、副边以及非隔离型的DC-DC电路组成。如通信电源一样,在其中有非常多的功率器件来实现电流、电压的转换电路,使系统的效率高低以及功率密度可以做的好坏和功率器件的选择有着直接和密不可分的关系。在以上描述的功率转换电路中,选择飞兆半导体采用屏蔽栅极技术的中等电压Power Trench MOSFET之后,可以实现系统的更高效率和更高的功率密度。

屏蔽栅极技术

这里我们对沟槽型功率MOS管的发展做一个简单的回顾。左边是传统沟槽型MOSFET的典型结构,与前期的平面结构的MOS管相比,它具有更低的RDS(ON)以及更好的开关特性。经过一段时间的发展,底部有厚氧化层的沟槽型MOS管替代了传统的沟槽型MOS管,它可以减少外延层的寄生电阻,得到更低的RDS(ON)。在采用屏蔽栅极技术的Power Trench MOSFET技术之后,可以使功率MOS管具有更高的单元密度,同时在采用电荷平衡技术之寄生电阻后,可以更加有效的减少Epi电阻,从而更大程度的减小了寄生电阻的阻值,以及提高了开通与关断的特性。

在使用了飞兆半导体Power Trench结构功率MOS管之后效能是如何提高的呢?我们以一台1000W的通信电源为平台做一些产品的对照比较。在使用了飞兆半导体FDH055N15A之后,效能提升可以从最小0.2%到超过0.5%,也就是可以有最高5W的功率提升,可以从图中看出,蓝色线是使用了飞兆半导体的功率器件,红色线是竞争对手的5.9mΩ的一颗150V的相同规格的MOS管的测试曲线。

与竞争对手的Power Trench 结构功率MOS管相比,飞兆半导体屏蔽栅极技术的MOS管在同步整流的运用下有明显的优势。如图中所示,飞兆半导体的FDP036N10A与竞争对手最好的MOS管相比,在Qg值上仍然比竞争对手低10%以上。我们可以读出它的数据,飞兆半导体的FDP036N10A的Qg值是58.7,而竞争对手最好的MOS管也要达到76.2。

系统轻负载效率比较

AC-DC同步整流应用

同步整流中的驱动损耗

从左边测试曲线可以看出,在导通期间内电流从源极到漏极流过MOSFET沟道,并在死区时间流过体二极管,由于在开关瞬变期没有电压穿过同步开关,所以这里不会发生“密勒效应”,在栅-源电压上没有过渡平台。再看右边的曲线图,红色线为没有了“密勒效应”的驱动波形,可以看到它的时间相对传统MOS管的时间有着明显的缩短。

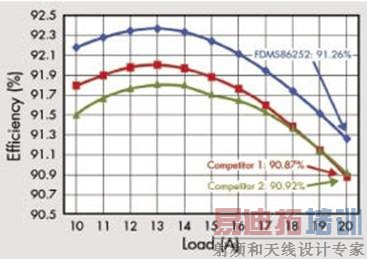

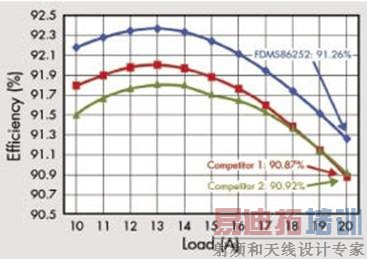

在针对隔离型和非隔离型DC-DC应用中如何提高效能,我们基于一款1/16砖的平台上做了一系列的比较试验。在采用了飞兆半导体FDMS86252与主要竞争对手产品比较,效率提升范围最小为0.4%,最大为超过1%,也就是有0.32W的功率提升,从图中可以看出,上面的曲线为采用了飞兆半导体FDMS86252的测试曲线。

众所周知低的RDS(ON)可以提高系统效能以及功率密度,这里我们针对芯片级对RDS(ON)的贡献做出分析。在比较每一串联电阻对低电压部分和高电压部分的贡献率时,可以看到,当Vg=10V、单位电流密度为200A/cm2时,外延层的电阻占的比例至关重要。在30V的VDS时,外延层的电阻只占29%,但当VDS上升到100V时,外延层的电阻将占到整个RDS(ON)的78%。所以现今在高压MOSFET上所做的大部分开发工作,都正在转向如何减少漂移区的EPI电阻。

现今如要满足行业的标准,就必须要提高设计的效率以及增加功率密度。飞兆半导体的屏蔽栅极功率MOSFET中,在5X6mm尺寸内最低RDS(ON)最大值可以做到2.5mΩ,典型值为60V的击穿电压。如右图所示,屏蔽栅极功率MOS管的击穿参数除传统的参数Cds、Cgs和Cgd之外,这里增加了CG屏蔽层以及CD屏蔽层,CG屏蔽层以及CD屏蔽层的电容作用会在后边给出解释。

飞兆半导体领先的RDS(ON)性能

基于飞兆半导体屏蔽栅极技术所提供的RDS(ON)性能,从图中可以读出,飞兆半导体屏蔽栅极技术功率MOS管测试点都在竞争对手的下边,也就是说在相同的测试条件下,飞兆半导体屏蔽栅极技术可以提供更低的RDS(ON)性能。

在选用飞兆半导体屏蔽栅极功率MOS管后,功率密度又是怎么增加的呢?我们基于AC-DC同步整流应用做一简单介绍。在选用飞兆半导体屏蔽栅极功率MOS管后,可以有效减少电压尖峰,其结果是可以使设计者选用更低额定电压的MOSFET,同时大多数应用都无需外部缓冲器。在相同测试条件下,使用飞兆半导体屏蔽栅极功率MOS管后电压尖峰可以比对手的小10%以上。

隔离型或非隔离型DC-DC的应用

同步整流中的电压尖刺损耗

在同步整流中,与器件相关的主要参数是MOS管的体二极管的柔和程度,针对于飞兆半导体屏蔽栅极功率MOS管而言,这一特性会比竞争对手更好,也就是我们定义体二级管恢复时间的TB/TA为软恢复特性,当这特性较软时,意味着同步整流中的电压尖刺可以被有效降低,其结果是可以省去缓冲器电路,或者用较低额定电压MOS管替换较高额定电压的MOS管。

屏蔽栅极技术的优势

可以带来优良的体二极管性能,而优良的体二极管性能又可以带来软反向恢复特殊和低电压尖刺,下三图是实测结果。左面是使用了飞兆半导体屏蔽栅极技术的体二极管反向恢复特性,最高毛刺电压仅有56.8V,中间图是和竞争对手最好的MOS管相比,它的方向尖峰电压仍然到63.32V。

对于隔离型或非隔离型DC-DC的应用中,在考虑到线路板空间更小,又需要增加功率密度时,我们推荐Power56的封装形式,而非D2PAK或其他封装模式。在使用了飞兆半导体屏蔽栅极功率MOS管后,可以减少开关节点的振铃现象,同时由于屏蔽栅极功率MOS管固有的电子和电容,可以实现内置的漏极到源极的缓冲电路,从而在大多数应用都无需外部缓冲电路。

与传统的Power Trench 功率MOS管相比,屏蔽栅极技术有着独特的优势。屏蔽栅极技术MOS管可以减少QGD,减少QGD带来的结果是可以拥有非常优良的开关特性及较低的振铃现象,较低的振铃现象又可以使多数情况下无需外接缓冲电路。通过比较我们可以看到,采用飞兆半导体屏蔽栅极功率MOS管后产生的振铃不到竞争对手的一半。

现在对电源系统的高能耗成本做系统分析。以服务器机架电源成本为例,预计2011年服务器数量将达到870万台,每台服务器的额定电源为4X2KW/h,即8KW/h,而每个机架有8台服务器,就是有大约100万个服务器机架,乘以8KW/h后得到额定功率为800万KW/h,以每KW/h价格0.15美元计算,最后得到成本为120万美元。对应如此高的能源成本,我们只能通过提高电源效率、提高功率密度,来节约电源的高能耗成本。

现在看看系统选用飞兆半导体的高成本效益电源之后会有什么变化。我们选用Power56技术封装的屏蔽栅极MOS管FDMS86500L,它可以使整机效率提高约1%,即每个电源每小时节电20W,每个服务器机架每年节电800W,每个服务器机架每年可以节省105美元,考虑到全部服务器机架数量为100万台,这样总体每年可以节省约11.4亿美元。这里我们可以看到,提高效率可以大幅节省成本,而提高功率密度又可以提供占位更小的解决方案,从而进一步节省成本。

总结

对于功率电源领域的发展趋势而言,更高的系统效率以及更高的功率密度已经成为各大公司及其设计人员所要达到的首要目标。根据这一系列的高要求,飞兆半导体推出了一系列的高性能的屏蔽栅极功率MOS管,可以很好的帮助设计人员解决效率以及功率密度的问题。飞兆半导体屏蔽栅极功率MOS管针对通信电源、服务器电源以及DC-DC同步整流电路,可以提高效率和功率密度,对于飞兆半导体屏蔽栅极功率MOS管的特点而言,具有低的Qg、软的体二极管的恢复特性以及极低的RDS(ON),以上特性均可以对系统的效率以及功率密度产生相当的贡献。

问答选编

问:3061之类的应该都是隔离过零驱动吧?

答:moc302x 系列

问:电压最好降额80%来使用,额定100V的管子用在20V的电路里比较安全,还是用在80V的电路里比较安全?

答:100V的管子,在系统稳态暂态各种工作条件下,电压不要超过80V,比较理想。

问:MOS当二极管用,中间的管脚必须要剪断吗?为什么不直接用二极管呢?

答:不用。二极管的压降在1V左右,如果输出电压很低,比如5V,这时候对效率影响很大,这时就需要同步整流。

问:MOS管在高速开关时产生的辐射主要是传导的还是辐射的?应该如何去除此种EMI

答:传导会是主要的,尽量减小回路,同时加吸收回路。

问:MOS管在什么情况下最容易损坏,之前有个电源的MOS击穿了,最后厂家解释说是电容里的静电或人体静电,通过MOS管卸放,击穿MOS管,这可能吗?

答:通过MOS管卸放也有可能击穿MOS的,所以操作人员要带防静电设备

问:Power Trench MOSFET的热特性和保护性能如何 使用时是否需要加散热器

答:Trench技术可以提高效率,以此减小发热,因此热特性会好一些。是否加散热器要根据具体应用来决定。MOS本身没有保护线路,因此需要工程师在设计时考虑裕量

问:Power Trench MOSFET的主要封装形式有哪几种?

答:这个从贴片到直插的一些常用封装都是有的。TO220, TO263, Power56等

问:Power Trench MOSFET的主要优势是什么

答:1.减小导通电阻Rdson;2.提高开关性能;3 Bodydiode的软恢复性能

问:采用PFC电路,是否有助于提高电源效率 为什么

答:采用PFC不会提高系统效率,反而会降低效率,因为PFC会增加元器件,反而会增加损耗。但是有了PFC,你的功率因数会提高,这样即使效率低一些,反而会省电。用电量=实际使用的电量/功率系数。

问:采用Power Trench MOSFET,效率能提高多少

答:采用Trench技术,中低压MOS的导通阻抗通常会小20~30%,考虑到开通损耗,综合效率可以提高20%左右。

问:产品的产地在哪里,供货周期一般是多久?

答:我们的封装工厂分布在苏州,马来西亚和菲律宾。TO-220的产品大多在苏州生产。供货周期通常在8-12周。

问:从频率特性和热特性以及封装成本来看, 采用那种封装的Power Trench MOSFET较优

答:从频率特性来看,一般贴片的封装相对的寄生电感会小。而从散热的角度出发,像TO220这样起直插的,可以更方便地进行散热器的放置。

问:电源的功率芯片的发热和系统输出功率有什么关系?

答:这个问题比较大,要具体到信号和电路才好分析,跟Vcc和反馈都有很大关系

问:电源的功率芯片的发热和系统输出功率有什么关系?

答:发热和输出功率没有必然联系。发热取决于效率和散热情况。不过一般情况下,由于功率大的产品电流也较大,发热量大,功率器件容易发热。

问:防静电性能如何?

答:我们在美国专门有一个team做静电方面的研究,所以静电防护是我们产品的强项。而且我们可以帮助客户检查他们的产品,是否存在静电隐患。

问:飞兆MOSFET采用的是哪种可靠性寿命试验?是加速寿命试验吗?

答:我们会做HTRB测试。

问:飞兆半导体是如何提升系统效率和功率密度?

答:飞兆半导体的分立元件,性能在业内都是领先的,可以保证客户实现很高的效率,在高效率的基础上满足尽量小的空间应用。此外,飞兆还推出目前比较流行的高效率拓扑控制器,比如LLC。

问:飞兆的MOS有没有与其相匹配的飞兆电源IC,组合搭配应用的建议?

答:临界导通模式的PFC控制器,以及反激控制芯片,LLC控制芯片,这些都有。

问:看到有的快速导通的二极管直插管脚上套着磁环,应该是防止EMI的,有这个必要吗?

答:加磁环大多是为了解决EMI问题,这是有效的办法,但是会稍微影响一点效率,也会增加成本。

问:快速开关速度的解调器电源系统提升效率比大约是多少?

答:这个应系统设计不同而不同, 有些可以提高达20%

问:请问电源PCB的布局对电源效率有影响吗

答:没有一个本质的关系。但PCB布局会影响到寄生参数。会对效率有相应的影响。

问:如何实现AC/DC同步整流 能提供相应的电路和所采用的器件吗

答:同步整流只是用MOS当二极管用,所以,具体的实现要根据拓补结构而定,包括相应的控制电路。如果需要技术支持和相关的样品,请联系我们就近的办事处。

问:如何有效降低电源中Power Trench MOSFET中的开关损耗?

答:我们现在PT MOS利用了栅极屏蔽技术,有效地降低了Qg, Ciss, 等寄生参数,而这些正是开关损耗的相关因素。

在线座谈(Online Seminar)是中电网于2000年推出的创新服务,通过“视频演示+专家解说+在线问答”三位一体相结合的形式,充分发挥网络平台的便捷性,实现了先进半导体技术提供商与系统设计工程师的实时互动交流,其形式和内容都广受电子行业工程师的好评。本刊每期将挑选一些精华内容整理成文,以飨读者。欲了解更多、更详细的内容,敬请登录http://seminar.eccn.com。

GEC

随着功率电源技术和信息技术的发展,用户对高效率小体积产品的要求越来越高,对电源的性能也相应提出了更为苛刻的规范要求,电源市场迎来巨大的商机,同时也迎来了巨大的挑战。本次报告包括以下几项内容:系统效率和功率密度的重要性,行业发展的趋势以及相应的解决方案,电源设计中面临的挑战,需要更高系统效率和功率密度的一些典型应用,以及在选用飞兆半导体采用屏蔽技术的中等电压Power Trench MOSFET后可实现更高系统效率和功率密度。

基于系统效率和功率密度发展趋势示意图,我们可以清晰的看出,在最近的十年间系统的效率和功率密度有了巨大的提升,尤其以服务器和通信电源为显著。这一巨大的提升是如何实现的呢?它主要是通过尝试新的拓扑结构,引进新技术高性能的功率器件,同时通过良好的系统设计来保证,以上几点我们会在接下来的内容中给出进一步的讨论。

系统效率和功率密度的重要性

为了说明系统效率和功率密度的重要性,我们以通信网络能耗增长为例做简要介绍。自2009年开始,通信网络每年的能耗百分比都以线性上升,到2016年这一数字将翻番,这彰显了系统的效率和功率密度对于工业应用是多么重要。

随着对电源系统效率和功率密度不断提高的行业发展趋势,各个国家和地区针对自己的具体情况开发并颁布了一系列新的标准以适应本国情况,例如美国的能源之星、欧盟的生态标准以及中国的CSC标准。电源行业针对这些新的要求,通过提高系统效率,增加功率密度及降低能源成本的方式来达到新标准的要求。

针对于服务器应用和通信应用的高性能电源,在设计过程中有以下三个指标尤为重要:一、如何提高系统的功率密度,二、如何提高系统轻载下的效率,三、如何实现长系统寿命下的高可靠性。图片所示是在原系统基础上改用飞兆半导体中等电压Power Trench MOSFET后在轻载25%状态下效率有明显的提高,大约1%左右。

系统效率和功率密度发展趋势示意图

飞兆半导体应用解决方案

针对目前高性能电源设计中的难点,飞兆半导体的解决方案可以帮助客户降低系统的RDS(ON),减少系统的传导损耗,减少系统的开关噪声,以及减少系统的热耗散,从而使得单位面积做到最小。除了通信电源以及服务器电源之外,需要更高效率和功率密度的应用还有很多,例如ATX电源以及专事转换器、VRM模块、D类音频放大器以及马达驱动等。

这里我们首先以AC-DC同步整流应用为例。在通讯电源的应用中它的主功率部分主要由功率校正电路、原边的电源转换电路、副边的整流电路组成,我们可以很清楚的看到,在图中有非常多的功率器件,系统的效率也就由这些功率器件的工作效率以及本身的性能优劣决定。

在服务器中隔离型或非隔离型DC-DC电路的应用,我们可以用方框图来描述。在下方蓝色图中是一典型的服务器电源的组成架构,它由原边、副边以及非隔离型的DC-DC电路组成。如通信电源一样,在其中有非常多的功率器件来实现电流、电压的转换电路,使系统的效率高低以及功率密度可以做的好坏和功率器件的选择有着直接和密不可分的关系。在以上描述的功率转换电路中,选择飞兆半导体采用屏蔽栅极技术的中等电压Power Trench MOSFET之后,可以实现系统的更高效率和更高的功率密度。

屏蔽栅极技术

这里我们对沟槽型功率MOS管的发展做一个简单的回顾。左边是传统沟槽型MOSFET的典型结构,与前期的平面结构的MOS管相比,它具有更低的RDS(ON)以及更好的开关特性。经过一段时间的发展,底部有厚氧化层的沟槽型MOS管替代了传统的沟槽型MOS管,它可以减少外延层的寄生电阻,得到更低的RDS(ON)。在采用屏蔽栅极技术的Power Trench MOSFET技术之后,可以使功率MOS管具有更高的单元密度,同时在采用电荷平衡技术之寄生电阻后,可以更加有效的减少Epi电阻,从而更大程度的减小了寄生电阻的阻值,以及提高了开通与关断的特性。

在使用了飞兆半导体Power Trench结构功率MOS管之后效能是如何提高的呢?我们以一台1000W的通信电源为平台做一些产品的对照比较。在使用了飞兆半导体FDH055N15A之后,效能提升可以从最小0.2%到超过0.5%,也就是可以有最高5W的功率提升,可以从图中看出,蓝色线是使用了飞兆半导体的功率器件,红色线是竞争对手的5.9mΩ的一颗150V的相同规格的MOS管的测试曲线。

与竞争对手的Power Trench 结构功率MOS管相比,飞兆半导体屏蔽栅极技术的MOS管在同步整流的运用下有明显的优势。如图中所示,飞兆半导体的FDP036N10A与竞争对手最好的MOS管相比,在Qg值上仍然比竞争对手低10%以上。我们可以读出它的数据,飞兆半导体的FDP036N10A的Qg值是58.7,而竞争对手最好的MOS管也要达到76.2。

系统轻负载效率比较

AC-DC同步整流应用

同步整流中的驱动损耗

从左边测试曲线可以看出,在导通期间内电流从源极到漏极流过MOSFET沟道,并在死区时间流过体二极管,由于在开关瞬变期没有电压穿过同步开关,所以这里不会发生“密勒效应”,在栅-源电压上没有过渡平台。再看右边的曲线图,红色线为没有了“密勒效应”的驱动波形,可以看到它的时间相对传统MOS管的时间有着明显的缩短。

在针对隔离型和非隔离型DC-DC应用中如何提高效能,我们基于一款1/16砖的平台上做了一系列的比较试验。在采用了飞兆半导体FDMS86252与主要竞争对手产品比较,效率提升范围最小为0.4%,最大为超过1%,也就是有0.32W的功率提升,从图中可以看出,上面的曲线为采用了飞兆半导体FDMS86252的测试曲线。

众所周知低的RDS(ON)可以提高系统效能以及功率密度,这里我们针对芯片级对RDS(ON)的贡献做出分析。在比较每一串联电阻对低电压部分和高电压部分的贡献率时,可以看到,当Vg=10V、单位电流密度为200A/cm2时,外延层的电阻占的比例至关重要。在30V的VDS时,外延层的电阻只占29%,但当VDS上升到100V时,外延层的电阻将占到整个RDS(ON)的78%。所以现今在高压MOSFET上所做的大部分开发工作,都正在转向如何减少漂移区的EPI电阻。

现今如要满足行业的标准,就必须要提高设计的效率以及增加功率密度。飞兆半导体的屏蔽栅极功率MOSFET中,在5X6mm尺寸内最低RDS(ON)最大值可以做到2.5mΩ,典型值为60V的击穿电压。如右图所示,屏蔽栅极功率MOS管的击穿参数除传统的参数Cds、Cgs和Cgd之外,这里增加了CG屏蔽层以及CD屏蔽层,CG屏蔽层以及CD屏蔽层的电容作用会在后边给出解释。

飞兆半导体领先的RDS(ON)性能

基于飞兆半导体屏蔽栅极技术所提供的RDS(ON)性能,从图中可以读出,飞兆半导体屏蔽栅极技术功率MOS管测试点都在竞争对手的下边,也就是说在相同的测试条件下,飞兆半导体屏蔽栅极技术可以提供更低的RDS(ON)性能。

在选用飞兆半导体屏蔽栅极功率MOS管后,功率密度又是怎么增加的呢?我们基于AC-DC同步整流应用做一简单介绍。在选用飞兆半导体屏蔽栅极功率MOS管后,可以有效减少电压尖峰,其结果是可以使设计者选用更低额定电压的MOSFET,同时大多数应用都无需外部缓冲器。在相同测试条件下,使用飞兆半导体屏蔽栅极功率MOS管后电压尖峰可以比对手的小10%以上。

隔离型或非隔离型DC-DC的应用

同步整流中的电压尖刺损耗

在同步整流中,与器件相关的主要参数是MOS管的体二极管的柔和程度,针对于飞兆半导体屏蔽栅极功率MOS管而言,这一特性会比竞争对手更好,也就是我们定义体二级管恢复时间的TB/TA为软恢复特性,当这特性较软时,意味着同步整流中的电压尖刺可以被有效降低,其结果是可以省去缓冲器电路,或者用较低额定电压MOS管替换较高额定电压的MOS管。

屏蔽栅极技术的优势

可以带来优良的体二极管性能,而优良的体二极管性能又可以带来软反向恢复特殊和低电压尖刺,下三图是实测结果。左面是使用了飞兆半导体屏蔽栅极技术的体二极管反向恢复特性,最高毛刺电压仅有56.8V,中间图是和竞争对手最好的MOS管相比,它的方向尖峰电压仍然到63.32V。

对于隔离型或非隔离型DC-DC的应用中,在考虑到线路板空间更小,又需要增加功率密度时,我们推荐Power56的封装形式,而非D2PAK或其他封装模式。在使用了飞兆半导体屏蔽栅极功率MOS管后,可以减少开关节点的振铃现象,同时由于屏蔽栅极功率MOS管固有的电子和电容,可以实现内置的漏极到源极的缓冲电路,从而在大多数应用都无需外部缓冲电路。

与传统的Power Trench 功率MOS管相比,屏蔽栅极技术有着独特的优势。屏蔽栅极技术MOS管可以减少QGD,减少QGD带来的结果是可以拥有非常优良的开关特性及较低的振铃现象,较低的振铃现象又可以使多数情况下无需外接缓冲电路。通过比较我们可以看到,采用飞兆半导体屏蔽栅极功率MOS管后产生的振铃不到竞争对手的一半。

现在对电源系统的高能耗成本做系统分析。以服务器机架电源成本为例,预计2011年服务器数量将达到870万台,每台服务器的额定电源为4X2KW/h,即8KW/h,而每个机架有8台服务器,就是有大约100万个服务器机架,乘以8KW/h后得到额定功率为800万KW/h,以每KW/h价格0.15美元计算,最后得到成本为120万美元。对应如此高的能源成本,我们只能通过提高电源效率、提高功率密度,来节约电源的高能耗成本。

现在看看系统选用飞兆半导体的高成本效益电源之后会有什么变化。我们选用Power56技术封装的屏蔽栅极MOS管FDMS86500L,它可以使整机效率提高约1%,即每个电源每小时节电20W,每个服务器机架每年节电800W,每个服务器机架每年可以节省105美元,考虑到全部服务器机架数量为100万台,这样总体每年可以节省约11.4亿美元。这里我们可以看到,提高效率可以大幅节省成本,而提高功率密度又可以提供占位更小的解决方案,从而进一步节省成本。

总结

对于功率电源领域的发展趋势而言,更高的系统效率以及更高的功率密度已经成为各大公司及其设计人员所要达到的首要目标。根据这一系列的高要求,飞兆半导体推出了一系列的高性能的屏蔽栅极功率MOS管,可以很好的帮助设计人员解决效率以及功率密度的问题。飞兆半导体屏蔽栅极功率MOS管针对通信电源、服务器电源以及DC-DC同步整流电路,可以提高效率和功率密度,对于飞兆半导体屏蔽栅极功率MOS管的特点而言,具有低的Qg、软的体二极管的恢复特性以及极低的RDS(ON),以上特性均可以对系统的效率以及功率密度产生相当的贡献。

问答选编

问:3061之类的应该都是隔离过零驱动吧?

答:moc302x 系列

问:电压最好降额80%来使用,额定100V的管子用在20V的电路里比较安全,还是用在80V的电路里比较安全?

答:100V的管子,在系统稳态暂态各种工作条件下,电压不要超过80V,比较理想。

问:MOS当二极管用,中间的管脚必须要剪断吗?为什么不直接用二极管呢?

答:不用。二极管的压降在1V左右,如果输出电压很低,比如5V,这时候对效率影响很大,这时就需要同步整流。

问:MOS管在高速开关时产生的辐射主要是传导的还是辐射的?应该如何去除此种EMI

答:传导会是主要的,尽量减小回路,同时加吸收回路。

问:MOS管在什么情况下最容易损坏,之前有个电源的MOS击穿了,最后厂家解释说是电容里的静电或人体静电,通过MOS管卸放,击穿MOS管,这可能吗?

答:通过MOS管卸放也有可能击穿MOS的,所以操作人员要带防静电设备

问:Power Trench MOSFET的热特性和保护性能如何 使用时是否需要加散热器

答:Trench技术可以提高效率,以此减小发热,因此热特性会好一些。是否加散热器要根据具体应用来决定。MOS本身没有保护线路,因此需要工程师在设计时考虑裕量

问:Power Trench MOSFET的主要封装形式有哪几种?

答:这个从贴片到直插的一些常用封装都是有的。TO220, TO263, Power56等

问:Power Trench MOSFET的主要优势是什么

答:1.减小导通电阻Rdson;2.提高开关性能;3 Bodydiode的软恢复性能

问:采用PFC电路,是否有助于提高电源效率 为什么

答:采用PFC不会提高系统效率,反而会降低效率,因为PFC会增加元器件,反而会增加损耗。但是有了PFC,你的功率因数会提高,这样即使效率低一些,反而会省电。用电量=实际使用的电量/功率系数。

问:采用Power Trench MOSFET,效率能提高多少

答:采用Trench技术,中低压MOS的导通阻抗通常会小20~30%,考虑到开通损耗,综合效率可以提高20%左右。

问:产品的产地在哪里,供货周期一般是多久?

答:我们的封装工厂分布在苏州,马来西亚和菲律宾。TO-220的产品大多在苏州生产。供货周期通常在8-12周。

问:从频率特性和热特性以及封装成本来看, 采用那种封装的Power Trench MOSFET较优

答:从频率特性来看,一般贴片的封装相对的寄生电感会小。而从散热的角度出发,像TO220这样起直插的,可以更方便地进行散热器的放置。

问:电源的功率芯片的发热和系统输出功率有什么关系?

答:这个问题比较大,要具体到信号和电路才好分析,跟Vcc和反馈都有很大关系

问:电源的功率芯片的发热和系统输出功率有什么关系?

答:发热和输出功率没有必然联系。发热取决于效率和散热情况。不过一般情况下,由于功率大的产品电流也较大,发热量大,功率器件容易发热。

问:防静电性能如何?

答:我们在美国专门有一个team做静电方面的研究,所以静电防护是我们产品的强项。而且我们可以帮助客户检查他们的产品,是否存在静电隐患。

问:飞兆MOSFET采用的是哪种可靠性寿命试验?是加速寿命试验吗?

答:我们会做HTRB测试。

问:飞兆半导体是如何提升系统效率和功率密度?

答:飞兆半导体的分立元件,性能在业内都是领先的,可以保证客户实现很高的效率,在高效率的基础上满足尽量小的空间应用。此外,飞兆还推出目前比较流行的高效率拓扑控制器,比如LLC。

问:飞兆的MOS有没有与其相匹配的飞兆电源IC,组合搭配应用的建议?

答:临界导通模式的PFC控制器,以及反激控制芯片,LLC控制芯片,这些都有。

问:看到有的快速导通的二极管直插管脚上套着磁环,应该是防止EMI的,有这个必要吗?

答:加磁环大多是为了解决EMI问题,这是有效的办法,但是会稍微影响一点效率,也会增加成本。

问:快速开关速度的解调器电源系统提升效率比大约是多少?

答:这个应系统设计不同而不同, 有些可以提高达20%

问:请问电源PCB的布局对电源效率有影响吗

答:没有一个本质的关系。但PCB布局会影响到寄生参数。会对效率有相应的影响。

问:如何实现AC/DC同步整流 能提供相应的电路和所采用的器件吗

答:同步整流只是用MOS当二极管用,所以,具体的实现要根据拓补结构而定,包括相应的控制电路。如果需要技术支持和相关的样品,请联系我们就近的办事处。

问:如何有效降低电源中Power Trench MOSFET中的开关损耗?

答:我们现在PT MOS利用了栅极屏蔽技术,有效地降低了Qg, Ciss, 等寄生参数,而这些正是开关损耗的相关因素。

在线座谈(Online Seminar)是中电网于2000年推出的创新服务,通过“视频演示+专家解说+在线问答”三位一体相结合的形式,充分发挥网络平台的便捷性,实现了先进半导体技术提供商与系统设计工程师的实时互动交流,其形式和内容都广受电子行业工程师的好评。本刊每期将挑选一些精华内容整理成文,以飨读者。欲了解更多、更详细的内容,敬请登录http://seminar.eccn.com。

GEC

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:调压、定时两用控制器

下一篇:UPS稳压电源工作方式简介

射频和天线工程师培训课程详情>>