- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用于低功耗SoC设计的自适应电压调节技术

录入:edatop.com 点击:

消费者对便携设备新功能的要求永无止境,并且希望仍能保持电池充电后的工作时间。于是,系统设计与 SoC 设计小组面临在增加功能的同时保证电池的使用时间的挑战。要达到这一点,就需要使用新的节能技术,如电压调节(voltage scaling)。SoC 设计中降低功耗可以用两种方式来实现,一种是开环电压调节(动态),另一种则是闭环(自适应)电压控制方法。

频率调节与电压调节

计算系统在实际期限中执行任务。当系统为高负载时,系统要在最大频率下工作。而当系统负载低时,则允许系统在较低频率下工作。这种频率调节是一种降低运行功耗的有效方式。电压调节与频率调节相互结合,能够极大地降低功耗,提高能量效率。动态电压调节(DVS)是在一个开环电压控制系统中用多组频率、电压对来实现。自适应电压调节(AVS)用一个闭环电压控制系统来实现,它无需配对的频率、电压,能提供更优的节能效果。

CMOS 数字系统中的功耗

CMOS 数字系统的功率是开关功率(动态)与泄漏功率的总和。

P = Pswitch + Pleakage ≈ C x V2AF + Ileakage

其中 C 表示数字系统中的开关电容,V 为供电电压,F 则为开关时钟频率,A 是开关活动因数,而 Ileakage 则为漏电流。

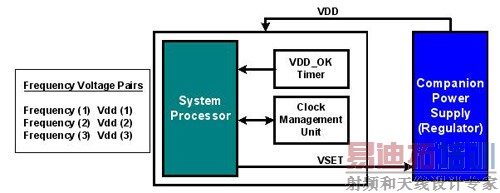

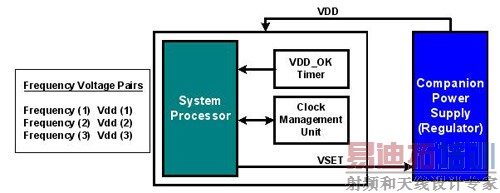

开环动态电压调节(DVS)

图 1 显示的是一个 DVS 系统。当允许工作在低于最高频率时,频率随电压的下降而降低。在 DVS 系统中,每种工作频率的供电电压值都是所有芯片工艺和温度变化所需的最差值。当系统在降低的频率工作时,功耗也显著下降,因为功率方程中的 F 和 V2 两项均减小。当系统工作在最高频率时,DVS 方法对恒定电压没有节能效果。

图 1 – 开环 DVS 框图

Frequency Voltage Pairs:频率-电压对

Frequency (1) Vdd(1):频率(1)Vdd(1)

Frequency (2) Vdd(2):频率(2)Vdd(2)

Frequency (3) Vdd(3):频率(3)Vdd(3)

System Processor:系统处理器

VDD_OK Timer:VDD_OK 定时器

Clock Management Unit:时钟管理单元

Companion Power Supply(Regulator):配合的电源(稳压器)

闭环自适应电压调节(AVS)

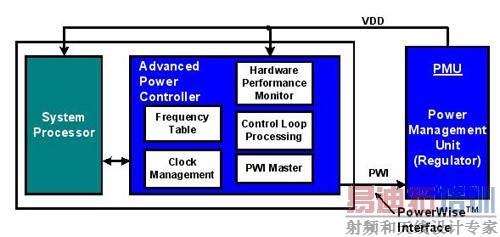

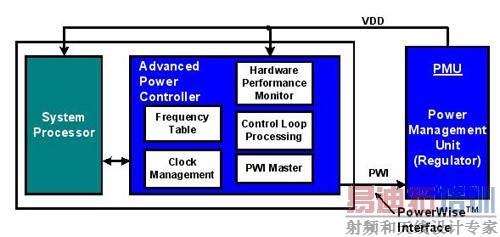

图 2 是采用 PowerWise 先进电源控制器(APC)以及集成硬件性能监控器(HPM)与电源管理单元(PMU)的一个闭环 AVS 系统。APC 通过开放标准 PowerWise 接口(PWI)连接到 PMU 上。这些组成部分自适应地为多种时钟频率、温度和芯片工艺提供最低供电电压。

闭环 AVS 系统使用嵌入在电压调节域中的 HPM 来监控芯片芯的时序性能,并提供可变电压系统控制环路的闭环机制。由于 HPM 与其监控的计算系统位于相同的芯片上,因而可以提供芯片工艺补偿以及温度补偿。

图 2 – 闭环 AVS 方块图

System Processor:系统处理器

Advanced Power Controller:先进电源控制器

Frequency Table:频率表

Clock Management:时钟管理

Hardware Performance Monitor:硬件性能监控器

Control Loop Processing:控制环路处理

PWI Master:PWI 控制

Power Management Unit(Regulator):电源管理单元(稳压器)

PowerWiseTM Interface:PowerWiseTM 接口

APC 处理来自 HPM 的信息,决定是否需要调节电压。电压调节指令通过 PWI 送给 PMU。

采用低速时序的芯片工艺,ASIC 设计可以在最高温度下工作。典型的工作温度和典型的芯片性能会有电压余量(headroom)。AVS 系统会检测这一余量,并调整电压,使得在所有运行频率上都有最低的运行功率。

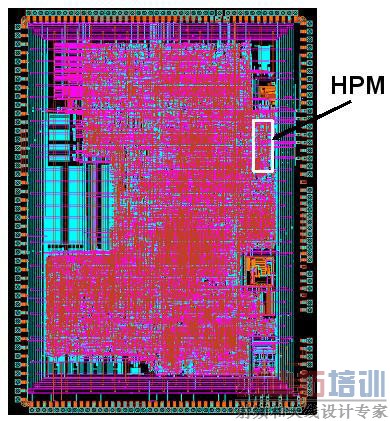

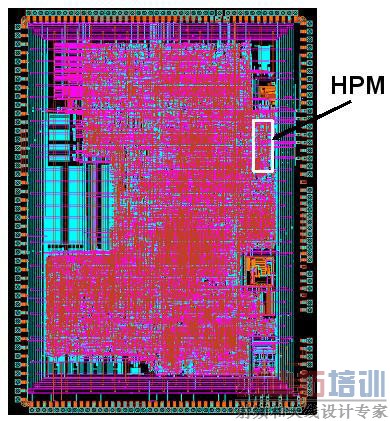

降低 SoC 的功耗

图 3 中的测试芯片是在标准的 0.18 微米 CMOS 工艺上实施的。处理器(ARM7 TDMI-S)与外围逻辑电路均由自适应的电压供电,电压变动范围是 1.8V 至 1.2V。模拟电路和时钟发生逻辑电路的电压是固定的,为 1.8V。

图 3 – 0.18 微米测试芯片的裸片布局

HPM 与一个分立的电压调节系统通信,该系统模拟一个完全集成的 APC、PWI 和 PMU 闭环系统。

图 4 显示测试芯片电压调节域的功率比较图。对于这块典型的性能测试芯片,在固定 1.8V 供电电压时,带 AVS 测出的节能百分比为:80MHz 时 45%,48MHz 时 63%,6MHz 时 81%。

图 4 – 功率测量:固定电压和使用 AVS 时的 0.18 微米测试芯片

Power Consumption Comparison:功耗比较图

Measured, 180nm, Typical Silicon, Room Temp:测量条件:0.18 微米典型芯片,室温

Power(Normalized):功率(标准化)

Frequency(MHz):频率(MHz)

Fixed Voltage:固定电压

PowerWise AVS 的优点

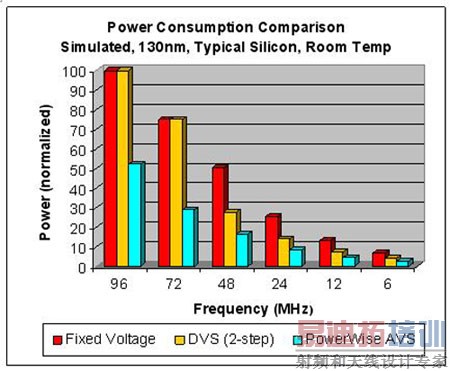

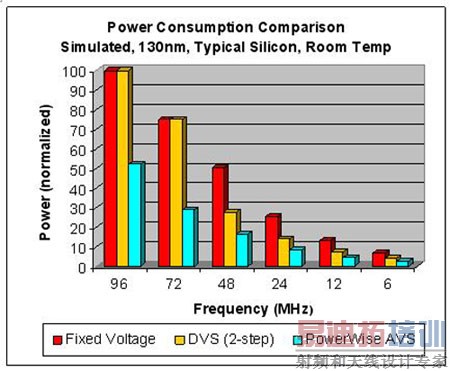

图 5 同时显示了各种功耗的模拟图,包括固定电压、开环 DVS 和闭环 AVS 供电系统。

模拟图使用了一个 ±10% 的调节方法,为96MHz 、低速仿真模型以及 120 度连结温度等设计工作条件提供固定而且是 DVS 的电压。这些条件代表了一个 ASIC 设计中常见的时序分析条件。

图 5 – 模拟的功率图:采用 AVS、2 级 DVS 和固定供电电压的 0.13 微米设计

Power Consumption Conparison:功耗比较图

Simulated, 130nm, Typical Silicon, Room Temp:模拟条件:0.13 微米典型芯片,室温

Power(Normalized):功耗(标准化)

Frequency(MHz):频率(MHz)

Fixed Voltage:固定电压

DVS(2-step):DVS(2-级)

DVS 的数据表示了一种两级式供电系统。在 70 MHz 以上频率时,采用 1.2V 供电,而在低于 70MHz 频率时,则提供 0.9V 电压。AVS 的供电电压等于模拟设计中发生一个时序错误时的电压与考虑 HPM 准确性的适当电压裕度之和。

当系统在可调节频率下工作时,DVS 和 AVS 共同达成降低固定电压系统功耗的目标。AVS 在所有工作频率时都能提供降低功耗的额外好处。达到设计目标频率的节能是采用低速芯片时最大频率与最大连结温度条件下闭环时序的设计需要。

结论

功耗和能效都是系统设计的重要考虑因素。在系统设计中使用 DVS 或 AVS 可以使固定电压系统获得显著的节能效果。当频率可调节系统的工作频率低于最大设计频率时,DVS 可提供节电节能功能。AVS 则在固定频率系统和可变/可调节频率系统中发挥节电节能作用。PowerWise 自适应电压调节技术可以在 SoC 的所有设计工作频率下达到显著的降低功耗目的,包括最大设计目标频率。

频率调节与电压调节

计算系统在实际期限中执行任务。当系统为高负载时,系统要在最大频率下工作。而当系统负载低时,则允许系统在较低频率下工作。这种频率调节是一种降低运行功耗的有效方式。电压调节与频率调节相互结合,能够极大地降低功耗,提高能量效率。动态电压调节(DVS)是在一个开环电压控制系统中用多组频率、电压对来实现。自适应电压调节(AVS)用一个闭环电压控制系统来实现,它无需配对的频率、电压,能提供更优的节能效果。

CMOS 数字系统中的功耗

CMOS 数字系统的功率是开关功率(动态)与泄漏功率的总和。

P = Pswitch + Pleakage ≈ C x V2AF + Ileakage

其中 C 表示数字系统中的开关电容,V 为供电电压,F 则为开关时钟频率,A 是开关活动因数,而 Ileakage 则为漏电流。

开环动态电压调节(DVS)

图 1 显示的是一个 DVS 系统。当允许工作在低于最高频率时,频率随电压的下降而降低。在 DVS 系统中,每种工作频率的供电电压值都是所有芯片工艺和温度变化所需的最差值。当系统在降低的频率工作时,功耗也显著下降,因为功率方程中的 F 和 V2 两项均减小。当系统工作在最高频率时,DVS 方法对恒定电压没有节能效果。

图 1 – 开环 DVS 框图

Frequency Voltage Pairs:频率-电压对

Frequency (1) Vdd(1):频率(1)Vdd(1)

Frequency (2) Vdd(2):频率(2)Vdd(2)

Frequency (3) Vdd(3):频率(3)Vdd(3)

System Processor:系统处理器

VDD_OK Timer:VDD_OK 定时器

Clock Management Unit:时钟管理单元

Companion Power Supply(Regulator):配合的电源(稳压器)

闭环自适应电压调节(AVS)

图 2 是采用 PowerWise 先进电源控制器(APC)以及集成硬件性能监控器(HPM)与电源管理单元(PMU)的一个闭环 AVS 系统。APC 通过开放标准 PowerWise 接口(PWI)连接到 PMU 上。这些组成部分自适应地为多种时钟频率、温度和芯片工艺提供最低供电电压。

闭环 AVS 系统使用嵌入在电压调节域中的 HPM 来监控芯片芯的时序性能,并提供可变电压系统控制环路的闭环机制。由于 HPM 与其监控的计算系统位于相同的芯片上,因而可以提供芯片工艺补偿以及温度补偿。

图 2 – 闭环 AVS 方块图

System Processor:系统处理器

Advanced Power Controller:先进电源控制器

Frequency Table:频率表

Clock Management:时钟管理

Hardware Performance Monitor:硬件性能监控器

Control Loop Processing:控制环路处理

PWI Master:PWI 控制

Power Management Unit(Regulator):电源管理单元(稳压器)

PowerWiseTM Interface:PowerWiseTM 接口

APC 处理来自 HPM 的信息,决定是否需要调节电压。电压调节指令通过 PWI 送给 PMU。

采用低速时序的芯片工艺,ASIC 设计可以在最高温度下工作。典型的工作温度和典型的芯片性能会有电压余量(headroom)。AVS 系统会检测这一余量,并调整电压,使得在所有运行频率上都有最低的运行功率。

降低 SoC 的功耗

图 3 中的测试芯片是在标准的 0.18 微米 CMOS 工艺上实施的。处理器(ARM7 TDMI-S)与外围逻辑电路均由自适应的电压供电,电压变动范围是 1.8V 至 1.2V。模拟电路和时钟发生逻辑电路的电压是固定的,为 1.8V。

图 3 – 0.18 微米测试芯片的裸片布局

HPM 与一个分立的电压调节系统通信,该系统模拟一个完全集成的 APC、PWI 和 PMU 闭环系统。

图 4 显示测试芯片电压调节域的功率比较图。对于这块典型的性能测试芯片,在固定 1.8V 供电电压时,带 AVS 测出的节能百分比为:80MHz 时 45%,48MHz 时 63%,6MHz 时 81%。

图 4 – 功率测量:固定电压和使用 AVS 时的 0.18 微米测试芯片

Power Consumption Comparison:功耗比较图

Measured, 180nm, Typical Silicon, Room Temp:测量条件:0.18 微米典型芯片,室温

Power(Normalized):功率(标准化)

Frequency(MHz):频率(MHz)

Fixed Voltage:固定电压

PowerWise AVS 的优点

图 5 同时显示了各种功耗的模拟图,包括固定电压、开环 DVS 和闭环 AVS 供电系统。

模拟图使用了一个 ±10% 的调节方法,为96MHz 、低速仿真模型以及 120 度连结温度等设计工作条件提供固定而且是 DVS 的电压。这些条件代表了一个 ASIC 设计中常见的时序分析条件。

图 5 – 模拟的功率图:采用 AVS、2 级 DVS 和固定供电电压的 0.13 微米设计

Power Consumption Conparison:功耗比较图

Simulated, 130nm, Typical Silicon, Room Temp:模拟条件:0.13 微米典型芯片,室温

Power(Normalized):功耗(标准化)

Frequency(MHz):频率(MHz)

Fixed Voltage:固定电压

DVS(2-step):DVS(2-级)

DVS 的数据表示了一种两级式供电系统。在 70 MHz 以上频率时,采用 1.2V 供电,而在低于 70MHz 频率时,则提供 0.9V 电压。AVS 的供电电压等于模拟设计中发生一个时序错误时的电压与考虑 HPM 准确性的适当电压裕度之和。

当系统在可调节频率下工作时,DVS 和 AVS 共同达成降低固定电压系统功耗的目标。AVS 在所有工作频率时都能提供降低功耗的额外好处。达到设计目标频率的节能是采用低速芯片时最大频率与最大连结温度条件下闭环时序的设计需要。

结论

功耗和能效都是系统设计的重要考虑因素。在系统设计中使用 DVS 或 AVS 可以使固定电压系统获得显著的节能效果。当频率可调节系统的工作频率低于最大设计频率时,DVS 可提供节电节能功能。AVS 则在固定频率系统和可变/可调节频率系统中发挥节电节能作用。PowerWise 自适应电压调节技术可以在 SoC 的所有设计工作频率下达到显著的降低功耗目的,包括最大设计目标频率。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于51单片机的数控电源设计

下一篇:基于研究电压型逆变器高压串联谐振技术

射频和天线工程师培训课程详情>>