- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于路径成组分离策略的低功耗FIR 设计

录入:edatop.com 点击:

1 引言

随着移动及便携式电子设备的普及和芯片频率的不断提高,功耗成为电路设计中必须考虑的重要因素。近来,集成电路设计工具已经逐步支持多电压设计,因而,使得对适合多电压实现的数字信号处理部件的算法改进、体系结构、以及逻辑电路等的研究成为进一步降低功耗的关键问题。

通常电路都工作于相同的电压,多电压技术是划分出不同的电压区,进而采用不同供电电压以降低功耗。以往的研究大多是按照系统中各个部件不同的频率或性能来划分不同电压区。而高性能数字信号处理设计中很多情况都是数据通路上的大量计算,工作频率基本都是一致的,因此本文针对这种情况寻求适合多电压设计的电压分区方案。在单一频率的电路层划分出不同的供电电压区,意味着把对应于不同时间约束的路径,确定为不同的电压需求,按照布局情况进行电压区的划分。由此可知,当长短路径规则的归属在不同的模块时,则易于用多电压技术实现,但大多数情况是长短路径交织在一起,很难按长短路径分组划分不同电压区。

本文提出的方法使得电路层错综在一起的路径按照其不同的时间延迟规则的分离开,关键路径和各种不同延迟的非关键路径对应为不同的模块,针对不同的路径长度采取不同的供电电压。通过剩余数方法将一个乘法运算化简为几个非常简单的乘法或加法,并将滤波器按照不同的路径延迟划分几个相互独立的模块,使之适合采用不同的供电电压,从而降低功耗。

2 路径成组分离分析

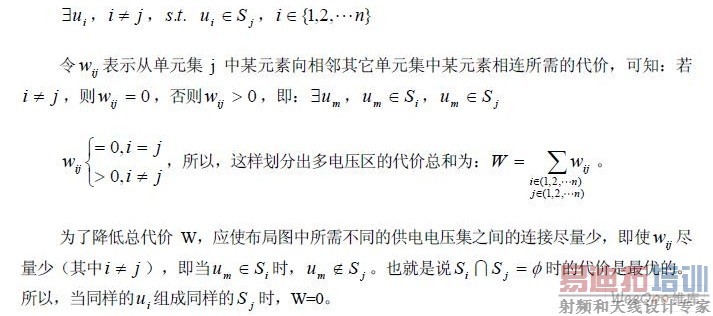

假设在综合后的电路网表中,有n 种不同长度等级的路径,分别采用n 种不同的供电电压。那么在需要多电压供电的电路的布局布线图中,将需要用不同电压供电的单元集(即不同长度的路径)记作ui ,i=1,2,Ln,i表示共需n种不同的电压。

在标准单元设计的电路级,电压供电区是规则的方框区,因此用方框将需要某种电压的单元区框起,每一个方框内的所有单元组成一个单元的集合,记作Sj ,j=1,2,Ln。对于用Vi 供电的单元ui ,可以用比Vi 高的电压Vj >Vi 供电,不影响性能,但不能用小于Vi 的电压供电。

由于EDA 工具自动布局的作用,不同的路径被随机的分布在版图上,不同路径上的单元也是无规律的分布,也就是说所需不同电压的单元是不规则分布的,因此按照上述划分集合的方法对布局图中的单元进行划分后,每个集合中将存在不同供电电压的元素,即:

通过以上分析,如果能够把整个电路按照不同的路径长度成组分离为不同的区域,则采用多电压实现的代价最小。下一节将以剩余数系统为例详细介绍路径成组分离的多电压实现。并在后面给出面积与功耗的优化结果分析。

3 剩余数方法

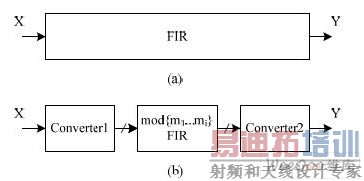

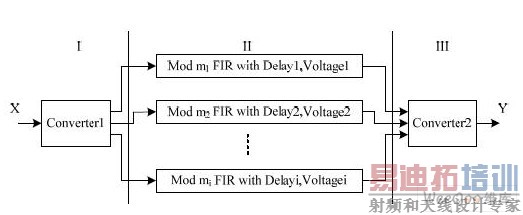

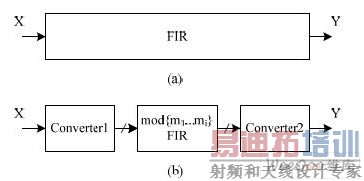

与常用的滤波器的结构略有不同,用剩余数方法实现FIR filter 的结构如图1,该方法需要先将正常的输入转换为一组(设组内元素个数为i)余数表示,然后是i 个独立的FIR,最后将这一组独立的FIR 的计算结果再转换为正常的输出。

图1 (a) 传统FIR 结构(b) 剩余数方法FIR 结构

用剩余数表示来实现FIR filter ,其功能上是等效的,但是其增加了正常模式和剩余表示之间的转换,同时由于采用余数的模乘和模加,大量节约了滤波器的乘累加资源。因此,在整体实现上,是否能节约面积和功耗将主要决定于转换部件的开销。

3.1 选择合适的一组模

对于硬件电路实现,从运算简单的角度出发来选择一组模,当然最好是2n ,其次是形如2n ±1,所以模组可以取为:彼此互素的一组数mi = {2 p1 ±1,2 p2 ±1,L2q }。

3.2 正常模式到剩余表示的转换

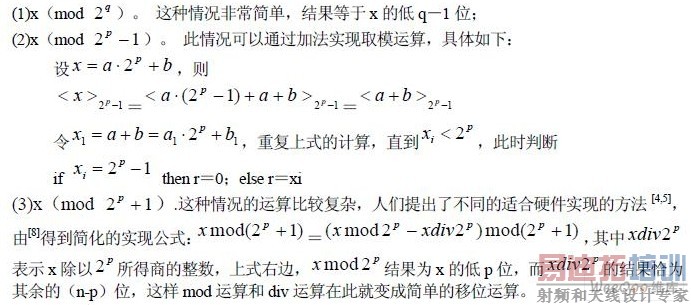

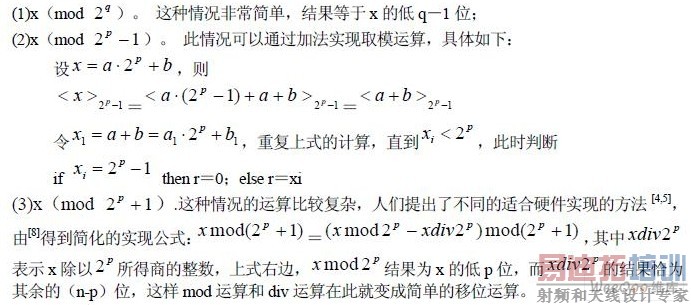

正常表示到剩余表示的转换实际就是取模运算,对于上面选定的一组模,取模运算有以下三种:

3.3 剩余表示到正常表示的转换

如果按照中国剩余定理,这一步的计算将非常复杂。由[6]可将原来中国剩余定理算法中复杂的乘法、mod 运算都化简,剩下的只有查表、加法和移位操作。对于二进制补码表示的有符号数,可采用[6]提出的将负数转换到正数去做的方法。

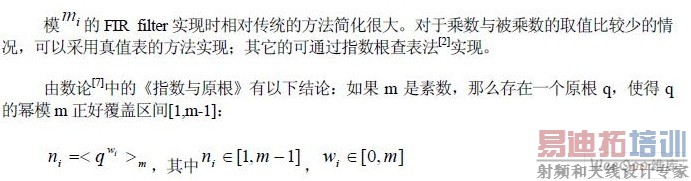

3.4 模乘的实现

n 和w 之间的转换可以通过查表实现,对n=0 的情况在外面判断,即n=0 时结果为0。

3.5 多电压分区

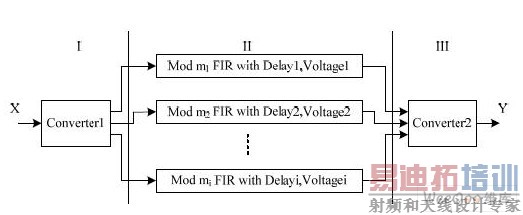

从体系结构可以看到,RNS 方法将滤波器的结构划分为3 部分,如图2 中ⅠⅡⅢ

图2 多电压分区图

其中中间部分有i 条相互独立的路径(i 的值为所选定的一组模的数量),每条路径由于其模乘运算的复杂度不同而导致电路级的路径时延也大不相同。显然,模乘运算最复杂的一条路径将成为中间部分关键路径,因此可以把时延明显较小的路径i 的FIR filter 模块采用低电压实现。

4 功耗与面积分析

以12bits 输入,8bits 系数为例。根据前面选模的方法选取modulo sets = {3, 5, 7, 17, 31, 32}; Converter2采用流水线复用技术实现,共需要7个表、1个加和一些DFF的资源。下面先看一下在TSMC0.25工艺时单一电压情况下不同的模mi 路径的时延信息,如下表:

由于模3、5、31、32 路径上的单个tap 的时延都小于3.6ns ,相当于富余了40%的时序约束(6-3.6=2.4ns ),我们就可以通过在这些非常富余的路径上降低供电电压来降低功耗。在双电压设计下,将供电电压从2.5V 降到2.0V,功耗大约是4.5+0.25*N 。在同样的工艺下实现传统FIR, 得到功耗面积与抽头数的关系为:设抽头数为N

当抽头数为16 时,采用此双电压方法可节省20%-30%的功耗。

5 结论

长短路径成组分离方法是指把路径长度分成不同的级别,每一个级别结合时序约束确定不同的电压,这样就把原来都按最长路径规定的单一电压电路转换为多电压电路。分析了以往多电压研究中电压分区的原则,而高性能数字信号处理设计中由于数据通路上大量的计算,使得以往的原则并不适用;通过对电路布局的多电压代价进行分析,得出把电路按照不同的路径长度成组分离为不同的区域时,易于采用多电压实现。以剩余数方法为例仿真分析结果显示功耗有明显优化。

本文作者创新点:提出把电路按照不同的路径长度成组分离为不同的集合时,易于采用多电压实现,且采用多电压实现的代价最小。

随着移动及便携式电子设备的普及和芯片频率的不断提高,功耗成为电路设计中必须考虑的重要因素。近来,集成电路设计工具已经逐步支持多电压设计,因而,使得对适合多电压实现的数字信号处理部件的算法改进、体系结构、以及逻辑电路等的研究成为进一步降低功耗的关键问题。

通常电路都工作于相同的电压,多电压技术是划分出不同的电压区,进而采用不同供电电压以降低功耗。以往的研究大多是按照系统中各个部件不同的频率或性能来划分不同电压区。而高性能数字信号处理设计中很多情况都是数据通路上的大量计算,工作频率基本都是一致的,因此本文针对这种情况寻求适合多电压设计的电压分区方案。在单一频率的电路层划分出不同的供电电压区,意味着把对应于不同时间约束的路径,确定为不同的电压需求,按照布局情况进行电压区的划分。由此可知,当长短路径规则的归属在不同的模块时,则易于用多电压技术实现,但大多数情况是长短路径交织在一起,很难按长短路径分组划分不同电压区。

本文提出的方法使得电路层错综在一起的路径按照其不同的时间延迟规则的分离开,关键路径和各种不同延迟的非关键路径对应为不同的模块,针对不同的路径长度采取不同的供电电压。通过剩余数方法将一个乘法运算化简为几个非常简单的乘法或加法,并将滤波器按照不同的路径延迟划分几个相互独立的模块,使之适合采用不同的供电电压,从而降低功耗。

2 路径成组分离分析

假设在综合后的电路网表中,有n 种不同长度等级的路径,分别采用n 种不同的供电电压。那么在需要多电压供电的电路的布局布线图中,将需要用不同电压供电的单元集(即不同长度的路径)记作ui ,i=1,2,Ln,i表示共需n种不同的电压。

在标准单元设计的电路级,电压供电区是规则的方框区,因此用方框将需要某种电压的单元区框起,每一个方框内的所有单元组成一个单元的集合,记作Sj ,j=1,2,Ln。对于用Vi 供电的单元ui ,可以用比Vi 高的电压Vj >Vi 供电,不影响性能,但不能用小于Vi 的电压供电。

由于EDA 工具自动布局的作用,不同的路径被随机的分布在版图上,不同路径上的单元也是无规律的分布,也就是说所需不同电压的单元是不规则分布的,因此按照上述划分集合的方法对布局图中的单元进行划分后,每个集合中将存在不同供电电压的元素,即:

通过以上分析,如果能够把整个电路按照不同的路径长度成组分离为不同的区域,则采用多电压实现的代价最小。下一节将以剩余数系统为例详细介绍路径成组分离的多电压实现。并在后面给出面积与功耗的优化结果分析。

3 剩余数方法

与常用的滤波器的结构略有不同,用剩余数方法实现FIR filter 的结构如图1,该方法需要先将正常的输入转换为一组(设组内元素个数为i)余数表示,然后是i 个独立的FIR,最后将这一组独立的FIR 的计算结果再转换为正常的输出。

图1 (a) 传统FIR 结构(b) 剩余数方法FIR 结构

用剩余数表示来实现FIR filter ,其功能上是等效的,但是其增加了正常模式和剩余表示之间的转换,同时由于采用余数的模乘和模加,大量节约了滤波器的乘累加资源。因此,在整体实现上,是否能节约面积和功耗将主要决定于转换部件的开销。

3.1 选择合适的一组模

对于硬件电路实现,从运算简单的角度出发来选择一组模,当然最好是2n ,其次是形如2n ±1,所以模组可以取为:彼此互素的一组数mi = {2 p1 ±1,2 p2 ±1,L2q }。

3.2 正常模式到剩余表示的转换

正常表示到剩余表示的转换实际就是取模运算,对于上面选定的一组模,取模运算有以下三种:

3.3 剩余表示到正常表示的转换

如果按照中国剩余定理,这一步的计算将非常复杂。由[6]可将原来中国剩余定理算法中复杂的乘法、mod 运算都化简,剩下的只有查表、加法和移位操作。对于二进制补码表示的有符号数,可采用[6]提出的将负数转换到正数去做的方法。

3.4 模乘的实现

n 和w 之间的转换可以通过查表实现,对n=0 的情况在外面判断,即n=0 时结果为0。

3.5 多电压分区

从体系结构可以看到,RNS 方法将滤波器的结构划分为3 部分,如图2 中ⅠⅡⅢ

图2 多电压分区图

其中中间部分有i 条相互独立的路径(i 的值为所选定的一组模的数量),每条路径由于其模乘运算的复杂度不同而导致电路级的路径时延也大不相同。显然,模乘运算最复杂的一条路径将成为中间部分关键路径,因此可以把时延明显较小的路径i 的FIR filter 模块采用低电压实现。

4 功耗与面积分析

以12bits 输入,8bits 系数为例。根据前面选模的方法选取modulo sets = {3, 5, 7, 17, 31, 32}; Converter2采用流水线复用技术实现,共需要7个表、1个加和一些DFF的资源。下面先看一下在TSMC0.25工艺时单一电压情况下不同的模mi 路径的时延信息,如下表:

由于模3、5、31、32 路径上的单个tap 的时延都小于3.6ns ,相当于富余了40%的时序约束(6-3.6=2.4ns ),我们就可以通过在这些非常富余的路径上降低供电电压来降低功耗。在双电压设计下,将供电电压从2.5V 降到2.0V,功耗大约是4.5+0.25*N 。在同样的工艺下实现传统FIR, 得到功耗面积与抽头数的关系为:设抽头数为N

当抽头数为16 时,采用此双电压方法可节省20%-30%的功耗。

5 结论

长短路径成组分离方法是指把路径长度分成不同的级别,每一个级别结合时序约束确定不同的电压,这样就把原来都按最长路径规定的单一电压电路转换为多电压电路。分析了以往多电压研究中电压分区的原则,而高性能数字信号处理设计中由于数据通路上大量的计算,使得以往的原则并不适用;通过对电路布局的多电压代价进行分析,得出把电路按照不同的路径长度成组分离为不同的区域时,易于采用多电压实现。以剩余数方法为例仿真分析结果显示功耗有明显优化。

本文作者创新点:提出把电路按照不同的路径长度成组分离为不同的集合时,易于采用多电压实现,且采用多电压实现的代价最小。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:打印头电源参考设计

下一篇:弧焊电源保护电路的设计

射频和天线工程师培训课程详情>>