- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种基于PWM的CMOS数据接口电路设计

录入:edatop.com 点击:

1 引言

随着电路系统需求的扩展,集成电路设计与制造技术的进步,现代数字系统多工作在几百Mbps的速率上,这些高速系统常包含多个电路模块。系统中不同模块间的接口十分重要,它一般采用总线结构。为了获得更高的数据传输速率必须增加内部总线宽度,实际应用中,采用更大芯片面积和更多端口数目。这类问题也出现在板级系统中。为此,提出一个端口同时传输多个比特的概念以解决该问题,即采用调制技术,在电路中将数据与时钟信号合并为一个通道以减少端口数。为解调该信号,接收端则采用时钟恢复电路(CRC)从数据流中提取时钟信号。常用的调制技术包括PPM,PCM及PWM。

给出了一采用PWM,传输速率达400Mbps的数据接口电路。用脉冲宽度对数据进行编码,并保证含时钟周期上升沿,将时钟信号嵌入到编码后的数据中,这样在接收端很容易以传统的PLL恢复出时钟。可用PLLVC输出来解PWM编码信号,这样电路几乎就只需一个PLL。由于接收信号每个周期都有上升沿,避免了数据格式不同引起的电平与时间偏移。

2 基本原理与系统结构

PWM的脉宽值T与数据速率D可以分别表示为:

上式中N表示每符号的比特数,R表示符号率, 为单位脉宽。为简化电路设计,我们取N=2。PWM发送单元包括一串/并转换,PWM调制器,发送PLL,二分频器及接口电路。接收单元包括接口电路,PWM解调器,接收PLL,并/串转换。

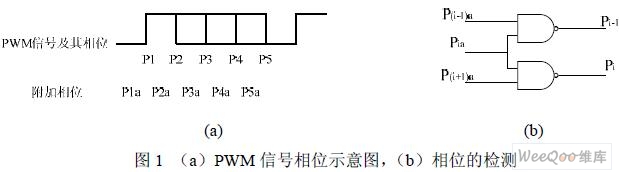

每2bit的数据通过串/并转换合并对应为一个符号。00, 01, 10, 11四个不同符号分别对应不同的脉宽。每个符号对应2bit信息,因而采用二分频电路。CLK经二分频后作为PLL的参考时钟。PLL中的VCO能产生五种时钟相位供PWM调制器使用。PWM由VCO的第一个相位输出触发实现同步,由另外四个中的一个来复位,实现了上升沿触发同步,脉冲宽度编码的PWM发送电路。

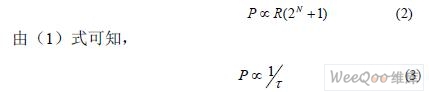

接收电路与发送电路工作过程相反,接收到的PWM信号首先经过接口电路转化为全摆幅CMOS电平。然后一路送PLL,一路接收PWM,接收PLL与发送PLL相似,只是在各相输出后产生五个附加相,这五个附加相准确定位,用以检测PWM编码信号的下降沿,由图1可知只要确定了下降沿,符号就能被解码成2bit的信号,经并/串转换输出。

电路的功耗主要来源于PWM编、解码器及接收、发送PLL。若N增加,上升、下降过程的密度减少,发送与接收单元功耗也随之减少。发送与接收PLL的功耗由下式决定:

显然,这个功耗值与N并无直接关系。

3 电路设计

3.1 发送/接收PLL

PLL的性能在本接口电路中相当关键,若将PLL与低噪声的数字电路集成在同一块硅片上,抖动问题尤为重要。该电路采用的PLL是一个包含PFD,低通滤波器/泵浦,VCO在内的传统电流泵浦型PLL(CPPLL)。采用外接低通滤波器以减少片上面积,如前所述,发送、接收PLL只在VCO上有所不同。

为获得低抖动PLL,PFD的性能很重要,PFD的品质可由死区值(即不可检测的最小相位差)来衡量,传统的静态PFD用NAND来复位内部节点,延时大,死区值较大,导致了大的时钟抖动,从而限制了电路的最高工作频率。本文采用dec-PFD (double edge checking PFD) ,以避免dd-PFD(difference phase frequency detector)的非对称性问题,获得较少的死区值,更高的工作频率与更低的功耗。泵浦是基于差分对的全差分电路,以UP/DOWN和UPb/DOWNb来切换差分对,获得泵浦电流。电流源则始终处于通的状态,开关切换时造成的影响减至最小,避免了从泵浦关态到通态过长的恢复时间。缺点是增加了一定的功耗。

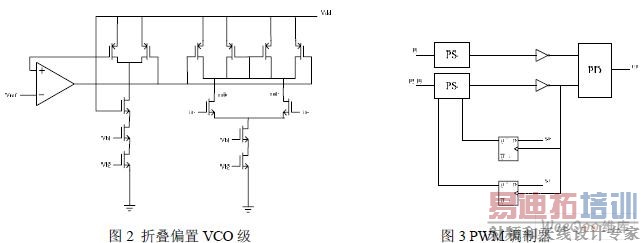

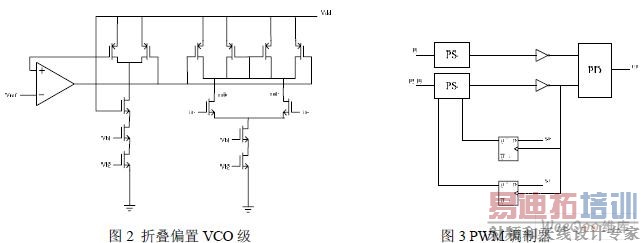

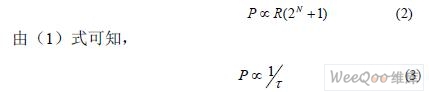

PLL的另一个关键模块是VCO,VCO设计的主要问题是噪声容限,它决定了PLL在一定的噪声环境下时钟抖动的大小。电路采用五相差分型环路振荡器,为PWM的调制解调提供五相信号。事实上,电路中存在很多噪声会引起时钟的抖动,其主要来源就是同一块基板上集成的大量电路所造成的电源噪声。为此,我们希望电路能有较大的PSSR(电源抑制比),我们采用图2所示折叠式电路,每一态都由nmos差分对及pmos对称负载构成。

VCO振荡器的频率取决于状态数S,及每一态的延时td,如下式所示:

式中td可以用下式表示:

式中Vsw为差分输出摆幅,CVsw/Iss为平均充放电时间。

显然,各状态的时间偏差与寄生电容上电压、电流源、输出波形幅度的波动相关。由于负反馈的作用,Vsw是固定的,这个值介于Vdd和Vref之间。保持Iss为常数,级联电流源输出电阻愈大,PSSR就愈高。对称pmos负载用二极管短接,产生关于输出电平中心对称的近于线性的I/V曲线。若电源由于噪声波动上升,Vsw与Iss同时上升,td可保持不变,即td可不受电源波动的影响。这有助于降低VCO对电源的敏感度,如图2所示,每一个状态的电流源以两个nmos管担任。VCO各相输出之后是DSE电路,将Vsw差分输出转换为轨对轨输出,其特点是不同Vref时都有50%的占空比输出。

2.2 PWM调制解调器

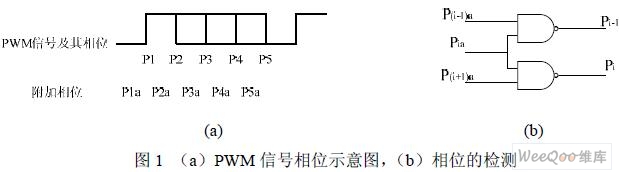

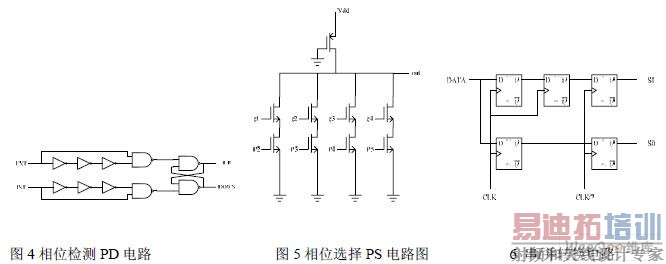

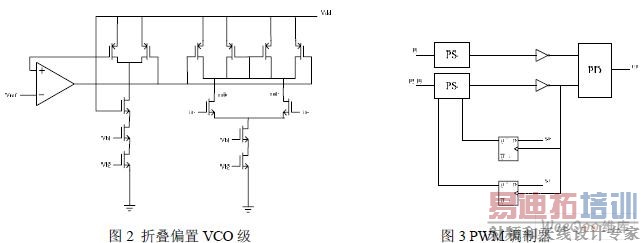

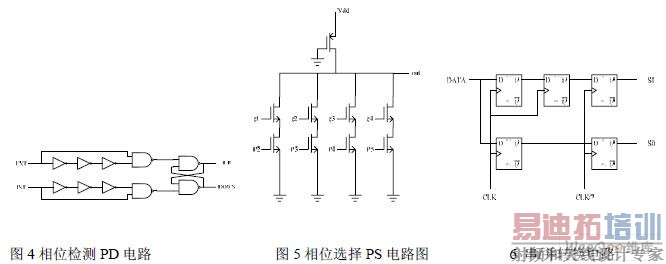

前面已知PWM调制器的输出仅仅包含四种宽度的信号,可采用数字方法产生PWM信号,PWM调制器如图3所示,两个主要的模块为相位检测(PD)和相位选择(PS)。此PWM调制器中,PD与一般的PLL中PD的作用类似,即输出一个与两个输入信号相位差成正比的脉宽信号。PD由一个确定的,四个不确定的相位触发,图中P1~P5, P1为置位相,P2~P5为四个可能复位相,通过串/并转换输出S0,S1来选择。为避免多次复位的发生,则采用图4所示的PD。图5则是PS原理图,为提高工作速度采用伪NMOS电路。

6 串/并转换电路

PWM解调电路如图3所示,接收PLL对接收的已调信号进行采样,产生相位采样信号。比较采样值就可以恢复出原来对应的数据(发送值)。由于采样信号来自于接收PLL,具有更加稳定的特点。

2.3 串/并,并/串转换

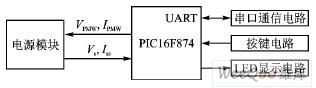

串/并转换的作用是将两个相邻的输入数据并化形成S0,S1两信号,用以进行调制控制,电路如图6所示。并/串转换是将解调后的信息串化恢复出数据,电路结构与串/并转换相似。

2.4 接口电路

为实现电路测试,考虑与1394a串行接口的连接,接口电路由漏极开路电流型晶体管,电平转换器,差分放大器构成。差分放大器为自偏压型,具有较宽共模输入范围且在电路高频工作时保证较低误码率。

3 实验结果

电路采用0.25 m DPTM工艺,除LPF,电路都集成在片上,发送单元,接收单元,及发送/接收PLL面积分别为:921×570 m2,723×448 m2,503×339 m2。PLL锁定在200MHZ时的输出,利用Tektronix CSA803A测量可得PLL输出峰-峰抖动为97ps,均方根为9.1ps。

发送电路以不同的四种数据输入产生四种不同的脉冲宽度,对应这些数据测得的脉冲占空比分别为19.5%, 39.0%, 61.3%, 78.6%,与理想值略有差异。我们保证数据流中有各种脉宽出现,使数据速率达到400Mbps时输出与输入相同。脉冲宽度与理想值的差异,可能是由于相位选择环路动态工作时的定时偏差所引起的,这一偏差愈大会使PWM解调器的采样范围减小,增加误码率。2.5V供电时功耗为79mW,说明该电路以简单较少的端口可以良好的工作在400Mbps速率上,对数据格式亦无特别限制,表1给出了电路的性能指标。

表1 电路的性能指标

4 结论

给出的一个基于PWM的高速数据接口电路,采用0.25 m标准CMOS工艺制造,以PLL构造电路,符号速率为200Mbps,数据速率为400Mbps,2.5V供电时接口电路功耗为79mW,适用于接口数目少且接口电路尽可能简单的系统,对实现片上IP核之间、乃至芯片之间的互连有积极的意义。

随着电路系统需求的扩展,集成电路设计与制造技术的进步,现代数字系统多工作在几百Mbps的速率上,这些高速系统常包含多个电路模块。系统中不同模块间的接口十分重要,它一般采用总线结构。为了获得更高的数据传输速率必须增加内部总线宽度,实际应用中,采用更大芯片面积和更多端口数目。这类问题也出现在板级系统中。为此,提出一个端口同时传输多个比特的概念以解决该问题,即采用调制技术,在电路中将数据与时钟信号合并为一个通道以减少端口数。为解调该信号,接收端则采用时钟恢复电路(CRC)从数据流中提取时钟信号。常用的调制技术包括PPM,PCM及PWM。

给出了一采用PWM,传输速率达400Mbps的数据接口电路。用脉冲宽度对数据进行编码,并保证含时钟周期上升沿,将时钟信号嵌入到编码后的数据中,这样在接收端很容易以传统的PLL恢复出时钟。可用PLLVC输出来解PWM编码信号,这样电路几乎就只需一个PLL。由于接收信号每个周期都有上升沿,避免了数据格式不同引起的电平与时间偏移。

2 基本原理与系统结构

PWM的脉宽值T与数据速率D可以分别表示为:

上式中N表示每符号的比特数,R表示符号率, 为单位脉宽。为简化电路设计,我们取N=2。PWM发送单元包括一串/并转换,PWM调制器,发送PLL,二分频器及接口电路。接收单元包括接口电路,PWM解调器,接收PLL,并/串转换。

每2bit的数据通过串/并转换合并对应为一个符号。00, 01, 10, 11四个不同符号分别对应不同的脉宽。每个符号对应2bit信息,因而采用二分频电路。CLK经二分频后作为PLL的参考时钟。PLL中的VCO能产生五种时钟相位供PWM调制器使用。PWM由VCO的第一个相位输出触发实现同步,由另外四个中的一个来复位,实现了上升沿触发同步,脉冲宽度编码的PWM发送电路。

接收电路与发送电路工作过程相反,接收到的PWM信号首先经过接口电路转化为全摆幅CMOS电平。然后一路送PLL,一路接收PWM,接收PLL与发送PLL相似,只是在各相输出后产生五个附加相,这五个附加相准确定位,用以检测PWM编码信号的下降沿,由图1可知只要确定了下降沿,符号就能被解码成2bit的信号,经并/串转换输出。

电路的功耗主要来源于PWM编、解码器及接收、发送PLL。若N增加,上升、下降过程的密度减少,发送与接收单元功耗也随之减少。发送与接收PLL的功耗由下式决定:

显然,这个功耗值与N并无直接关系。

3 电路设计

3.1 发送/接收PLL

PLL的性能在本接口电路中相当关键,若将PLL与低噪声的数字电路集成在同一块硅片上,抖动问题尤为重要。该电路采用的PLL是一个包含PFD,低通滤波器/泵浦,VCO在内的传统电流泵浦型PLL(CPPLL)。采用外接低通滤波器以减少片上面积,如前所述,发送、接收PLL只在VCO上有所不同。

为获得低抖动PLL,PFD的性能很重要,PFD的品质可由死区值(即不可检测的最小相位差)来衡量,传统的静态PFD用NAND来复位内部节点,延时大,死区值较大,导致了大的时钟抖动,从而限制了电路的最高工作频率。本文采用dec-PFD (double edge checking PFD) ,以避免dd-PFD(difference phase frequency detector)的非对称性问题,获得较少的死区值,更高的工作频率与更低的功耗。泵浦是基于差分对的全差分电路,以UP/DOWN和UPb/DOWNb来切换差分对,获得泵浦电流。电流源则始终处于通的状态,开关切换时造成的影响减至最小,避免了从泵浦关态到通态过长的恢复时间。缺点是增加了一定的功耗。

PLL的另一个关键模块是VCO,VCO设计的主要问题是噪声容限,它决定了PLL在一定的噪声环境下时钟抖动的大小。电路采用五相差分型环路振荡器,为PWM的调制解调提供五相信号。事实上,电路中存在很多噪声会引起时钟的抖动,其主要来源就是同一块基板上集成的大量电路所造成的电源噪声。为此,我们希望电路能有较大的PSSR(电源抑制比),我们采用图2所示折叠式电路,每一态都由nmos差分对及pmos对称负载构成。

VCO振荡器的频率取决于状态数S,及每一态的延时td,如下式所示:

式中td可以用下式表示:

式中Vsw为差分输出摆幅,CVsw/Iss为平均充放电时间。

显然,各状态的时间偏差与寄生电容上电压、电流源、输出波形幅度的波动相关。由于负反馈的作用,Vsw是固定的,这个值介于Vdd和Vref之间。保持Iss为常数,级联电流源输出电阻愈大,PSSR就愈高。对称pmos负载用二极管短接,产生关于输出电平中心对称的近于线性的I/V曲线。若电源由于噪声波动上升,Vsw与Iss同时上升,td可保持不变,即td可不受电源波动的影响。这有助于降低VCO对电源的敏感度,如图2所示,每一个状态的电流源以两个nmos管担任。VCO各相输出之后是DSE电路,将Vsw差分输出转换为轨对轨输出,其特点是不同Vref时都有50%的占空比输出。

2.2 PWM调制解调器

前面已知PWM调制器的输出仅仅包含四种宽度的信号,可采用数字方法产生PWM信号,PWM调制器如图3所示,两个主要的模块为相位检测(PD)和相位选择(PS)。此PWM调制器中,PD与一般的PLL中PD的作用类似,即输出一个与两个输入信号相位差成正比的脉宽信号。PD由一个确定的,四个不确定的相位触发,图中P1~P5, P1为置位相,P2~P5为四个可能复位相,通过串/并转换输出S0,S1来选择。为避免多次复位的发生,则采用图4所示的PD。图5则是PS原理图,为提高工作速度采用伪NMOS电路。

6 串/并转换电路

PWM解调电路如图3所示,接收PLL对接收的已调信号进行采样,产生相位采样信号。比较采样值就可以恢复出原来对应的数据(发送值)。由于采样信号来自于接收PLL,具有更加稳定的特点。

2.3 串/并,并/串转换

串/并转换的作用是将两个相邻的输入数据并化形成S0,S1两信号,用以进行调制控制,电路如图6所示。并/串转换是将解调后的信息串化恢复出数据,电路结构与串/并转换相似。

2.4 接口电路

为实现电路测试,考虑与1394a串行接口的连接,接口电路由漏极开路电流型晶体管,电平转换器,差分放大器构成。差分放大器为自偏压型,具有较宽共模输入范围且在电路高频工作时保证较低误码率。

3 实验结果

电路采用0.25 m DPTM工艺,除LPF,电路都集成在片上,发送单元,接收单元,及发送/接收PLL面积分别为:921×570 m2,723×448 m2,503×339 m2。PLL锁定在200MHZ时的输出,利用Tektronix CSA803A测量可得PLL输出峰-峰抖动为97ps,均方根为9.1ps。

发送电路以不同的四种数据输入产生四种不同的脉冲宽度,对应这些数据测得的脉冲占空比分别为19.5%, 39.0%, 61.3%, 78.6%,与理想值略有差异。我们保证数据流中有各种脉宽出现,使数据速率达到400Mbps时输出与输入相同。脉冲宽度与理想值的差异,可能是由于相位选择环路动态工作时的定时偏差所引起的,这一偏差愈大会使PWM解调器的采样范围减小,增加误码率。2.5V供电时功耗为79mW,说明该电路以简单较少的端口可以良好的工作在400Mbps速率上,对数据格式亦无特别限制,表1给出了电路的性能指标。

表1 电路的性能指标

4 结论

给出的一个基于PWM的高速数据接口电路,采用0.25 m标准CMOS工艺制造,以PLL构造电路,符号速率为200Mbps,数据速率为400Mbps,2.5V供电时接口电路功耗为79mW,适用于接口数目少且接口电路尽可能简单的系统,对实现片上IP核之间、乃至芯片之间的互连有积极的意义。

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

天线设计工程师培训课程套装,资深专家授课,让天线设计不再难...

上一篇:基于CAN总线的镍氢电池管理系统设计

下一篇:双晶体管正激有源钳位软开关电源的设计

射频和天线工程师培训课程详情>>