- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用低端栅极驱动器IC进行系统开发

录入:edatop.com 点击:

低端栅极驱动器IC是专用放大器,普遍用于电源设计中,根据来自PWM控制器的输入信号开关接地参考MOSFET和 IGBT。对于低于100~200W的低功率转换器,这些驱动器可以成功地集成到PWM控制器中以减少元件数,只要满足一定条件便没有问题。这些条件包括:MOSFET开关速度足够快,让开关损耗在可接受的范围内;较高驱动电流脉冲产生的噪声不会干扰控制功能;以及PWM IC的板上散热易于管理。另一方面,在较高功率的转换器中,一般采用单独的驱动器IC以提供更大的驱动功率或更方便地管理噪声和散热。此外,通过对控制器采用更低的电源电压,以及采用较高电压来驱动功率开关,可以提高电源效率,而栅极驱动器IC能够很好地完成这种电平转换工作。

为节约成本,有时也采用分立式元件来搭建简单的栅极驱动电路,在不需要具有先进功能及性能的驱动器IC时,这样做是可行的。不过,这种方案有不少局限性。例如,如果选定NPN/PNP射极跟随器的输出级,偏置电路的设计就必须谨慎,当晶体管的输出饱和电压高至快速开关电压时,会致使输出电压的摆幅减小。如果在输出端改用PMOS/NMOS反向器,控制逻辑必须适应这种逻辑转换,而且当驱动器改变状态时一般有部分击穿。利用上述两种技术的任一种,这种低增益级都需要输入快速边缘来产生快速的切换,需要更多的电路来执行电压级转换等功能,而元件数的增加对空间、装配时间及可靠性都有不良影响。

栅极驱动器IC 能够解决上述大部分问题。它们集成有使能和欠压锁定(UVLO)等功能,可以轻松地在启动、关断和发生故障等最棘手的工作条件下控制功率开关。很小的逻辑门就能够很容易地驱动高阻抗输入,而且由于驱动器IC包含有带正反馈的高增益电路,故只要输入电压超过阈值,输出总是能够快速切换。当IC需要设计以防止阈值电压随过热波动时,很容易通过在输入端添加简单的RC电路来插入一个固定延时。

驱动器大小的决定

使用低端驱动器的两类常见开关是具有硬开关拓扑的初级端开关特征的钳位感应开关,以及同步整流。决定驱动器大小的标准各不相同,这里做一个检阅。

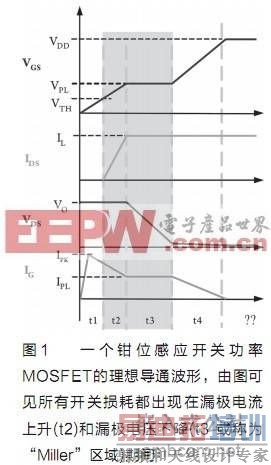

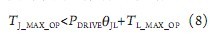

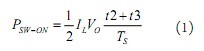

图1所示为钳位感应开关的理想导通波形,其特征是漏源电流的上升和漏源电压的下降之间没有重叠。这产生最差情况的开关损耗,通常表示为整个转换器开关时间TS上的平均功耗,即使实际功耗只发生在图中的t2和t3上。

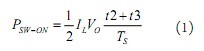

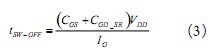

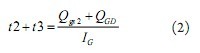

(t2+t3)的长度取决于平均栅极驱动电流IG和MOSFET栅极穿越这些时间间隔所必需的电荷量,两者都可以在 MOSFET规格中找到,或者是从总栅极电荷曲线上读取。

关断波形是图1的镜像图形,可以采用类似的方法计算关断开关损耗,并代入式(1),求出该功率开关的总开关损耗。从这些式子可明显看出,在损耗时间间隔内,开关损耗与栅极驱动电流成反比。对于钳位感应开关,开关损耗是决定栅极驱动器大小的主要指标。事实上,当它的输出电压接近工作范围中间值时,最重要的驱动器特性是其输出电流。

若把输出电压范围中间值下的稳态电流作为额定电流,则表1是个使用指南,显示了当驱动器路径上没有外接电阻时,单位大小的驱动器提供或消除一定数量的栅极电荷的速度。这个表是通过式(2)计算得出的,但考虑到实验室测试条件的非理想化,乘以了1.5的经验系数。然而,这个系数仍然过于保守,因为即使没有使用串联栅极电阻时,功率开关的内部栅极阻抗也会减慢开关的速度。当栅极驱动器与同步整流器(SR)一起使用时,大小标准又完全不同,由于体二极管在MOSFET沟道导通之前和之后都导通,故开关损耗可忽略不计。在此情况下,所需驱动器电流取决于时序和防止由于dv/dt而导通。

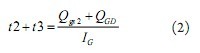

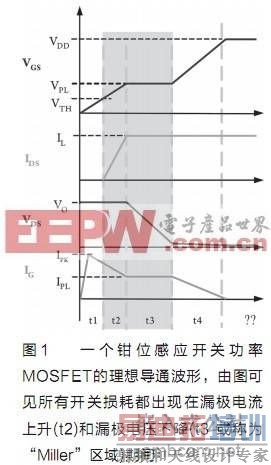

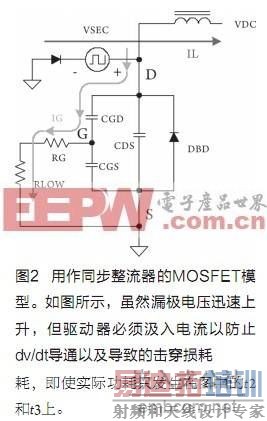

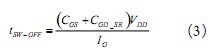

为了防止击穿导致不必要的功耗,必须在加载电压之前完全关断SR,一般通过导通一个或多个初级开关来实现。为了确保此条件得到满足,同时让SR尽可能长地保持导通状态,以最大限度提高效率,必须知道需要多长时间来关断SR。由图2中的MOSFET模型,可计算出关断时间。

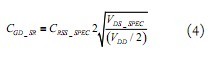

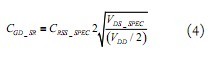

这里, CGS=CISS-CRSS是MOSFET的线性栅源电容,CGD_SR是低压非线性栅漏电容或“密勒”电容CGD=CRSS。后者的选择最好对应SR关断期间电压摆幅的中间值,VDD/2。这个值可从CRSS与电压的关系曲线(若提供)读取,也可以根据使用手册给出的对应某些更高电压VDS_SPEC的CRSS_SPEC值按照下式求出:

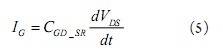

一旦SR完全被关断,功率转换器中的主要开关可导通,致使SR的漏源电压急速上升。图2显示了这种情况,由CGD和CGS构成的电容性分压器导致内部漏电压增加―MOSFET短暂时反向导通―除非驱动器吸入足够多的电流使内部栅极节点保持在MOSFET的阈值电压之下。这常常是决定SR驱动器大小的主要标准。在漏电压刚开始上升时,CGD最大,所需吸入电流近似为:

如果一个较大的驱动器不能使用,而且它已经紧靠SR放置,避免因dv/dt导通的最终手段是通过减慢主要开关的导通速度来减小dv/dt,但这同时也增加了主要开关的开关损耗。

功能选择

在选择驱动器IC时,除了额定电流之外,设计人员还面临着功能选择的问题,也就是输入逻辑及配置、输入阈值和封装的选择。对于单沟道驱动器,输入形式包括反向、非反向、双输入和使能输入等选项。要正确设置每一个MOSFET栅极控制信号的极性,通常需要在反向和非反向之间进行选择,由单个控制输出驱动时,不同开关有时选择不同。如果两种极性都需要,则双输入驱动器需要的不同元件更少,由于具有一个反向输入,一个非反向输入,故其可按二者中任一种方式配置。若MOSFET开关时需要额外的控制,比如设置更高的UVLO阈值或启动期间禁用SR一秒,使能输入很有用。

驱动器可以带有TTL 或 CMOS输入电平。TTL“低”输入定义为0.8V以下,“高”输入定义为2.0V以上,与电源无关,故TTL阈值近似恒定,总是保持在这两个上下限之间。相反地,CMOS输入阈值大约是电源电压的40% 和 60%。TTL阈值更常见,在输入信号(比如来自低压PWM控制器)幅度较低时尤其有用。不过,CMOS具有更好的噪声容限,故是嘈杂环境的首选。而且利用CMOS可以更精确地设置RC延时,因为其阈值更接近电源电压的一半。当需要精确时序时,输入阈值和传播延迟的温度稳定性也很重要。

补偿元件

在利用驱动器IC进行设计时,有两个补偿元件十分重要:旁路电容和串联栅极电阻。由于驱动器产生短电流脉冲,故需要阻抗极低的电源来提供最大电流,这通常是通过紧邻驱动器放置一对旁路电容来实现,而驱动器本身也应该尽可能靠近功率开关放置以尽量减小这一电流回路的漏电感(stray inductance)。这种较大的电容一般是电解电容器或另一种ESR值较低的电容器,其电容值是有效负载电容的2~10倍,可利用总栅极电荷通过下式求得:

其次,陶瓷旁路电容一般是该值的十分之一。当采用相同的电压源对灵敏的控制电路进行供电时,良好的习惯是:在供电线路上串联数欧姆的电阻,把驱动器部分和控制部分隔离开来。

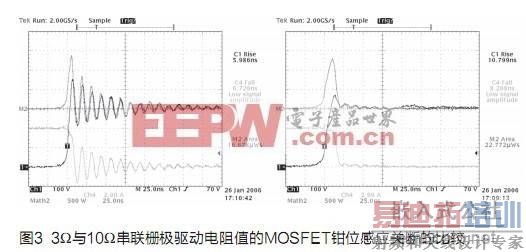

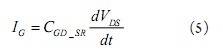

在驱动同步整流器时,驱动器和功率开关之间的串联栅极电阻往往被忽略,但在实际中常常使用2到20欧姆的这样一个电阻,原因有三:第一,可抑制功率开关栅极电容和栅极驱动回路漏电感之间的振铃电流,如图3所示,因为过多的振铃电流会增加EMI,并因快速切换开关而增加损耗。其次,可减慢开关速度,从而降低EMI,不过会导致更高的开关损耗。第三个可能的原因是,使用一个串联栅极驱动电阻可以把驱动器的栅极驱动损耗部分转移到该外接电阻上,而总的栅极驱动损耗保持不变。

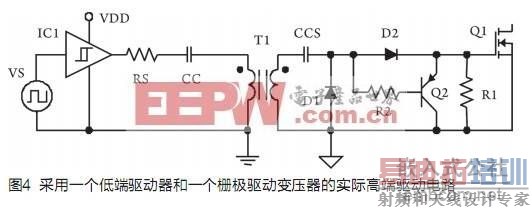

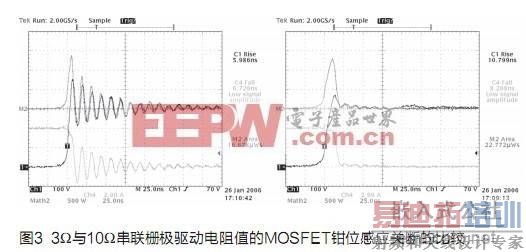

对于具有控制良好的输入阈值的驱动器IC,可以利用串联电阻外加驱动器输入端的小接地电容,在控制路径上插入固定延时。如图4所示,在增加栅极驱动变压器和若干其它元件之后,低端驱动器还可以用于驱动高端(浮动)开关,作为高压驱动器IC的一种替代方案。这么做的主要原因是,越过隔离边界,缩短传播延迟,实现更稳健的驱动电路。

热设计

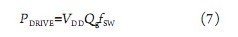

由于驱动器IC的功耗相当显著,故应该关注热设计问题。这是一个两步过程:首先估算驱动器的功耗,然后计算结温,确保其在设计限制范围内。对于这里讨论的简单栅极驱动电路(控制驱动和非谐振),与功率MOSFET或IGBT每周期开/关有关的总栅极驱动损耗可从开关的资料表给出的总栅极电荷曲线求得,即读取对应所选栅极驱动电压VDD的总栅极电荷Qg,然后按下式计算:

这一功耗与串联栅极驱动电阻的值无关,但会影响与驱动电路的其它串联电阻相比驱动器IC所消耗的功率。事实上,驱动器IC功耗所占比例正好是它的有效输出阻抗与驱动回路中所有阻抗总和之比,该值在导通和关断时不同。要进行计算,估算驱动器的有效输出阻抗的最简单方法是:电源电压的一半除以稳态源或二分之一电源电压下的输出钳位吸入电流。其它应该计入内的回路电阻还有开关的外部和内部串联栅极电阻,大容量旁路电容的ESR。因为这些电阻中有部分无法精确获知,按照(7)求得的总栅极驱动功耗可以作为驱动器IC功耗的上限,或者计算值可以使用部分经验值。

一旦确定了驱动器IC的功耗,资料表提供的无论何种热参数都应用来估算最大结温。结环热阻θJA 是最常用的参数,但很遗憾它只在某些指定热设计中很精确,比如PCB构建、散热和气流。在无顶部散热器的低气流中,大部分功耗集聚在PCB中。这时,如果结到引脚或结到电路板的热阻给定,且若设计限制了PCB的最大工作温度,假设引脚温度等于最大板温,则可求出工作结温的上限:

若结温过高,重新选择改进估算,提供更冷却或选择阻抗更低的驱动器。驱动器供应商要获得更好的结果(以及资料表提供的某些热参数),对封装和热环境进行有限元分析是一种好方法。

参考文献:

[1] Balogh L. Design and Application Guide for High Speed MOSFET Gate Drive Circuits. Power Supply Design Seminar SEM-1400, Topic 2, Texas Instruments Literature No. SLUP169

作者:飞兆半导体公司功率模拟设计部Van Niemela

为节约成本,有时也采用分立式元件来搭建简单的栅极驱动电路,在不需要具有先进功能及性能的驱动器IC时,这样做是可行的。不过,这种方案有不少局限性。例如,如果选定NPN/PNP射极跟随器的输出级,偏置电路的设计就必须谨慎,当晶体管的输出饱和电压高至快速开关电压时,会致使输出电压的摆幅减小。如果在输出端改用PMOS/NMOS反向器,控制逻辑必须适应这种逻辑转换,而且当驱动器改变状态时一般有部分击穿。利用上述两种技术的任一种,这种低增益级都需要输入快速边缘来产生快速的切换,需要更多的电路来执行电压级转换等功能,而元件数的增加对空间、装配时间及可靠性都有不良影响。

栅极驱动器IC 能够解决上述大部分问题。它们集成有使能和欠压锁定(UVLO)等功能,可以轻松地在启动、关断和发生故障等最棘手的工作条件下控制功率开关。很小的逻辑门就能够很容易地驱动高阻抗输入,而且由于驱动器IC包含有带正反馈的高增益电路,故只要输入电压超过阈值,输出总是能够快速切换。当IC需要设计以防止阈值电压随过热波动时,很容易通过在输入端添加简单的RC电路来插入一个固定延时。

驱动器大小的决定

使用低端驱动器的两类常见开关是具有硬开关拓扑的初级端开关特征的钳位感应开关,以及同步整流。决定驱动器大小的标准各不相同,这里做一个检阅。

图1所示为钳位感应开关的理想导通波形,其特征是漏源电流的上升和漏源电压的下降之间没有重叠。这产生最差情况的开关损耗,通常表示为整个转换器开关时间TS上的平均功耗,即使实际功耗只发生在图中的t2和t3上。

(t2+t3)的长度取决于平均栅极驱动电流IG和MOSFET栅极穿越这些时间间隔所必需的电荷量,两者都可以在 MOSFET规格中找到,或者是从总栅极电荷曲线上读取。

关断波形是图1的镜像图形,可以采用类似的方法计算关断开关损耗,并代入式(1),求出该功率开关的总开关损耗。从这些式子可明显看出,在损耗时间间隔内,开关损耗与栅极驱动电流成反比。对于钳位感应开关,开关损耗是决定栅极驱动器大小的主要指标。事实上,当它的输出电压接近工作范围中间值时,最重要的驱动器特性是其输出电流。

若把输出电压范围中间值下的稳态电流作为额定电流,则表1是个使用指南,显示了当驱动器路径上没有外接电阻时,单位大小的驱动器提供或消除一定数量的栅极电荷的速度。这个表是通过式(2)计算得出的,但考虑到实验室测试条件的非理想化,乘以了1.5的经验系数。然而,这个系数仍然过于保守,因为即使没有使用串联栅极电阻时,功率开关的内部栅极阻抗也会减慢开关的速度。当栅极驱动器与同步整流器(SR)一起使用时,大小标准又完全不同,由于体二极管在MOSFET沟道导通之前和之后都导通,故开关损耗可忽略不计。在此情况下,所需驱动器电流取决于时序和防止由于dv/dt而导通。

为了防止击穿导致不必要的功耗,必须在加载电压之前完全关断SR,一般通过导通一个或多个初级开关来实现。为了确保此条件得到满足,同时让SR尽可能长地保持导通状态,以最大限度提高效率,必须知道需要多长时间来关断SR。由图2中的MOSFET模型,可计算出关断时间。

这里, CGS=CISS-CRSS是MOSFET的线性栅源电容,CGD_SR是低压非线性栅漏电容或“密勒”电容CGD=CRSS。后者的选择最好对应SR关断期间电压摆幅的中间值,VDD/2。这个值可从CRSS与电压的关系曲线(若提供)读取,也可以根据使用手册给出的对应某些更高电压VDS_SPEC的CRSS_SPEC值按照下式求出:

一旦SR完全被关断,功率转换器中的主要开关可导通,致使SR的漏源电压急速上升。图2显示了这种情况,由CGD和CGS构成的电容性分压器导致内部漏电压增加―MOSFET短暂时反向导通―除非驱动器吸入足够多的电流使内部栅极节点保持在MOSFET的阈值电压之下。这常常是决定SR驱动器大小的主要标准。在漏电压刚开始上升时,CGD最大,所需吸入电流近似为:

如果一个较大的驱动器不能使用,而且它已经紧靠SR放置,避免因dv/dt导通的最终手段是通过减慢主要开关的导通速度来减小dv/dt,但这同时也增加了主要开关的开关损耗。

功能选择

在选择驱动器IC时,除了额定电流之外,设计人员还面临着功能选择的问题,也就是输入逻辑及配置、输入阈值和封装的选择。对于单沟道驱动器,输入形式包括反向、非反向、双输入和使能输入等选项。要正确设置每一个MOSFET栅极控制信号的极性,通常需要在反向和非反向之间进行选择,由单个控制输出驱动时,不同开关有时选择不同。如果两种极性都需要,则双输入驱动器需要的不同元件更少,由于具有一个反向输入,一个非反向输入,故其可按二者中任一种方式配置。若MOSFET开关时需要额外的控制,比如设置更高的UVLO阈值或启动期间禁用SR一秒,使能输入很有用。

驱动器可以带有TTL 或 CMOS输入电平。TTL“低”输入定义为0.8V以下,“高”输入定义为2.0V以上,与电源无关,故TTL阈值近似恒定,总是保持在这两个上下限之间。相反地,CMOS输入阈值大约是电源电压的40% 和 60%。TTL阈值更常见,在输入信号(比如来自低压PWM控制器)幅度较低时尤其有用。不过,CMOS具有更好的噪声容限,故是嘈杂环境的首选。而且利用CMOS可以更精确地设置RC延时,因为其阈值更接近电源电压的一半。当需要精确时序时,输入阈值和传播延迟的温度稳定性也很重要。

补偿元件

在利用驱动器IC进行设计时,有两个补偿元件十分重要:旁路电容和串联栅极电阻。由于驱动器产生短电流脉冲,故需要阻抗极低的电源来提供最大电流,这通常是通过紧邻驱动器放置一对旁路电容来实现,而驱动器本身也应该尽可能靠近功率开关放置以尽量减小这一电流回路的漏电感(stray inductance)。这种较大的电容一般是电解电容器或另一种ESR值较低的电容器,其电容值是有效负载电容的2~10倍,可利用总栅极电荷通过下式求得:

其次,陶瓷旁路电容一般是该值的十分之一。当采用相同的电压源对灵敏的控制电路进行供电时,良好的习惯是:在供电线路上串联数欧姆的电阻,把驱动器部分和控制部分隔离开来。

在驱动同步整流器时,驱动器和功率开关之间的串联栅极电阻往往被忽略,但在实际中常常使用2到20欧姆的这样一个电阻,原因有三:第一,可抑制功率开关栅极电容和栅极驱动回路漏电感之间的振铃电流,如图3所示,因为过多的振铃电流会增加EMI,并因快速切换开关而增加损耗。其次,可减慢开关速度,从而降低EMI,不过会导致更高的开关损耗。第三个可能的原因是,使用一个串联栅极驱动电阻可以把驱动器的栅极驱动损耗部分转移到该外接电阻上,而总的栅极驱动损耗保持不变。

对于具有控制良好的输入阈值的驱动器IC,可以利用串联电阻外加驱动器输入端的小接地电容,在控制路径上插入固定延时。如图4所示,在增加栅极驱动变压器和若干其它元件之后,低端驱动器还可以用于驱动高端(浮动)开关,作为高压驱动器IC的一种替代方案。这么做的主要原因是,越过隔离边界,缩短传播延迟,实现更稳健的驱动电路。

热设计

由于驱动器IC的功耗相当显著,故应该关注热设计问题。这是一个两步过程:首先估算驱动器的功耗,然后计算结温,确保其在设计限制范围内。对于这里讨论的简单栅极驱动电路(控制驱动和非谐振),与功率MOSFET或IGBT每周期开/关有关的总栅极驱动损耗可从开关的资料表给出的总栅极电荷曲线求得,即读取对应所选栅极驱动电压VDD的总栅极电荷Qg,然后按下式计算:

这一功耗与串联栅极驱动电阻的值无关,但会影响与驱动电路的其它串联电阻相比驱动器IC所消耗的功率。事实上,驱动器IC功耗所占比例正好是它的有效输出阻抗与驱动回路中所有阻抗总和之比,该值在导通和关断时不同。要进行计算,估算驱动器的有效输出阻抗的最简单方法是:电源电压的一半除以稳态源或二分之一电源电压下的输出钳位吸入电流。其它应该计入内的回路电阻还有开关的外部和内部串联栅极电阻,大容量旁路电容的ESR。因为这些电阻中有部分无法精确获知,按照(7)求得的总栅极驱动功耗可以作为驱动器IC功耗的上限,或者计算值可以使用部分经验值。

一旦确定了驱动器IC的功耗,资料表提供的无论何种热参数都应用来估算最大结温。结环热阻θJA 是最常用的参数,但很遗憾它只在某些指定热设计中很精确,比如PCB构建、散热和气流。在无顶部散热器的低气流中,大部分功耗集聚在PCB中。这时,如果结到引脚或结到电路板的热阻给定,且若设计限制了PCB的最大工作温度,假设引脚温度等于最大板温,则可求出工作结温的上限:

若结温过高,重新选择改进估算,提供更冷却或选择阻抗更低的驱动器。驱动器供应商要获得更好的结果(以及资料表提供的某些热参数),对封装和热环境进行有限元分析是一种好方法。

参考文献:

[1] Balogh L. Design and Application Guide for High Speed MOSFET Gate Drive Circuits. Power Supply Design Seminar SEM-1400, Topic 2, Texas Instruments Literature No. SLUP169

作者:飞兆半导体公司功率模拟设计部Van Niemela

射频工程师养成培训教程套装,助您快速成为一名优秀射频工程师...

射频和天线工程师培训课程详情>>